前记:师夷长技以自强

一、基本概念

FIFO:利用FPGA的片上存储器设计的一个先进先出缓冲器。可以分为单时钟FIFO和双时钟FIFO,前者用于高速传感器数据的缓存,后者用于异步数据的收发(数据的发送端和接收端分别使用不同的时钟域)。

FIFO参数:

宽度:FIFO一次读写数据的位数。

深度:存储数据的个数。

满标志:FIFO已满或将要满时发出的一个标志信号。

空标志:FIFO已空或将要空时发出的一个状态标志。

读时钟:读操作遵循的时钟,每个上升沿若读请求为高时则读数据。

写时钟:写操作遵循的时钟,每个上升沿若写请求为高时则写数据。

二、使用方法

从理论上说所有的IP电路都可以自己实现,但一般项目中都是使用现成的IP,幸运的时Quartus II为我们提供了现成的FIFO IP核,并有简洁的图形化页面。

1.Tools->MegaWizard Plug-In Manager

2.Create a new custom megafunction variation next

3.

搜索fifo找到FIFO模块后,再输入文件名,next.

4.

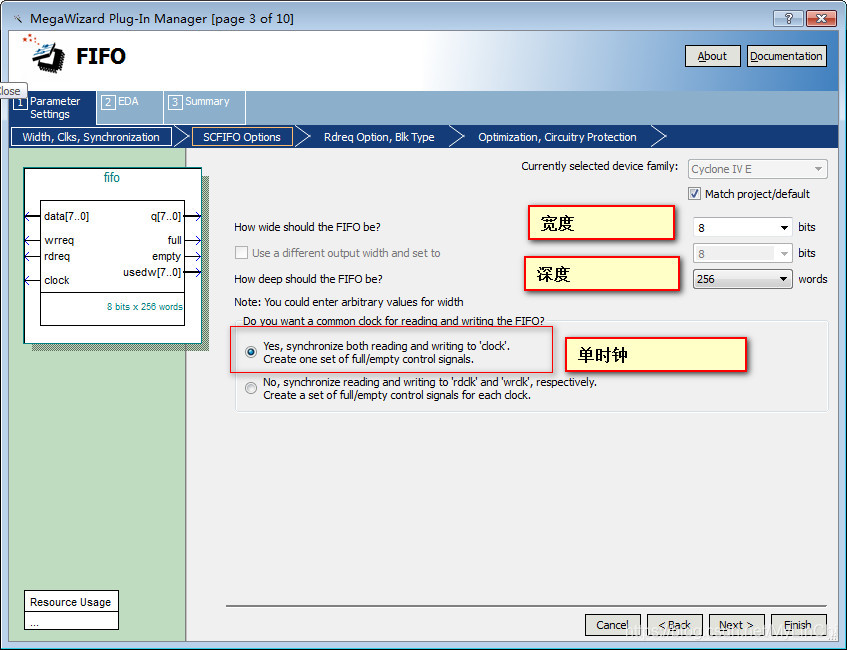

这一步可以设置是单时钟FIFO还是双时钟FIFO,并设置FIFO的宽度和深度。

5.

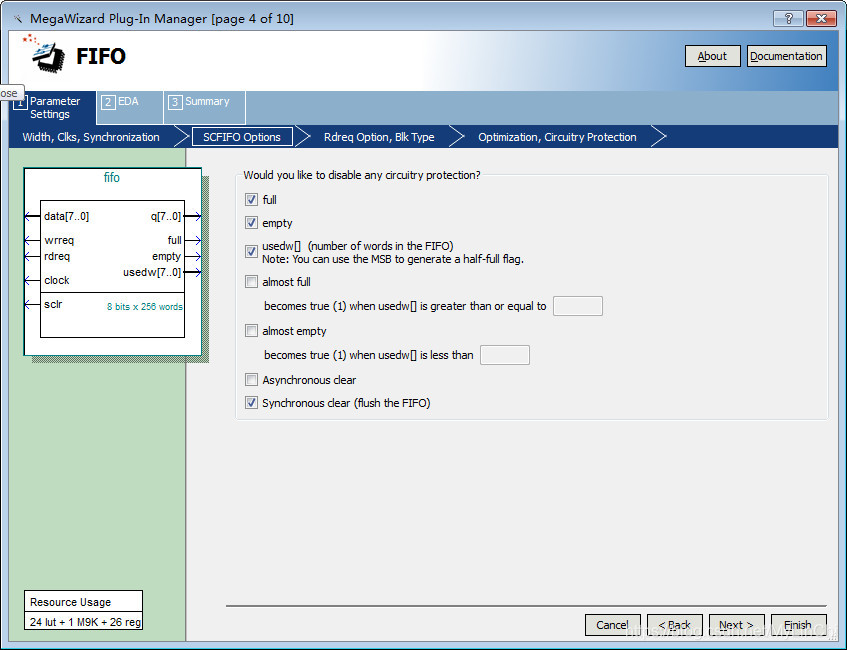

选择FIFO的引脚,这里只选了一些最基础的引脚,next。

6.

rdreq可以设置为普通模式或者前显模式,一般选前者,next.

7.

可以选择速度优化或者面积优化,保留前者即可。

三、测试

上面已经把FIFO模块添加到程序中了,要使用的话只需打开fifo.v文件即可看到模块的具体管脚。本人为了测试一下这个模块的功能,先后对这个模块进行了写入和读出。

`timescale 1ns/1ns

module fifo_tb();

reg clock;

reg [15:0] data;

reg rdreq;

reg sclr;

reg wrreq;

wire almost_empty;

wire almost_full;

wire empty;

wire full;

wire [15:0] q;reg [10:0]i;

fifo fifo1(

.clock(clock),

.data(data),

.rdreq(rdreq),

.sclr(sclr),

.wrreq(wrreq),

.almost_empty(almost_empty),

.almost_full(almost_full),

.empty(empty),

.full(full),

.q(q)

);

initial clock = 0;

always #10 clock = ~clock;

initial begin

wrreq = 0;

data = 0;

rdreq = 0;

sclr = 0;

#401;

for(i=0;i<=2000;i=i+1)begin

wrreq = 1;

data = i;

#20;

end

#400;

for(i=0;i<=2000;i=i+1)begin

rdreq = 1;

#20;

end

rdreq = 0;

$stop;

endendmodule

可以得到如下的仿真波形

8509

8509

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?