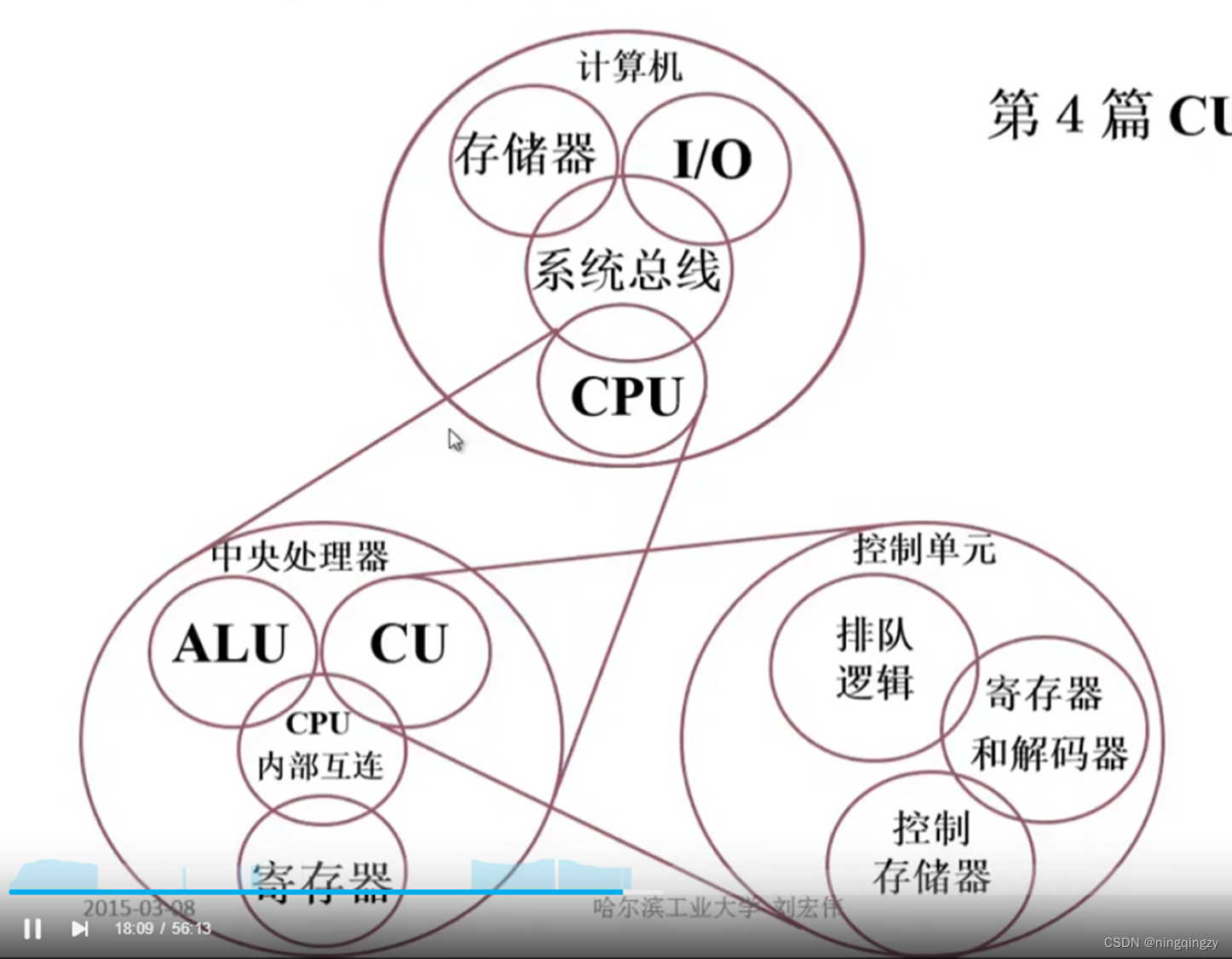

框图

第一章 总线

1、什么是总线?

总线是连接各个部件的信息传输线,是各个部件共享的传输介质。

2、总线特点?

相对于一对一的连线来说,可拓展性更好,也更省空间,但是某个时刻只能有一对部件进行通信。

3、总线传输方式?

串行和并行。并行一次可以传输N个信号,效率高,但是距离长会导致数据丢失,因此适合内部传输;串行一次只能传输一个信号,特点正好相反,适合部件之间传输。

4、总线分类?

- 片内总线:芯片内部的总线

- 系统总线:计算机各部件之间的信息传输线

- 通信总线:计算机之间或计算机与其它系统之间的通信

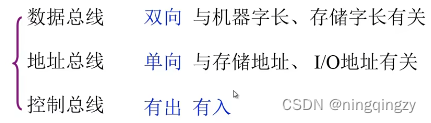

系统总线分为三类:

5、总线传输周期?

- 申请分配阶段:主模块申请,总线仲裁决定

- 寻址阶段:主模块向从模块 给出地址 和 命令

- 传数阶段:主模块和从模块 交换数据

- 结束阶段:主模块 撤消有关信息

6、总线通信方式?

- 同步通信:由统一时标 控制数据传送

- 异步通信:采用应答方式,没有公共时钟标准

- 半同步通信:同步、异步结合

- 分离式通信:充分挖掘系统总线每个瞬间的潜力

第二章 数据的表示和运算

第三章 存储系统

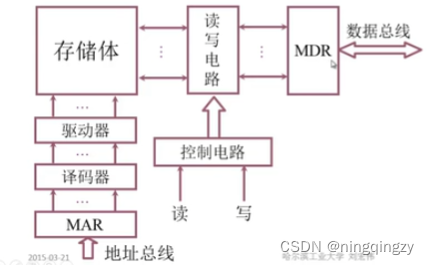

1、主存的基本组成?

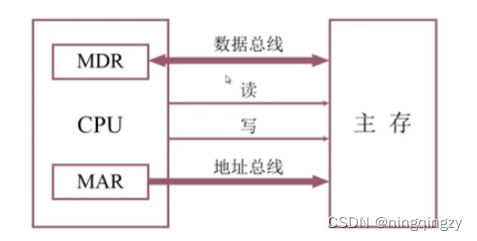

2、主存与CPU的联系?

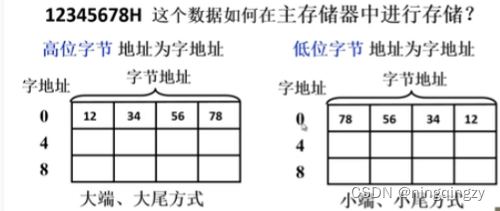

3、主存中存储单元地址的分配?

大端存储:低位字节存储在高位地址,高位字节存储在低位地址;

小端存储:高位字节存储在高位地址,低位字节存储在低位地址。

x86机器采用的是小端、小尾方式

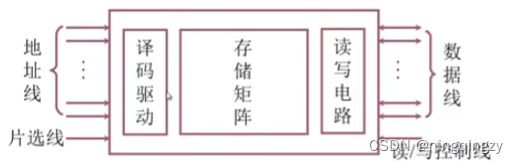

4、半导体存储芯片简介?

地址线:单向 数据线:双向

假设地址线有n条,数据线m条,则芯片容量为*2^n m 位

片选线两种标识方式:CS和CE,CS(芯片选择信号)低电平表示有效,CE(芯片使能信号)

读写控制线,可以一条,可能有两条。若两条:WE和OE,WE(允许写),OE(允许读);若一条:WE(低电平写,高电平读)

5、随机存取存储器?

1、静态RAM(SRAM)

最基本SRAM由T1~T4,4个触发器和T5\T6行开关共六个晶体管组成

2、动态RAM(DRAM)

基本单元主要由一个晶体管和一个电容组成,电容中有电荷代表“1”,没有电荷代表“0”。 由于电容中的电荷会随着时间而慢慢泄露,所以需要周期性地进行“充电”,这也是“Dynamic”的由来。

6、只读存储器?

- 掩模 ROM (MROM):只可读

- PROM (一次性编程)

- EPROM (多次性编程)

- EEPROM (多次性编程)

- Flash Memory (闪速型存储器)

7、主存储器与CPU的连接?

首先对单个存储芯片进行字、位拓展,再进行:

- 地址线的连接

- 数据线的连接

- 读/写命令线的连接

- 片选线的连接

- 合理选择存储芯片

- 其他时序、负载

详细可以参考博文:主存储器与CPU的连接详解

高速缓冲存储器

1、为什么要用Cache?——避免CPU空等现象

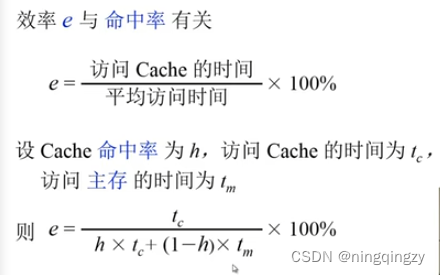

2、主存系统的效率?

IO设备

1、IO指令?

操作码+命令码+设备码

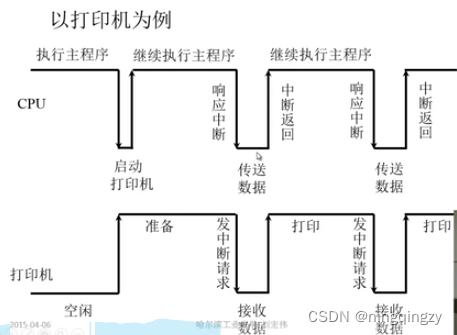

2、IO中断的产生?

4003

4003

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?