目录

例1 用D触发器设计一个8421 BCD码同步十进制加计数器。编辑

例3;用D 触发器设计状态变化满足下状态图的时序逻辑电路编辑

同步时序逻辑电路的设计是分析的逆过程,其任务是根据实际逻辑问题的要求,设计出能实现给定逻辑功能的电路。

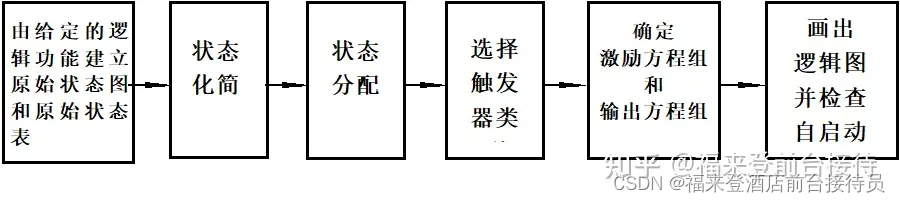

6.3.1 设计同步时序逻辑电路的一般步骤

同步时序电路的设计过程

(1)根据给定的逻辑功能建立原始状态图和原始状态表

①明确电路的输入条件和相应的输出要求,分别确定输入变量和输出变量的数目和符号。

②找出所有可能的状态和状态转换之间的关系。

③根据原始状态图建立原始状态表。

(2)状态化简-----求出最简状态图 ;

合并等价状态,消去多余状态的过程称为状态化简

等价状态:在相同的输入下有相同的输出,并转换到同一个次态去的两个状态称为等价状态。

(3)状态编码(状态分配);

给每个状态赋以二进制代码的过程。

根据状态数确定触发器的个数, 2�−1 <M≤ 2� M:状态数;n:触发器的个数)

(4)选择触发器的类型

(5)求出电路的激励方程和输出方程 ;

(6)画出逻辑图并检查自启动能力。

2 同步时序逻辑电路设计举例

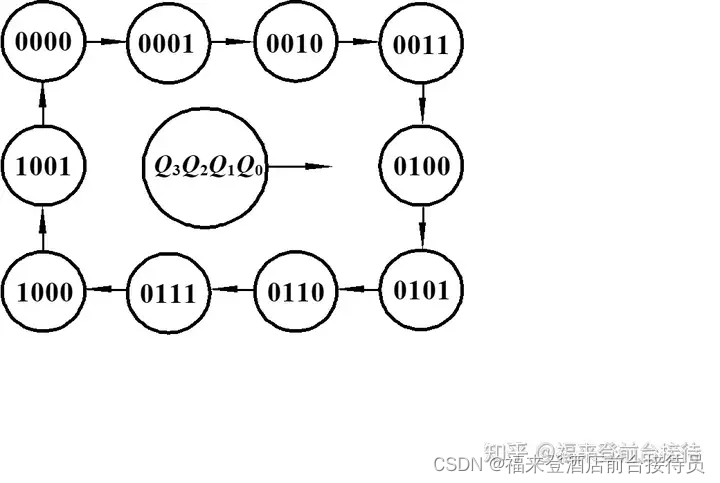

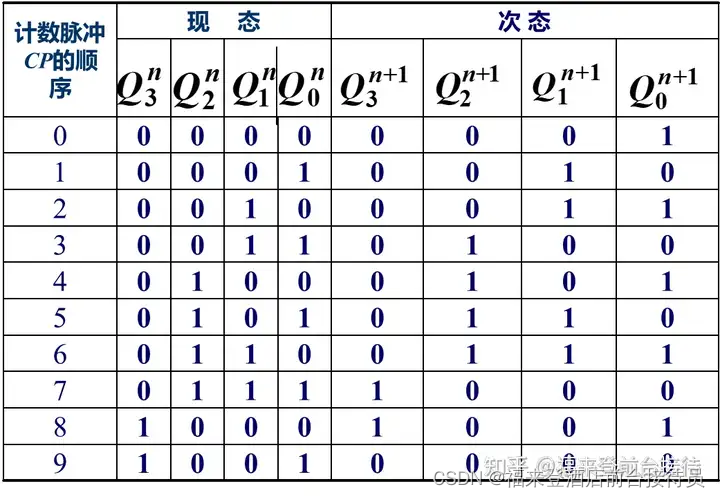

例1 用D触发器设计一个8421 BCD码同步十进制加计数器。

(1)8421码同步十进制加计数器的状态表

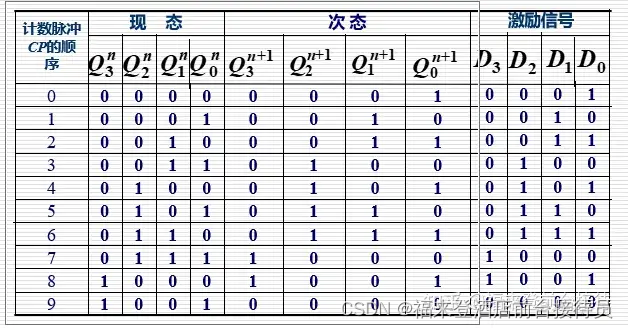

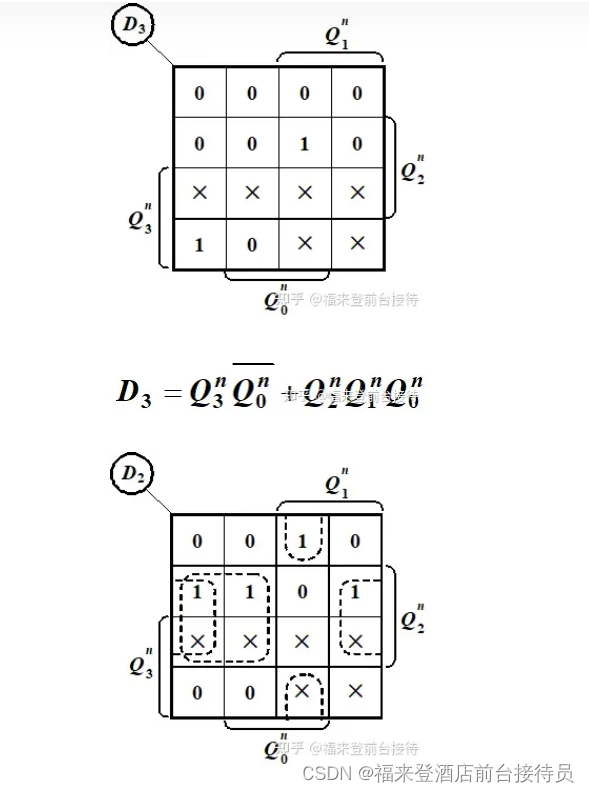

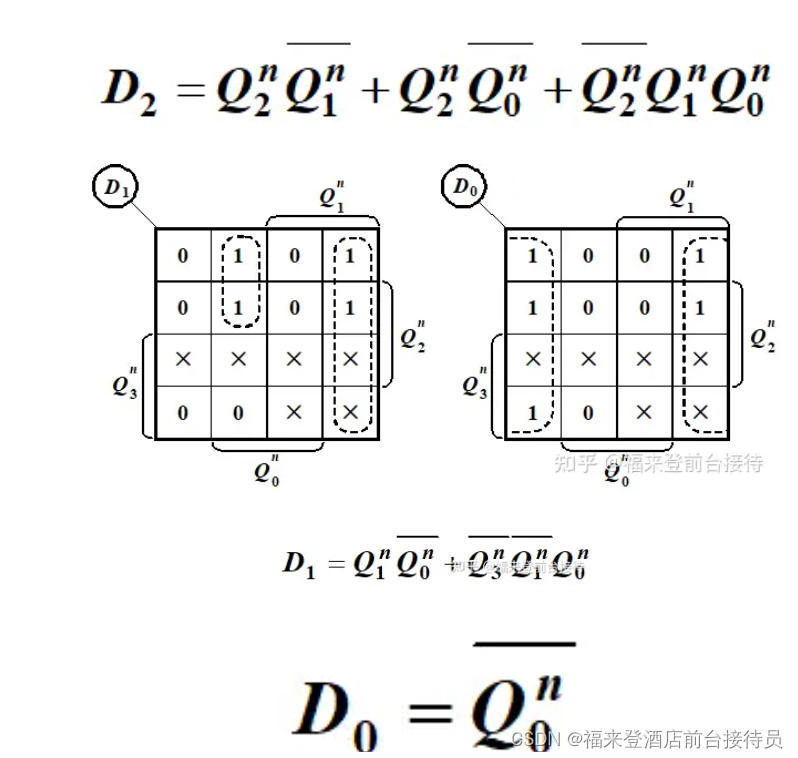

(2) 确定激励方程组

D3、 D2、 D1、 D0、是触发器初态还是次态的函数?D3、 D2、 D1、 D0是触发器初态的函数

画出各触发器激励信号的卡诺图

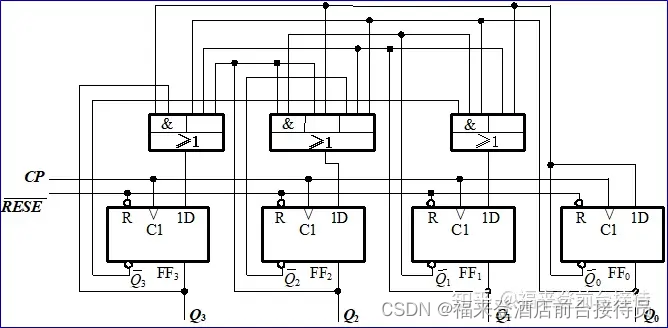

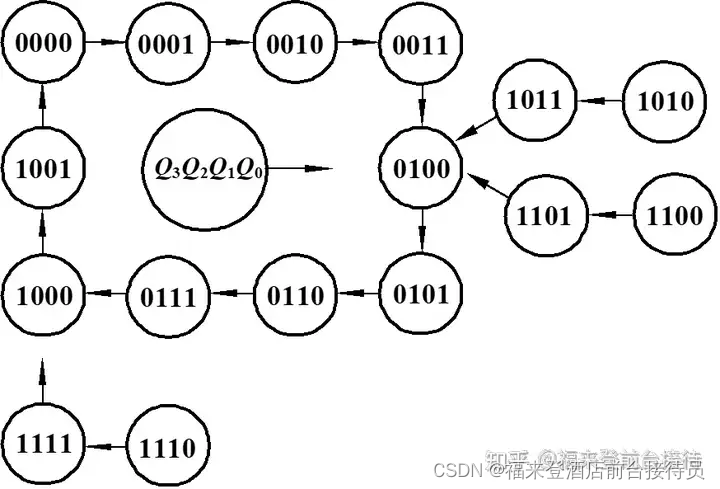

(3) 画出逻辑图,并检查自启动能力

画出完全状态图

电路具有自启动能力

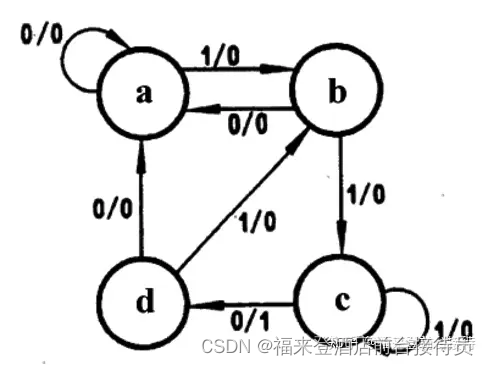

例二 用JK触发器设计一个序列检测器

设计一个串行数据检测器。电路的输入信号X是与时钟脉冲同步的串行数据,其时序关系如下图所示。输出信号为Z;要求电路在X信号输入出现110序列时,输出信号Z为1,否则为0。

解: 根据给定的逻辑功能建立原始状态图和原始状态表

1.)确定输入、输出变量及电路的状态数:

输入变量:A 输出变量:Z 状态数:4个

2.)定义输入 输出逻辑状态和每个电路状态的含义;

a —— 初始状态;b—— A输入1后;c —— A输入11后;d —— A输入110后。

1:建立状态图

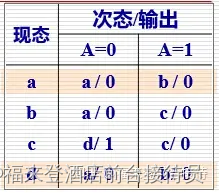

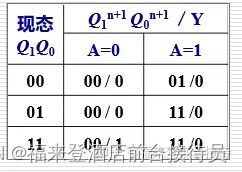

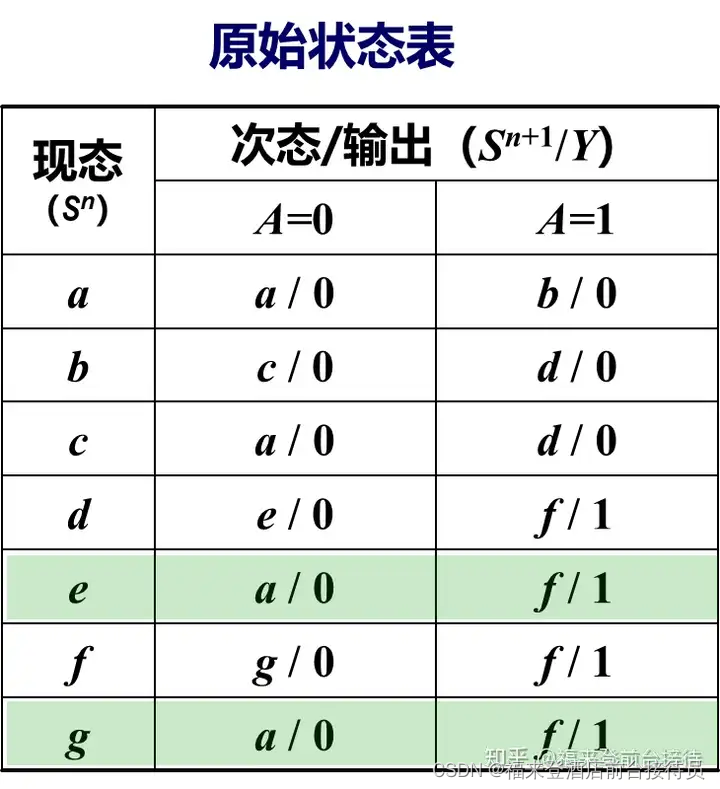

2.列出原始状态转换表并化简

状态化简

3、状态分配

令 a = 00,b = 01,c = 11,

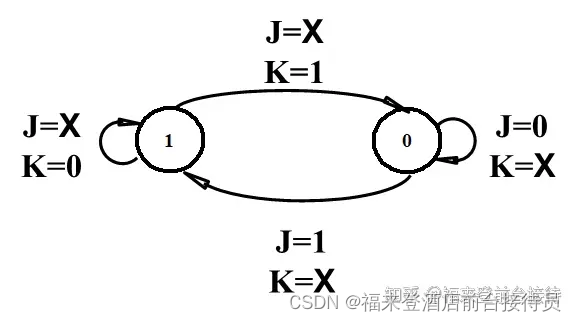

4、选择触发器的类型

触发器个数: 两个。

类型:采用对 CP 下降沿敏感的JK 触发器。

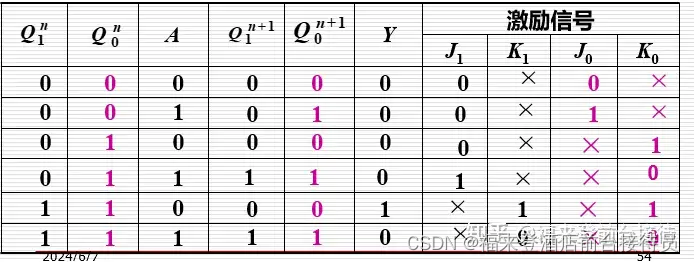

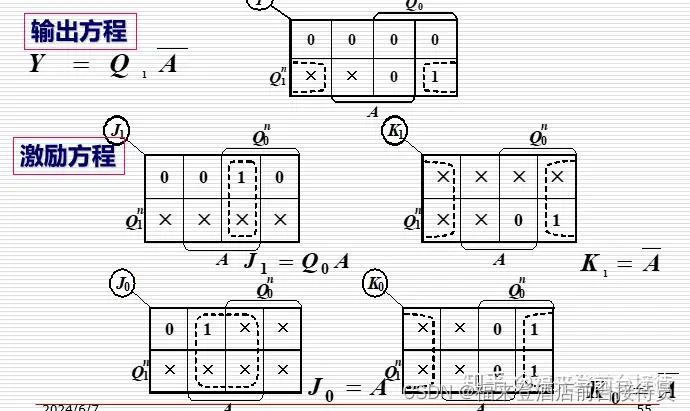

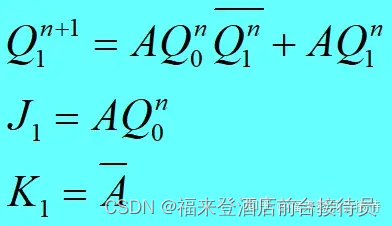

5. 求激励方程和输出方程

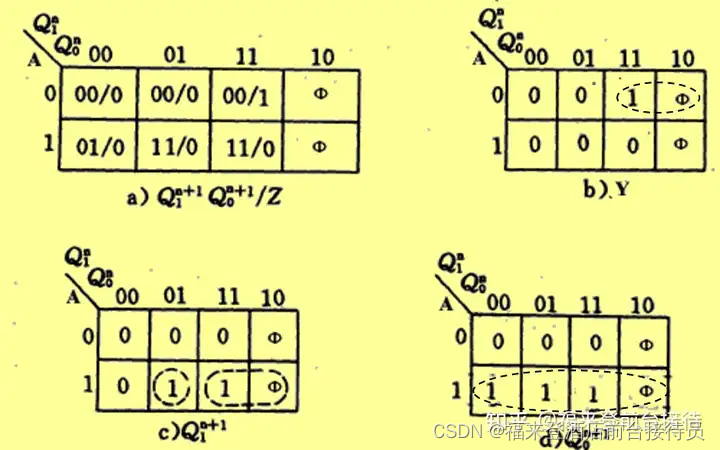

状态转换真值表及激励信号

卡诺图化简得

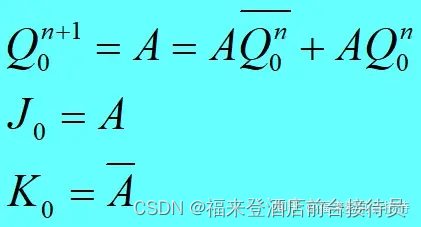

利用特性方程求解 比照JK的特性方程 求得:

比照JK的特性方程 求得:

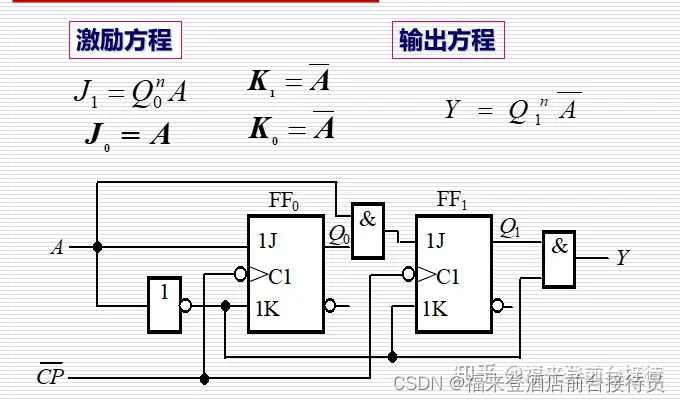

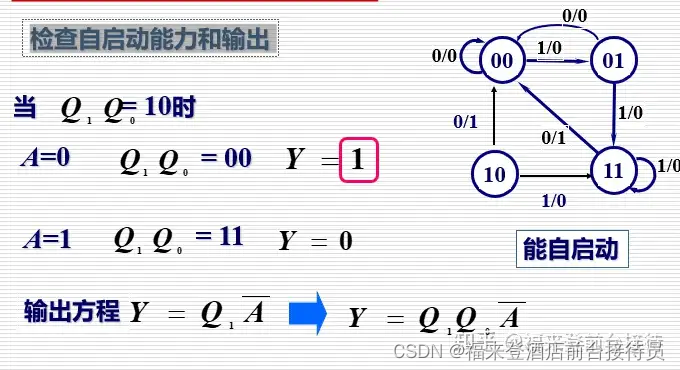

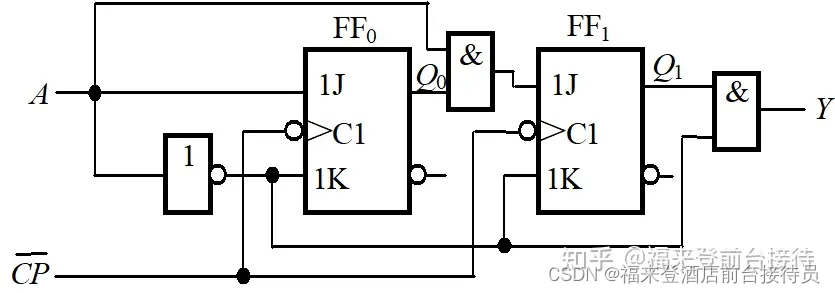

6. 根据激励方程和输出方程画出逻辑图,并检查自启动能力

检查自启动能力和输出

修改电路

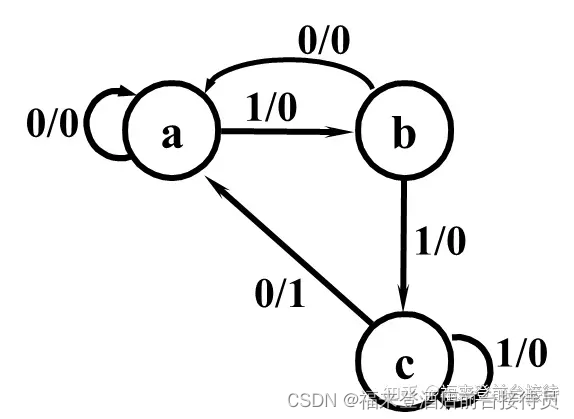

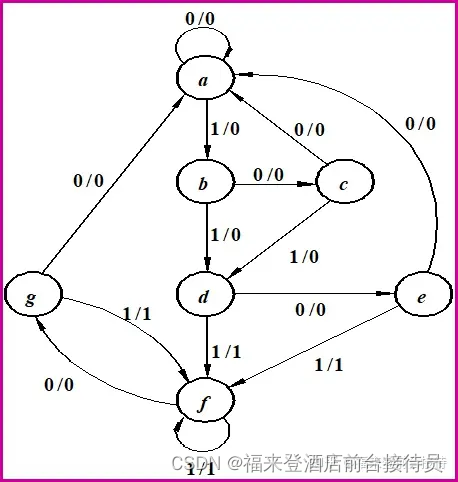

例3;用D 触发器设计状态变化满足下状态图的时序逻辑电路

1、列出原始状态表

2、状态表化简

2、状态编码

a=000;b=001;c=010 ;d=011;e=100

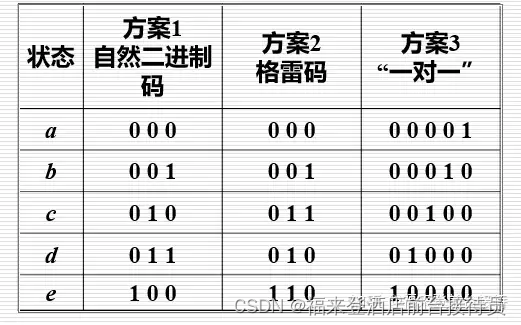

三种状态分配方案

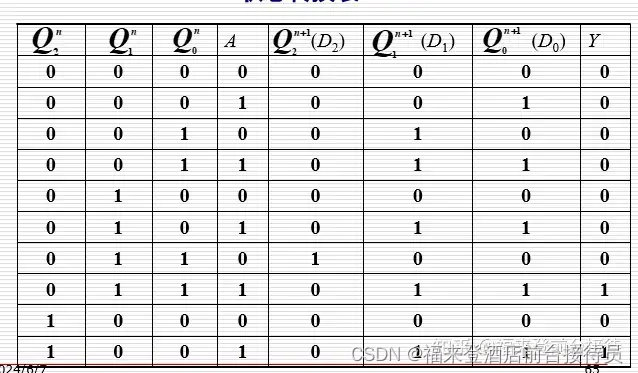

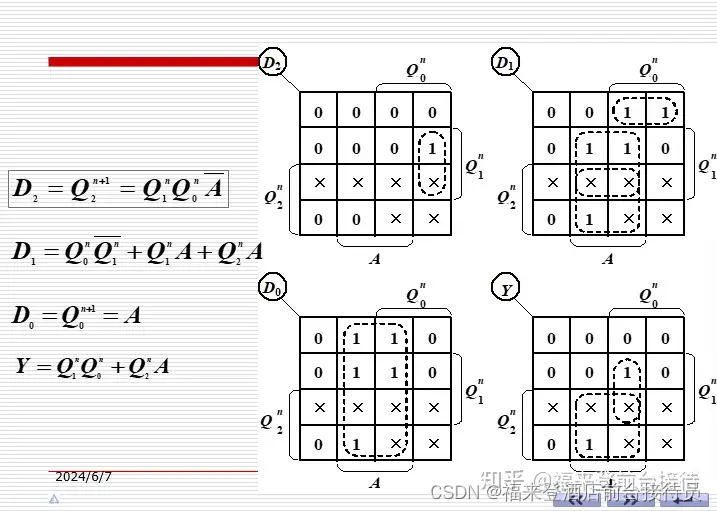

3、求激励方程、输出方程

画出逻辑电路

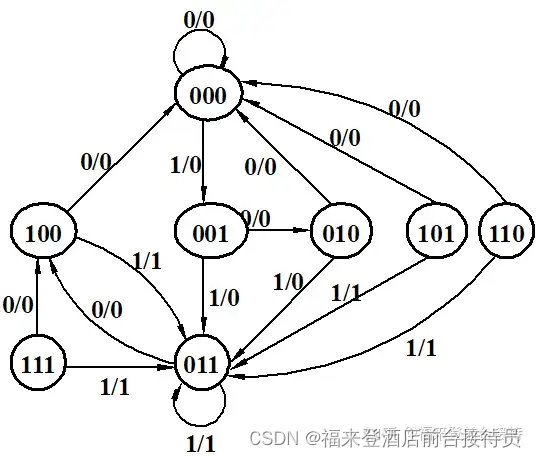

画出完整的状态图,检查所设计的计数器能否自启动.

资料仅供学习使用

如有错误欢迎留言交流

上理考研周导师的其他专栏:

上理考研周导师了解更多

5194

5194

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?