GPIO引脚分配

ZC706评估板的PS部分有54个引脚,分成Bank0,Bank1两组;PL部分有64个引脚,分成Bank2,Bank3两组。GPIO外设通过MIO提供PS部分54个引脚,并且还可以通过EMIO将PL部分的64个引脚以及其他硬件模块调用给PS部分使用。

Bank0:32-bit bank controlling MIO pins[31:0]

Bank1:22-bit bank controlling MIO pins[53:32]

Bank2:32-bit bank controlling MIO pins[31:0]

Bank3:32-bit bank controlling MIO pins[63:32]

GPIO寄存器

Bank0,Bank1与Bank2,Bank3寄存器结构不同,其中最大的区别在于

输入输出寄存器

1.DATA_RO寄存器

寄存器中反应引脚的实时状态

如果没有配置其GPIO引脚,其寄存器内的值不可预测

2.DATA寄存器

GPIO配置为输出时将要输出的状态写入该寄存器

读该寄存器会得到最近写入之前的寄存器状态(不是实时的状态)

3.MASK_DATA_LSW寄存器

低16位掩码寄存器,不想写的位置1,想写的位置0。

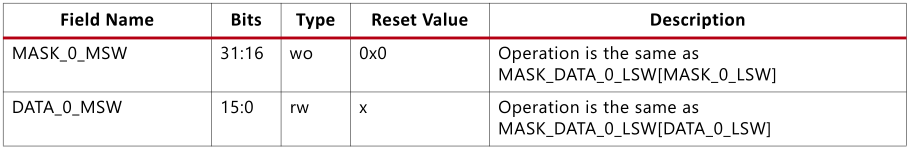

4.MASK_DATA_MSW寄存器

高16位掩码寄存器,不想写的位置1,想写的位置0。

5.DIRM寄存器

IO方向寄存器,输入模式置0,输出模式置1。

6.OEN寄存器

输出使能寄存器,置0不使能,置1使能。

输出模式下,只有DIRM寄存器与OEN寄存器均为1才能正常工作在输出模式

疑问及解决:

ARM寄存器一般高版本均应为32bit寄存器,为什么MSK寄存器一个GPIO的Bank分两个?

查看ug585手册附录B的寄存器详细版本可知,DATA寄存器与MASK寄存器是和在一起的,例如针对Bank0来说,对DATA和MASK实际管控的寄存器是:MSK_DATA_0_LSW与MSK_DATA_0_MSW两个寄存器(即DATA寄存器对于1个Bank来说也分低16bit与高16bit)

选自ug585.APPX.B

MIO与EMIO区别

MIO是PS主要调用的IO口来源(即Bank0,Bank1),EMIO来自于FPGA部分的引脚作为对PS引脚的补充使用(即Bank2,Bank3)。其中MIO的使用主要是配置以上的所有寄存器即可实现所需要的IO引脚功能,而EMIO则是引入由PS端控制的三根线(EMIOGPIOI,EMIOGPIOO,EMIOGPIOTN)作为输入,想要PS操作的FPGA上的GPIO引脚做为输出,其中的逻辑关系可以通过FPGA做硬件上的更改(因此EMIO的使用在某种程度上反而更加灵活)

EMIO结构示意图

对应的在硬件上实际会引出三个接口

4474

4474

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?