GIC V2(gic400)

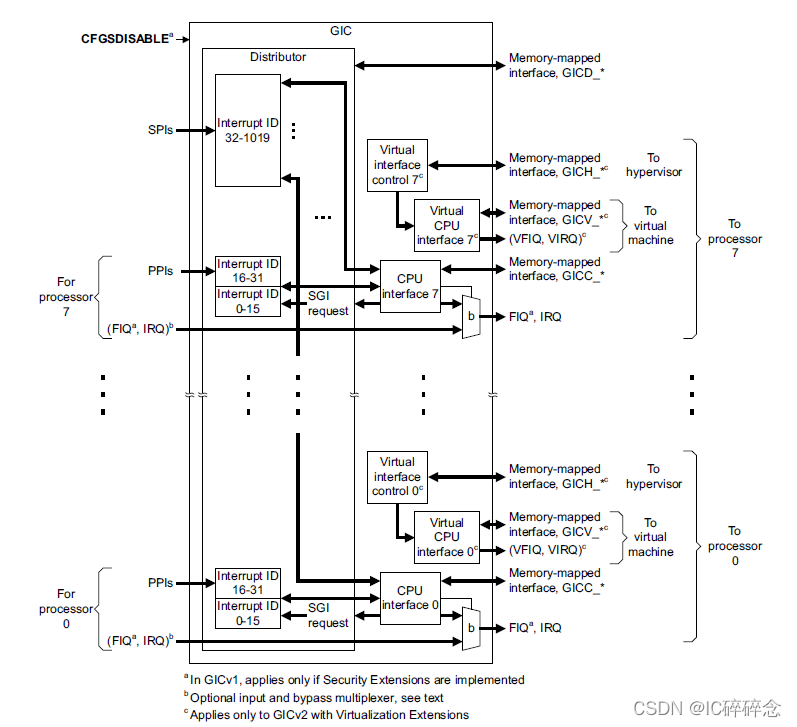

GIC400,支持最大8个core,在gicv2中,gic由两个大模块组成:distributor 和 cpu interface

distributor:实现中断分发,对于PPI,SGI是各个core独有的中断,不参与目的core的仲裁,SPI,是所有core共享的,根据配置决定中断发往的core。最后选择最高优先级中断发送给cpu interface。寄存器使用 GICD_ 作为前缀。一个GIC中,只有一个GICD_*。当一个中断事件分发到多个CPU interface(最多8个)的时候,GIC的内部逻辑应该保证只assert 一个CPU。

Distributor:用来收集所有的中断来源,并且为每个中断源设置中断优先级,中断分组,中断目的core。

提供以下功能 地址0x1000 — 0x1FFF

-

全局中断使能

[GICD_CTRL] 0x000

-

每个中断的使能

GICD_ENABLE_CLEAR

-

中断的优先级

GIC-400 最大支持256级优先级

如果两个或多个中断具有相同的优先级,则仲裁取决于类型中断:由中断ID号来确定,SGI<PPI<SPI。中断号越小,优先级越高

写入中断优先级寄存器 GICD_IPRIORITYR 不会影响活动中断的优先级。

-

[中断的分组]

coer 0 irq or fiq (secure)

core 1 only irq (unsecure)

-

中断的目的core

Interrupt Processor Targets Registers, GICD_ITARGETSRn

-

中断触发方式

level-sensitive还是edge-triggered

-

每个中断的状态管理

-

提供软件,可以修改中断的状态

Cpu interface:将GICD发送的中断信息,通过IRQ,FIQ管脚,传输给core。寄存器使用 GICC_ 作为前缀。每一个core,有一个cpu interface。0x2000—0x3FFF

每个 CPU 接口向相应的处理器发出中断信号并接收确认和来自该处理器的 EOI(end of interrupt) 访问。这些 AXI 访问传达中断 ID 和其他有关中断的信息,还会触发对distribution服务器状态的更新。

CPU 接口为其连接的处理器获取最高优先级的挂起中断,确定中断是否具有足够的优先级以向处理器发出中断请求信号。到判断是否向处理器发出中断请求信号,CPU接口考虑中断优先级掩码和处理器的抢占设置。

At any time, the connected processor can read the priority of its highest priority active interrupt from its GICC_HPPIR, (CPU interface register)

提供以下功能

- 启用向处理器发出中断请求的信号

- [中断进行认可](acknowledging an interrupt)

- [中断完成应答]

- 设置中断优先级屏蔽

- 定义中断抢占策略

- 决定当前处于pending状态最高优先级中断

◾virtual cpu interface:将GICD发送的虚拟中断信息,通过VIRQ,VFIQ管脚,传输给core(需要CPU支持虚拟化)。每一个core,有一个virtual cpu interface。而在这virtual cpu interface中,又包含以下两个组件:

◾virtual interface control:寄存器使用 GICH_ 作为前缀

◾virtual cpu interface:寄存器使用 GICV_ 作为前缀

GICv2支持by pass mode,也就是gic外部的FIQ,IRQ直接接到core的FIQ,IRQ上,相当于gic是不使能的。也就是CFGSDISABLE是有效的,将GIC给无效掉.

gicv2,定义了自己的一些寄存器,这些寄存器,都是使用memory-mapped的方式去访问的,也就是在soc中,会留有一片空间给gic。CPU通过访问这部分空间,来对gic进行操作。

寄存器,分为以下:

◾GICD_*: distributor的寄存器

◾GICC_*: cpu interface的寄存器

◾GICH_*: 虚拟interface的控制寄存器

◾GICV_*:虚拟CPU的控制寄存器

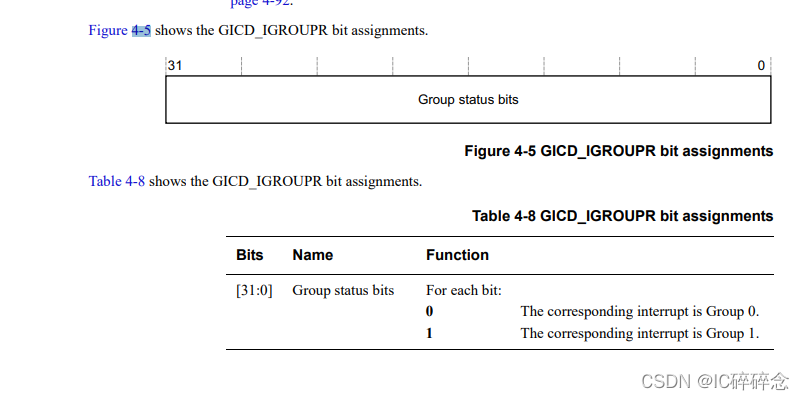

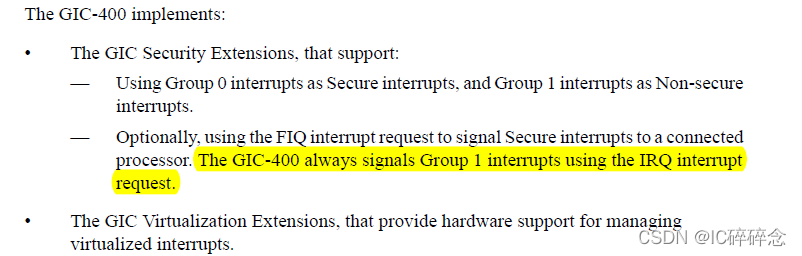

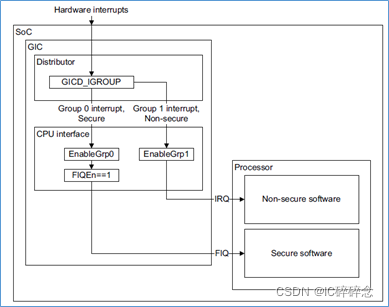

中断分组

givc2,将中断,分成了group0和group1。使用寄存器GICD_IGROUPRn来对每个中断,设置组。

◾group0:安全中断,由nFIQ或nirq驱动

◾group1:非安全中断,由nIRQ驱动

默认情况下,所有中断都是组 0 中断,并使用 IRQ 向连接的处理器发送信号中断请求

CPU 接口可以配置为使用 FIQ 向连接的处理器发送组 0 中断信号中断请求。

group0 或者group1都可以分别被disable,但是可能存在再group1的中断优先级大于group0,但是group1 is disable,group0 is enable,这时候如果产生一个中断在group1中,那么distribution将不会发送任何中断给cpu interface。所以需要建议总要保持高优先级的中断组是enable的,并且一个group中的中断优先级应该都大于或小于另外一个组。

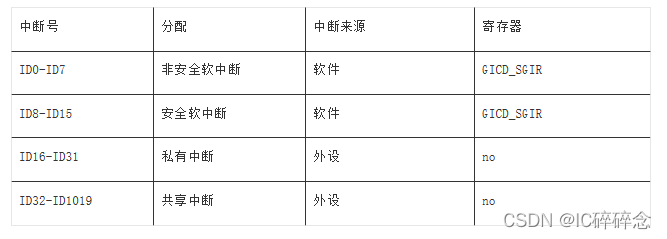

中断号

!](https://img-blog.csdnimg.cn/e6c0604c12a645a9bade055d06fc818b.png?x-oss-process=image/watermark,type_d3F5LXplbmhlaQ,shadow_50,text_Q1NETiBASUPnoo7noo7lv7U=,size_20,color_FFFFFF,t_70,g_se,x_16)

gic,支持最大1020个中断。其中断号分配如下:gicv2支持480个

中断active 读中断ID

中断认可,是指cpu响应该中断。此时中断状态从pending状态,变为active状态。通过访问GICC_IAR(read only)寄存器,来对中断进行认可。中断一旦被应答,Distributor就会把该中断的状态从pending状态修改成active或者pending and active(这是和该interrupt source的信号有关,例如如果是电平中断并且保持了该asserted电平,那么就是pending and active)。processor ack了中断之后,CPU interface就会deassert nIRQCPU和nFIQCPU信号线。

◾GICC_EOIR(0x0010):End of Interrupt,只写,中断处理完成后需要写该寄存器

◾GICC_IAR(0x000C):Interrupt Acknowledge,只读,可以查看当前pending的最高优先级中断

◾GICC_IAR: 认可group0的中断

◾GICC_AIAR: 认可group1的中断

中断完成

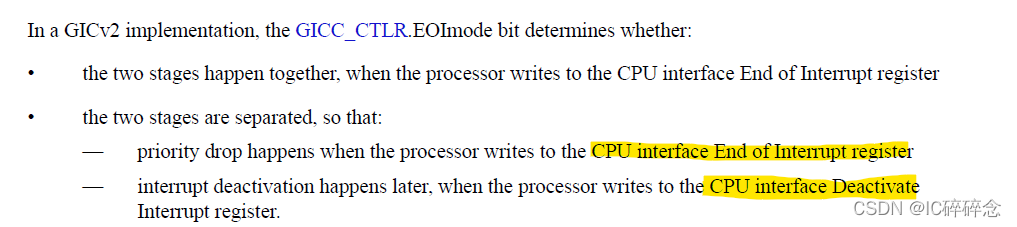

中断完成,是指cpu处理完中断。此时中断状态从active状态,变为[inactive]状态。当interrupt handler处理完了一个中断的时候,会向写CPU interface的寄存器(GICC_EOIR(0x0010))从而通知GIC CPU已经处理完该中断。做这个动作一方面是通知Distributor将中断状态修改为deactive,另外一方面,CPU interface会priority drop,从而允许其他的pending的interrupt向CPU提交gic中,对中断完成,定义了以下两个stage:

◾优先级重置(priority drop):将当前中断mask的最高优先级进行重置,以便能够响应低优先级中断。group0中断,通过写GICC_EOIR寄存器,来实现优先级重置,group1中断,通过写 GICC_AEOIR 寄存器,来实现优先级重置。

◾中断无效(interrupt deactivation):将中断的状态,设置为inactive状态。通过写 GICC_DIR 寄存器,来实现中断无效。

对于中断来说,我们是希望中断处理程序越短越好,但是有些中断处理程序,就是比较长,在这种情况下,就会影响其他中断得到相应,从而影响实时性。比如当前cpu在响应优先级为4的中断A,但是这个中断A的中断处理程序比较长,此时如果有优先级为5的中断B到来,那么cpu是不会响应这个中断的。

在软件上,会将中断处理程序分为两部分,分为上半部分,和下半部分。在上半部分,完成中断最紧急的任务,然后就可以通知GIC,降低当前的中断处理优先级,以便其他中断能够得到响应。在下半部分,处理该中断的其他事情。在这种机制下,低优先级的中断,不用等待高优先级的中断,完全执行完中断处理程序后,就可以被cpu所响应,提高实时性。

为了实现上述机制,就将中断完成分成了2步。还是刚刚的例子,cpu在响应优先级为4的中断A,当中断A的上半部分完成后,通知GIC,优先级重置(drop priority),GIC将当前的最高优先级中断重置,重置到响应中断A之前的优先级,比如优先级6,那么此时优先级为5的中断B,就可以被cpu响应。最后中断A的下半部分完成后,通知GIC,将该中断A的状态,设置为inactive状态,此时中断A就真正的完成了。

当然,也可以不将中断完成分成2步,就1步。通过控制 GICC_CTLR寄存器的EOImode比特,来决定是否将中断完成分成2步。

中断处理流程

中断处理流程,包含了以下几步:

- GIC决定每个中断的使能状态,不使能的中断,是不能发送中断的

- 如果某个中断的中断源有效,GIC将该中断的状态设置为pending状态,然后判断该中断的目标core

- 对于每一个core,GIC将当前处于pending状态的优先级最高的中断,发送给该core的cpu interface

- cpu interface接收GIC发送的中断请求,判断优先级是否满足要求,如果满足,就将中断通过nFIQ或nIRQ管脚,发送给core。

- core响应该中断,通过读取 GICC_IAR 寄存器,来active此中断。读取该寄存器,如果是软中断,返回源处理器ID,否则返回中断号。当core认可该中断后,GIC将该中断的状态,修改为active or active and pending状态

- 当core完成该中断后,通过写 EOIR (end of interrupt register)来实现优先级重置,写 GICC_DIR 寄存器,来无效该中断

中断enable or disable

通过设置GICD_ISENABLERn寄存器,来使中断使能,通过设置GICD_ICENABLERn寄存器,来使中断禁止。

这两个寄存器,都是bit有效的寄存器,一个bit,关联一个中断。

中断pending

通过设置GICD_ISPENDRn或GICD_ICPENDRn寄存器,可以读取和修改中断的pending状态。这两个寄存器,也是bit有效的寄存器,一个bit,关联一个中断。

中断active

通过设置GICD_ISACTIVERn或GICD_ICACTIVERn寄存器,可以读取和修改中断的active状态。这两个寄存器,也是bit有效的寄存器,一个bit,关联一个中断

产生软中断

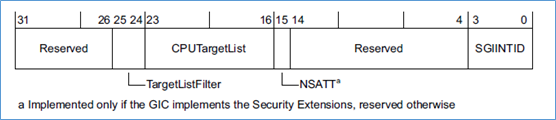

通过写 GICD_SGIR 寄存器,来产生软中断。软中断,可以指定产生中断,发往执行的core,也可以发送多个core。

对于软中断,是软件产生的中断。比如软件,想给执行自己的core,发送一个中断,就可以通过软中断来产生。或者软件,想起其他的core,发送一个中断,也可以通过软中断来产生。

寄存器如下:

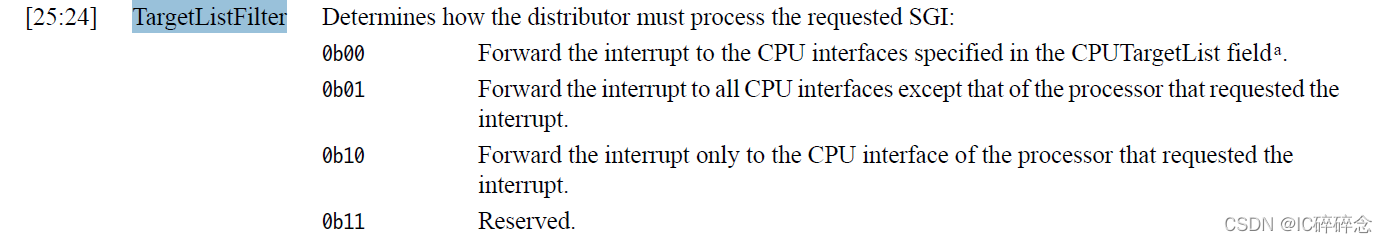

ArgetListFileter

对于TargetListFileter:决定distributor将软中断,如何发送给cpu interface。

◾0b00:按照CPUTargetList的指定,来发送软中断

◾0b01:按照CPUTargetList的指定,来发送软中断,但是不能发送给自己

◾0b10:软中断,只能发送给自己

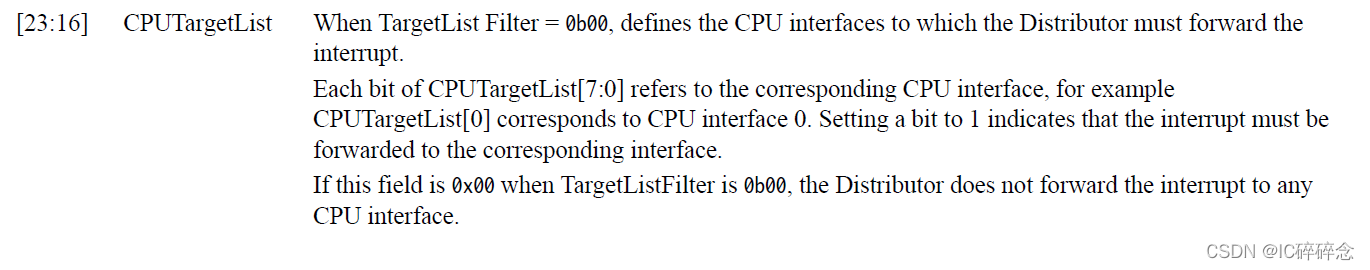

CPUTargetList

描述如下:

对于多core的系统,会给每个core一个编号。gicv2支持最多8个core,因此core的编号就是0-7,刚好8个bit,可以表示。这样的CPUTargetList,就和8个cpu相对应。第0bit,表示core0,第7bit,表示core7。如果想给core1,core2,core7发送软中断,那么此时这个位域要填入0x84。

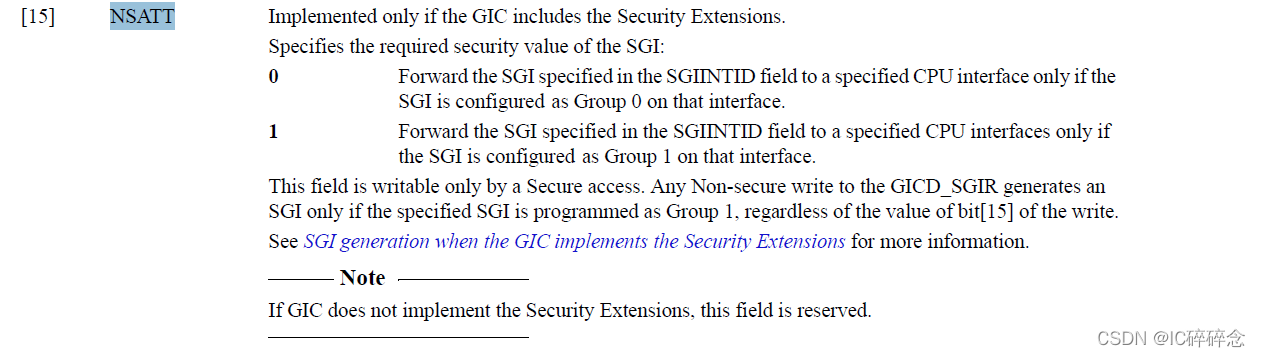

NSATT

描述如下:

这个用来支持安全扩展,在gicv2中,将中断进行了分组

◾group0:安全中断 FIQ

◾group1:非安全中断 IRQ or FIQ

这个bit,用来表示发送的中断,是安全中断,还是非安全中断。而且这个bit,只有core处于安全状态的时候,才能写。如果core是处于非安全状态,那么这个bit被忽略,也就是只能发非安全的中断。

中断组影响中断是否可以转发到CPU接口,也对以后有影响CPU 接口中的路由决策,可能包括是否向处理器作为 FIQ 或 IRQ 异常请求

**SGIINTID:**发送的软中断的中断号

中断优先级

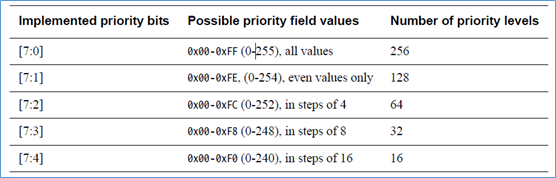

gicv2,支持最小16个,最大256个中断优先级,如下图所示:

如果实现的中断优先级小于256个,那么最低的几个bit,是为0的。

通过设置GICD_IPRIORITYRn寄存器,来设置中断的优先级。这个寄存器是字节有效的,也就是一个字节,对应一个中断的优先级。优先级数值越小,那么这个中断的优先级越高。

高优先级的中断,是可以抢占低优先级的中断。

gic使用例子

下图是gic的使用例子:

外部的中断,连接到gic。由distributor进行中断分组。中断请求,由distributor发送给cpu interface,cpu interface再发送给处理器。

对于支持安全扩展,其应用如下:

安全中断,处于group0,非安全中断处于group1。

gicv2最多只能支持8个core,超过了8个core,那么就不能使用gicv2了。对于手机的arm处理器来说,最多也就8个core。但是对于服务器,桌面级的arm处理器,那么就可能会超过8个core,此时gicv2就不适用了,所以ARM后面又加入GICv3,v4架构。

GICv2的寄存器,都是通过memory-mapped的方式访问。但是中断在一个soc系统中,是经常会产生的,那么处理器就会经常的读取gic的寄存器,而使用memory-mapped的方式去访问,就会影响中断响应速度。在之后的GICv3,v3中,就加入了使用系统寄存器来进行访问,加快中断处理。

GICv2只是一个gic的架构,其实现的对应的IP是gic400

总结与使用过程中注意事项

可配置的cpu_num(1~8)

可配置的spi_nums(0~480),需要是32 的整数倍

AXI_RID_BITS,axi的read id width,至少1bit。

AXI_WID_BITS: axi的write id width 至少1bit。

SGI 是通过写入软件生成的中断寄存器GICD_SGIR生成的。CPU 接口最多可为每个目标处理器生成 16 个 SGI,ID0-ID15。

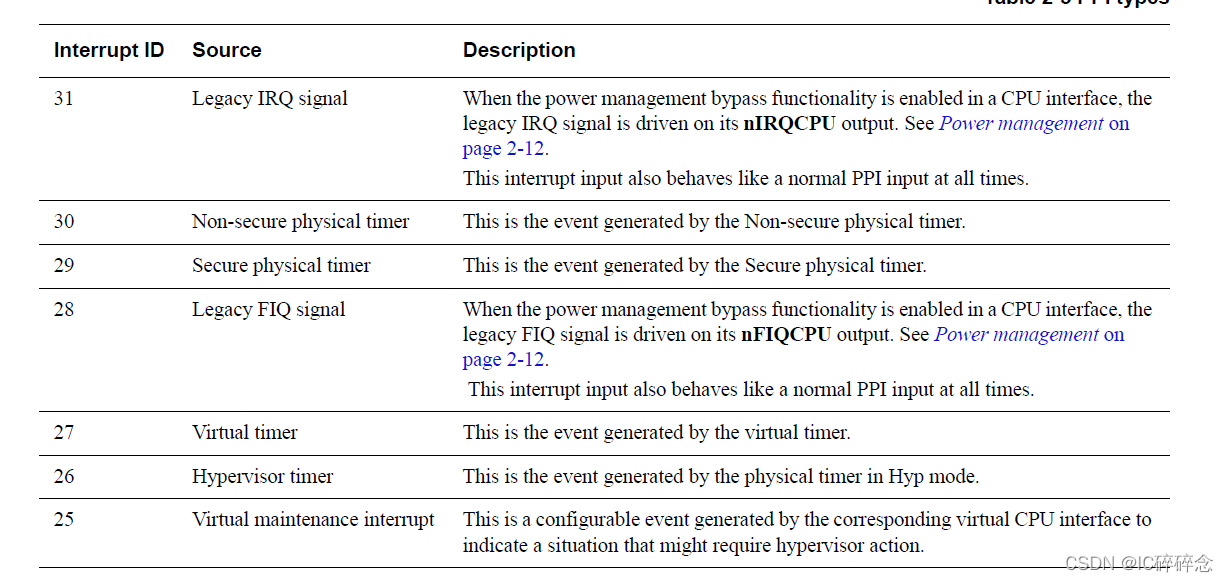

PPI 是特定于单个处理器的中断。所有 PPI 信号都是低电平有效的电平敏感

与A55 cpu相关的PPI

(a)nLEGACYIRQ信号线。对应interrupt ID 31,在bypass mode下(这里的bypass是指bypass GIC functionality,直接连接到某个processor上),nLEGACYIRQ可以直接连到对应CPU的nIRQCPU信号线上。在这样的设置下,该CPU不参与其他属于该CPU的PPI以及SPI中断的响应,而是特别为这一根中断线服务。

(b)nCNTPNSIRQ信号线。来自Non-secure physical timer的中断事件,对应interrupt ID 30。

(c)nCNTPSIRQ信号线。来自secure physical timer的中断事件,对应interrupt ID 29。

(d)nLEGACYFIQ信号线。对应interrupt ID 28。概念同nLEGACYIRQ信号线,不再描述。

(e)nCNTVIRQ信号线。对应interrupt ID 27。Virtual Timer Event,和虚拟化相关,这里不与描述。

(f)nCNTHPIRQ信号线。对应interrupt ID 26。Hypervisor(管理程序) Timer Event,和虚拟化相关,这里不与描述

SPI 可以配置每个SPI是否是边沿触发在上升沿或高电平敏感。

所有信号,包括 SPI,必须与 GIC-400 中的时钟同步。因此,任何来自异步源的中断信号在连接之前必须同步到 GIC-400。

使用步骤:

- 打开ARM核的中断开关,CPSR寄存器

- 打开Distributor的全局开关:GICD_CTLR[0]

- 打开Distributor的中断开关:寄存器GICD_ISENABLER/GICD_ICENABLER

- 配置中断触发方式:GICD_ICFGRn

- 等待中断

- 读取GICC_IAR寄存器,获取中断编号

- 执行中断程序

- 写GICC_EOIR寄存器

GIC-400初始化流程

(1)设置distributor和CPU interface寄存器组的基地址;

(2)读取GICD_TYPER寄存器,计算当前GIC最大支持多少个中断源;

(3)初始化distributor:

a.disable distributor;

b.设置中断分组;

c.设置SPI中断的路由;

d.设置SPI中断的触发类型;

e.disactive和disable所有中断源;

f.enable distributor;

(4)初始化CPU Interface:

a.设置GIC_CPU_PRIMASK,设置中断优先级mask level;

b. enable CPU interface;

452

452

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?