BIST

Created: January 20, 2022 1:53 PM

参考文章如下:

BIST介绍

基础名词扫盲篇

scan_chain 测试基本原理

Question & answer

-

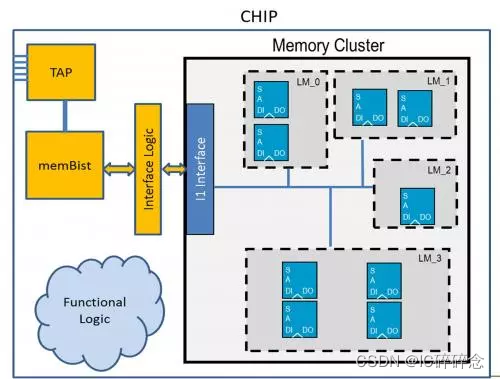

MBIST Memory 内建自测试:

A:MBIST是指在电路中加入针对Memory的自测试电路。在测试模式下,它会接管功能逻辑对memory的控制,依据特定算法,对memory进行读写测试操作,判断Memory是否有制造缺陷。至于面临的挑战,从以下几个方面来探讨:

- 对于Memory Vendor来说, 在新工艺下,memory可能会有新的失效机制,如何设计有效的MBIST 算法是一项重要的研究课题。

- 从EDA角度看,目前业界工具对常规memory (SRAM, ROM, Register File等)的支持已相对成熟。芯片公司对EDA 提供针对特殊类型的memory (如TCAM, DRAM )的测试方案的需求正日渐迫切。

- 从芯片实现的角度看,设计者需要考虑如何使得MBIST逻辑对芯片PPA的影响最小。对于使用带Redundacy Memory的design来说,要考虑自修复(self-repair),也会增加设计和验证的难度。

-

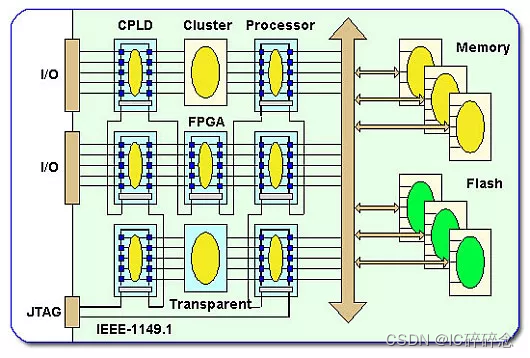

Boundary Scan:

A:Boundary scan 顾名思义,是附加在芯片I/O 周边的扫描测试链,它通过专门的测试端口(TAP)访问。在测试模式下,边界扫描链会接管功能逻辑,对I/O进行灵活访问。边界扫描链的结构,测试端口,以及其控制器(TAP Controller),被IEEE定为标准协议(IEEE 1149), 也称做JTAG. 边界扫描链最早应用于印刷电路板上芯片间的互联测试, 后来也广泛应用于生产测试中对芯片管脚的测试。

-

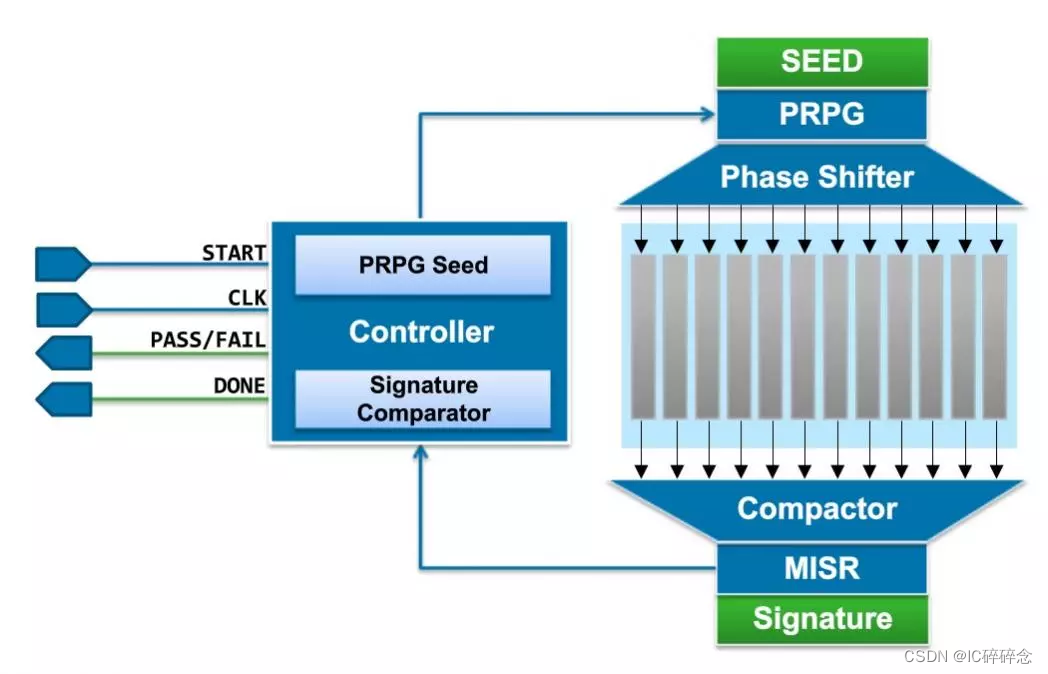

Logic Bist:

A:LBIST (Logic Built-In Self Test)是针对逻辑电路的自测试。测试激励由片上 PRPG (Pseudo-randompattern generation) 来产生。输出响应通过 MISR(Multiple Input Signature Register)来压缩,最后对得到的特征值进行比对。LBIST 多应用于对可靠性要求较高的芯片(如汽车电子,工业级应用)的系统自检测试。LBIST产生的激励是随机的,所以天生的缺陷是测试覆盖率不充分,通过在设计中增加测试点(Test Point Insertion)可以在一定程度上得到改善。

-

为什么bist测试只能跑网表测试?

因为DFT加SCAN 扫描都是在网表加,不会加在rtl级别

-

dft中要求所有的寄存器都是scan寄存器吗?

基本都要求是,除了寄存器输出直连寄存器输入。或者一些func 表明no_dft

-

ac和dc的区别?

dc: stuck at的测试 用的ATE的clk,比较慢

ac: trasition check strat up的clk较慢 capture较快 模拟真实芯片工作频率

9388

9388

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?