一、概念 & 设计

1、中断概述

处理器的中断:

CPU 在正常执行程序但遇到紧急事件时,暂时中止当前程序的执行,转而去为处理紧急的事件。

待处理完毕后再返回被打断的程序处继续往下执行。

退出中断:

中断前的现场被自动从堆栈中恢复。一旦出栈完成,继续执行被中断打断的指令。

出栈的过程也可被打断,使得随时可以响应新的中断, 而不再进行现场保存。中断也可能嵌套。

其他:待独立成新章节。

参考:https://blog.csdn.net/k666499436/article/details/124181471?ops_request_misc=%257B%2522request%255Fid%2522%253A%2522170549276616800182134643%2522%252C%2522scm%2522%253A%252220140713.130102334..%2522%257D&request_id=170549276616800182134643&biz_id=0&utm_medium=distribute.pc_search_result.none-task-blog-2~all~top_positive~default-1-124181471-null-null.142^v99^pc_search_result_base2&utm_term=NVIC&spm=1018.2226.3001.4187

2、STM32F4 中断体系

系统定时器、CSS时钟安全系统、...

内核中断 ↓

NVIC 嵌套向量中断控制器 ---> CORTEX-M4 内核指令执行单元 <---> 中断向量表

外设中断 ↑

串口、定时器、IIC、EXTI(GPIO 等)、...

--------------------

Cortex-M4 内核支持 256 个中断:16 个内核中断和 240 个外部中断,具有256 级的可编程中断优先级设置。

每一个外部中断都可以被使能或者禁止,并且可以被设置为挂起状态或者清除状态。

STM32F4 并没有使用 Cortex-M4 内核的全部东西,而是只用了它的一部分。

--------------------

中断处理程序中,__weak 修饰的回调函数需要用户自己实现。一般用于业务逻辑的处理。

外部中断线可能会复用中断入口。必要时需要在中断处理程序中读取 GPIO 电平来判断。

keil5 -> {}functions:需要编译完成才能使用 hal 库。

3、嵌套中断

1、STM32F4中断的优先级:优先级越小优先级越高。见(异常向量表)

3个固定的优先级,都是负值,不能改变

16个可编程优先级,用4个bit位表示

2、中断抢占:

抢占优先级 > 响应优先级。数值越小,优先级越高。

抢占优先级不同的中断,高优先级可以打断正在进行的低优先级的中断。

抢占优先级相同的中断,高优先级的响应优先级中断不可以打断低响应优先级的中断。

抢占优先级和响应优先级都一样,则优先处理编号较小的中断。

3、中断的优先级分组:工程开发中应当首先确定中断优先级分组,之后就不要再做修改了。

STM32F4 将中断分为 5 个组,每个组有不同的分配情况(抢占优先级+响应优先级)。

抢占优先级在前,响应优先级在后。各占几个位要根据 SCB->AIRCR 中的 bit8 ~ bit10 决定。

--------------------

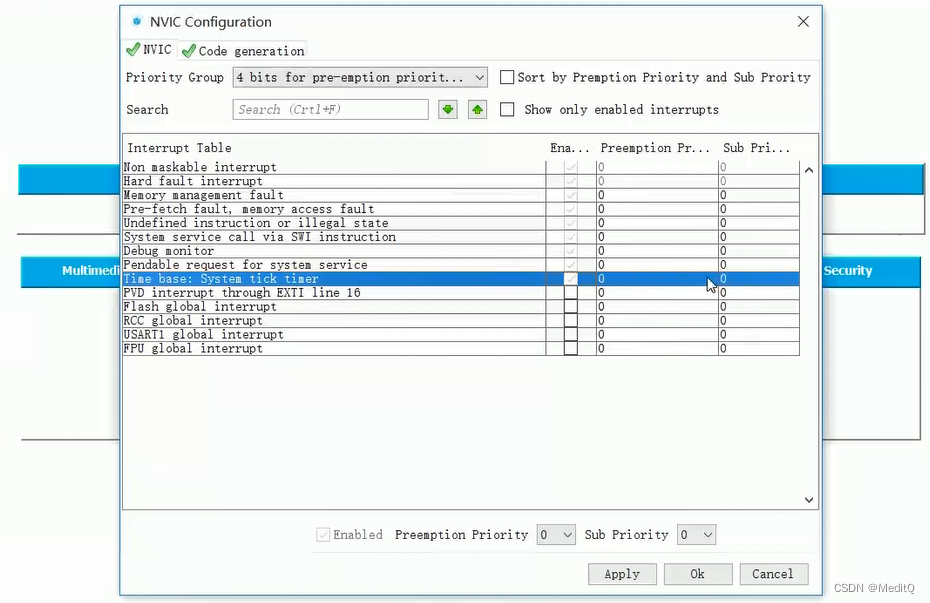

cubeMX 中可以图形化配置 NVIC 并使能。

不建议在应用中将抢占优先级过高(0),否则可能导致系统中断被抢占造成卡死等情况。

4、SCB->AIRCR 优先级设置规则:

组 bit10 ~ bit8 bit7 ~ bit4 结果

0 111 0/4 0位抢占优先级,4位响应优先级

1 110 1/3 1位抢占优先级,3位响应优先级

2 101 2/2 2位抢占优先级,2位响应优先级

3 100 3/1 3位抢占优先级,1位响应优先级

4 011 4/0 4位抢占优先级,0位响应优先级

4、嵌套向量中断控制器 (NVIC)

包括内核异常在内的所有中断均通过 NVIC 进行管理

STM32F405xx/07xx 和 STM32F415xx/17xx 具有 82 个可屏蔽中断通道

STM32F42xxx 和 STM32F43xxx 具有 86 个可屏蔽中断通道(不包括 Cortex™-M4F 的 16 根中断线)

16 个可编程优先级(4 位中断优先级)

低延迟异常和中断处理

电源管理控制

系统控制寄存器的实现

NVIC 和处理器内核接口紧密配合,可处理低延迟中断、晚到中断。

----------

SysTick 校准值寄存器:设置为 18.75 MHz(HCLK/8,HCLK 设为150 MHz),会产生 1 ms 时间基准。

----------

NVIC 寄存器

5、SCB 寄存器

SCB 表示系统控制块。其中还包含一些中断控制相关寄存器。

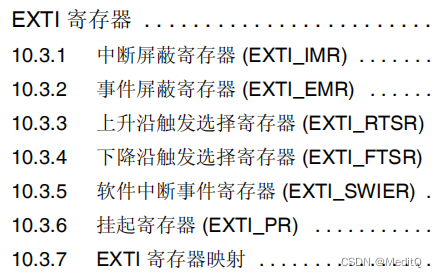

6-1、外部中断控制器 (EXTI)、系统配置控制器 (SYSCFG)

外部中断控制器(EXTI):下图左

包含多达 23 个用于产生事件/中断请求的边沿检测器。控制外部 GPIO 的中断。

EXTI 0~15 总共 16 路:

IO口外部中断在中断向量表中只分配了7个中断向量,只能使用7个中断服务函数

EXTI 0~4 每个中断线分配一个中断向量。

外部中断线5~9分配一个中断向量,共用一个服务函数。

外部中断线10~15分配一个中断向量,共用一个中断服务函数。

剩余的高编号 EXTI 17+ 的功能是架构固定的。

每根输入线可单独配置:

EXTI 0 可配置为 PA0 ~ PI0。

功能可配置为中断或事件,事件可配置触发类型:上升/下降/边沿 触发。脉冲能触发 ADC/定时器 等。

每根输入线还可单独屏蔽。挂起寄存器用于保持中断请求的状态线。

系统配置控制器(SYSCFG):下图右

重映射存储器到代码起始区域。

管理连接到 GPIO 口的外部中断。

管理系统的可靠性特性。

---------------------------------------

在中断控制中,外部中断配置寄存器(SYSCFG_EXTICR 1~4)负责配置 EXTI 对应具体哪个管脚。

每个外部中断配置寄存器只使用 0~15 bit,4 位一组。由小到大共对应 16 个 EXTI。

SYSCFG_EXTICR 1:0~3 bit 对应 EXTI 0;4~7 bit 对应 EXTI 1;... ...

每 4bit 组成的数字,从小到大(0~15)代表:PA[X] ~ PI[X]

1567

1567

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?