最近在DDR4方面做了一些工作,但依然对整个流程理解得不够透彻,遂在去年4月阅读DDR4标准的基础上再次阅读该手册,理清了不少含糊的脉络。由于阅读的英文很快便会忘记,加之阅读英文时脑海中不自觉地翻译,于是大脑不堪重负,忘记速率更快了,遂萌生将其直接翻译的想法。

前两章和第六章之后不翻译,只翻译设计和验证时所需的基本概念,此包括3、4、5章节。翻译过程中结合了不少资料,其中包括CSDN上前辈的翻译:hierro_sic的博客_CSDN博客-DDR4标准,DDR3,SNPS-PHY领域博主

还有些其它的参考博客,分布在各个章节内。

3 功能描述

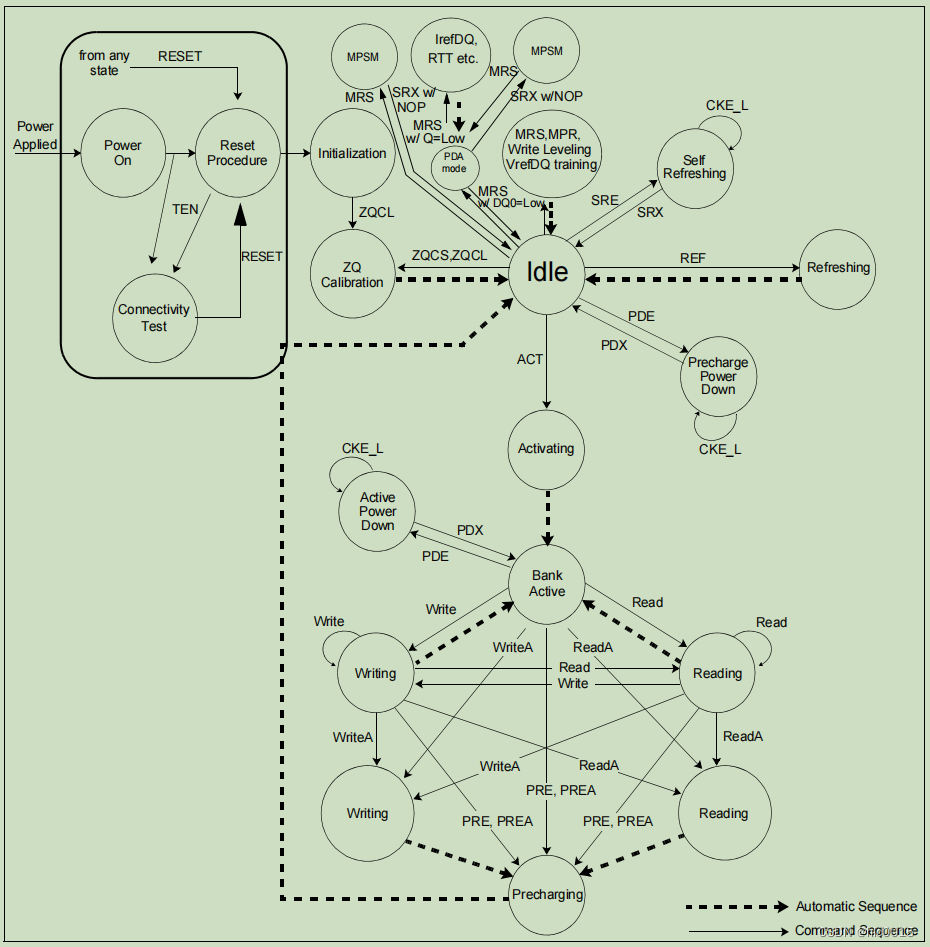

3.1 简略状态图

| 缩写 | 功能 | 缩写 | 功能 | 缩写 | 功能 |

| ACT | Activate | Read | RD, RDS4, RDS8 | PDE | Enter Power-down |

| PRE | Precharge | Read A | RDA, RDAS4, RDAS8 | PDX | Exit Power-down |

| PREA | Precharge ALL | Write | WR, WRS4, WRS8 with/without CRC | SRX | Self-Refresh eXit |

| REF | Refresh, Fine granularity Refresh | RESET_n | Start RESET procedure | MPR | Multi Purpose Register |

| TEN | Boundary Scan Mode Enable |

Note1 这里的简单状态转移图只是一个大概的示意图。对于涉及到多bank操作、或者使能/不使能ODT(on-die termination终端电阻)以及其他情况下的一些操作,上述示意图中并没有将全部细节展示出来。

3.2 基本功能

DDR4 SDRAM是高速动态随机存储器,对于x4/x8的器件,其内部有4个Bank Group(BG),每个BG有4个bank,共16个bank;对于x16器件,其内部分为2个BG,每个BG中有4个bank,共8个bank。

DDR4 SDRAM获取数据的方式为8倍预取(8n prefetch),以此方式来实现高速数据传输的操作。对于IO pin,每个时钟周期传输2个data words,从而实现了8倍预取(时钟上升沿传输一个data word,时钟下降沿传输一个data word,此处的data word不可简单理解为一个字节)。一个单独的读或写操作包含一个8倍预取的bit宽度(8n-bit),对应在DRAM core内部有4个时钟数据的传输,对应在IO端口上为8个n-bit宽度(不是8n-bit,而是8个n-bit),半个时钟周期的数据传输。

DDR4 SDRAM的读和写操作是以突发方式进行的,从一个给定地址开始,并根据突发长度(BL8或者BC4的长度)进行读写操作。读写操作前必须先发送ACTIVATE命令。其地址位跟随ACT命令一起发送过来,用于选择哪个bank和哪个row被激活(被activate),对于x4/x8的器件,BG0-1用于选择bank group,对于x16器件,BG0用于选择bank group;BA0-1用于选择bank,A0-17用于选择row,详见2.8章节。地址位在不同的命令下有不同的含义,例如紧随ACT命令后的READ/WRITE命令,其地址bit表示选择列地址(column location),同时,对于突发的读写操作,还需要根据A10来确定是否进行auto precharge(自动充电),以及根据A12确定发送的burst length是否为BL8或BC4。

当然,在能够对DDR4正常操作之前,整个器件必须被正确地上电以及初始化。

下列章节讲述了复位和初始化、寄存器定义、命令描述和器件操作的细节。

3.3 复位和初始化流程

对于上电和复位初始化,为了防止DRAM进行错误的操作,推荐MR寄存器的默认值如下:

| 设置值 | 含义 |

| MR3 A3 = 0 | Gear down模式为1/2速率 |

| MR3 A4 = 0 | PDA disable(Per DRAM寻址) |

| MR4 A1 = 0 | Max power saving mode disable |

| MR4 A8-6 = 000 | CS to Cmd/Addr latency disable |

| MR5 A2-0 = 000 | CA Parity latency mode disable |

| MR4 A13 = 0 | Hard post package repair mode disable |

| MR4 A5 = 0 | Soft post package repair mode disable |

3.3.1 上电初始化流程

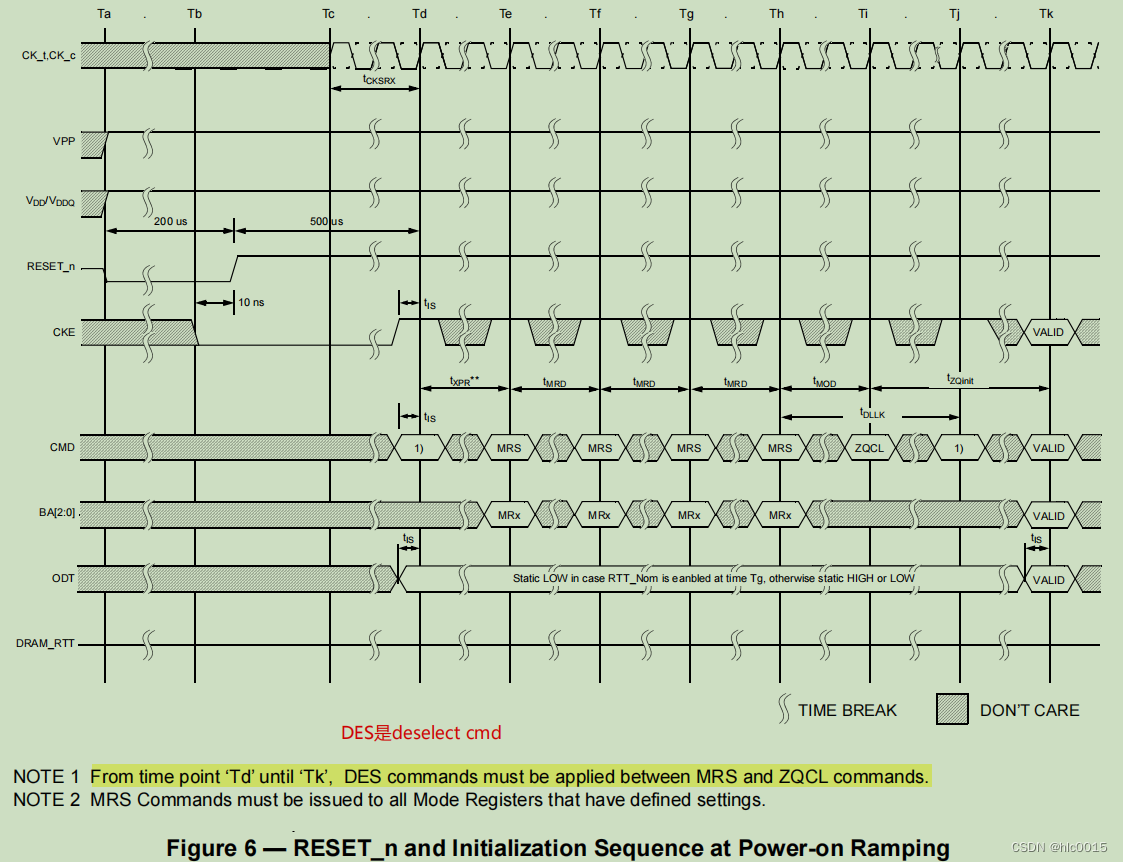

下列流程为上电以及初始化的流程,时序图参见图6。

- 供电。推荐RESET_n和TEN信号保持在0.2VDD以下,其它的输入管脚可能为undefined状态。在稳压状态下,RESET_n必须低于0.2VDD,并保持最小200us,TEN必须低于0.2VDD并保持最少700us。在RESET_n释放之前,CKE必须为低。从300mV到VDD min的电源电压斜坡时间不能大于200ms;并在在斜坡时间之间,VDD >= VDDQ,且(VDD-VDDQ) < 0.3V。VPP需同时和VDD拉高,或早于VDD拉高,且在所有情况下,VPP电压值必须大于等于VDD。

VDD和VDDQ从同一电源接出来,并且

1. 除了VDD/VDDQ/VSS/VSSQ pin脚,其它pin脚的电源电压必须小于等于VDD和VDDQ,且必须大于等于VSS和VSSQ。另外,一旦电压稳定后,VTT被限制在最大为0.76V。

2. VrefCA = VDD/2

3. 在VDDQ之前或同时应用VDD,没有任何斜率反转。

4. 在VTT & VrefCA之前或同时应用VDDQ,没有任何斜率反转。

5. 在VDD之前或同时应用VPP,没有任何斜率反转。

6. 在VDD之前或同时应用VPP,没有任何斜率反转。

- 在RESET_n释放后,等待500us,CKE拉高。在此期间,DRAM将会启动内部的初始化,且不需要外部时钟参与。

- 在CKE拉高前,CK_t/CK_c必须保持稳定至少10ns或至少5个CK周期。由于CKE是一个同步信号,其对应的建立时间必须被满足(tIS)。同时,DES命令也必须在时刻Td处被寄存。一旦在复位之后CKE被拉高,则CKE必须被持续地拉高,直到初始化序列结束,此间也包括tDLLK和tZQinit的末尾。

- 在RESET_n有效期间,DDR4 SDRAM将其ODT(终端电阻)保持在高阻态。ODT pin脚在CKE拉高之前的tIS时间之前可以为0/1态,当CKE拉高,ODT pin可以静态地保持在高/低状态。假如MR1中的RTT_NOM被使能,则ODT必须为0。在所有情况下,直到上电初始化完成,包括tDLLK和tZQinit的末尾,ODT pin的输入电平一般保持不动。

- CKE拉高后,发送MRS命令来加载模式寄存器前(mode register),等待tXPR时间(Reset CKE Exit time),其中tXPR = Max(tXS, 5nCK)。

- 发送MRS命令来加载MR3(为了使MRS命令指向MR3,需要令BG0=0,BA1-0 = 1);

- 发送MRS命令加载MR6(BA0 = 0, BG0 = 1, BA1 = 1);

- 发送MRS命令加载MR5(BA1 = 0; BG0 = 1, BA0 = 1);

- 发送MRS命令加载MR4(BA1 = 0; BA0 = 0, BG0 = 1);

- 发送MRS命令加载MR2(BG0 = 0, BA0 = 0, BA1 = 0);

- 发送MRS命令加载MR1(BG0 = 0, BA1 = 0, BA0 = 1);

- 发送MRS命令加载MR0(BG0 = 0, BA1 = 0, BA0 = 0);

- 发送ZQCL命令开始ZQ校准。

- 等待tDLLK和tZQinit时长,注意,这两者时间有重叠。

- 流程结束,目前DDR4能够被用来后续的读写训练,包括Vref训练(参考电压训练)以及write leveling训练。

3.3.2 在上电初始化过程中VDD的转换速率要求

| 符号 | 最大值 | 最小值 | 单位 |

| VDD_sl | 0.004 | 600 | V/ms |

| VDD_on | 200 | ms |

3.3.3 在稳定电压下的复位初始化

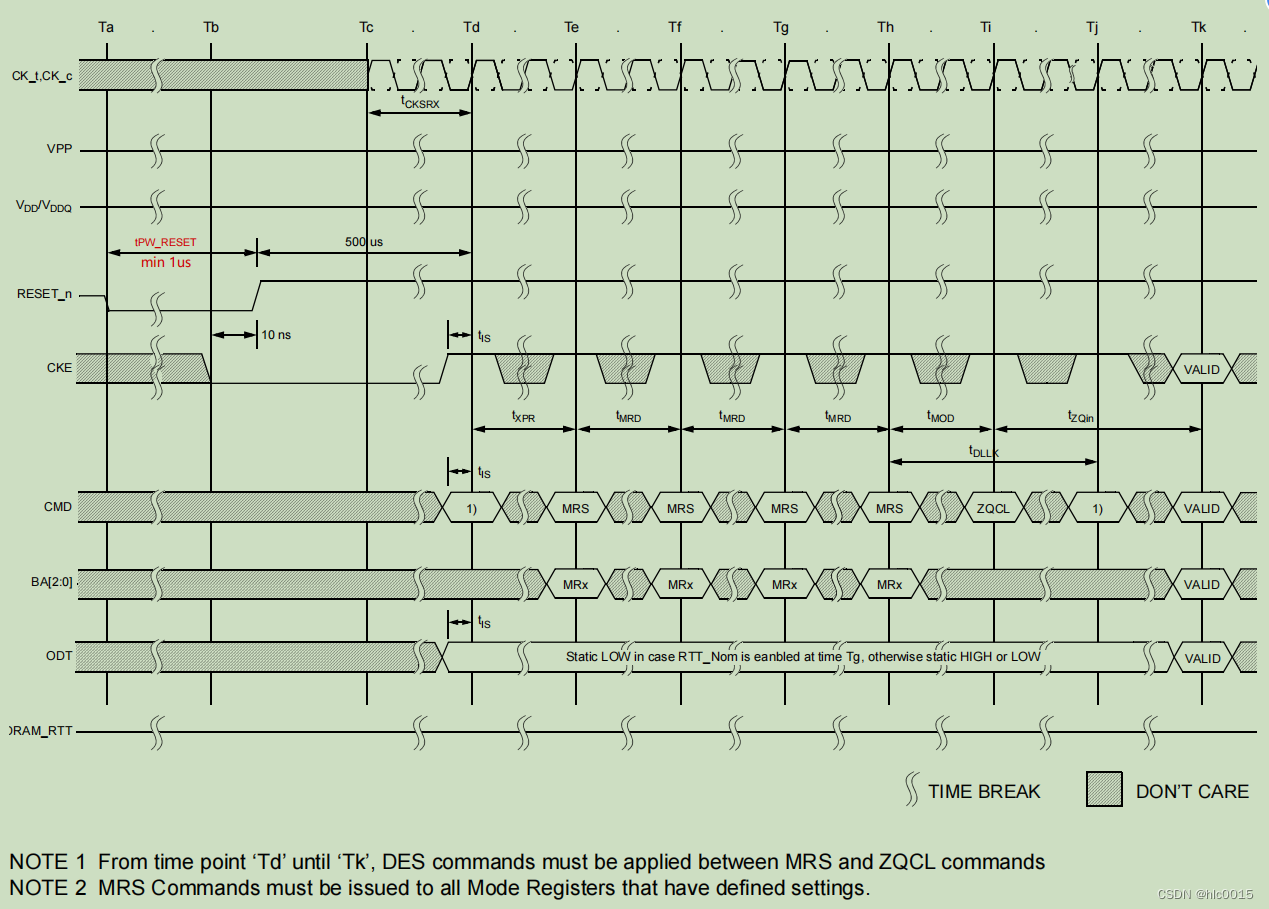

图7显示了在无电源间断的情况下进行复位的时序图。

- 将RESET_n信号置为低于0.2VDD的电平。RESET_n需要保持最少tPW_RESET的时间。在RESET_n信号拉高之前,CKE必须保持为低至少10ns。

- 之后,参见3.3.2章节的上电初始化流程中的第2到10步骤。

- 复位流程结束,DDR4 SDRAM已经ready。

3.4 寄存器定义

3.4.1 对MR寄存器进行编程

为了更加灵活地应用,DDR4提供了7个模式寄存器(MR),用户可以利用MRS命令写入不同的值。根据功能和模式的不同,MR被分为了不同的域。由于并不是所有的MR都有默认值,所以MR寄存器必须被初始化(或者说被重新初始化),例如在上电完成后或复位完成后对MR寄存器进行写入。

当然,MR寄存器的值也可以在DDR4正常工作期间被修改。当对MR进行写入/修改时,即使用户只对MRS某些域进行写入,则所有的地址域都要被重新写入(例如对MR4的A1进行修改,不修改其它的值,但A2, A3...的值也会被写入,所以正确的做法是将其它的值保持与原来一样的值,并写入到MR4中)。MRS命令和DLL Reset并不影响DRAM中存储的内容,这意味着这些命令能够在上电后的任何时间/时刻处被执行(被发送)。不过,MRS命令只能在DRAM处于idle状态时被发送。

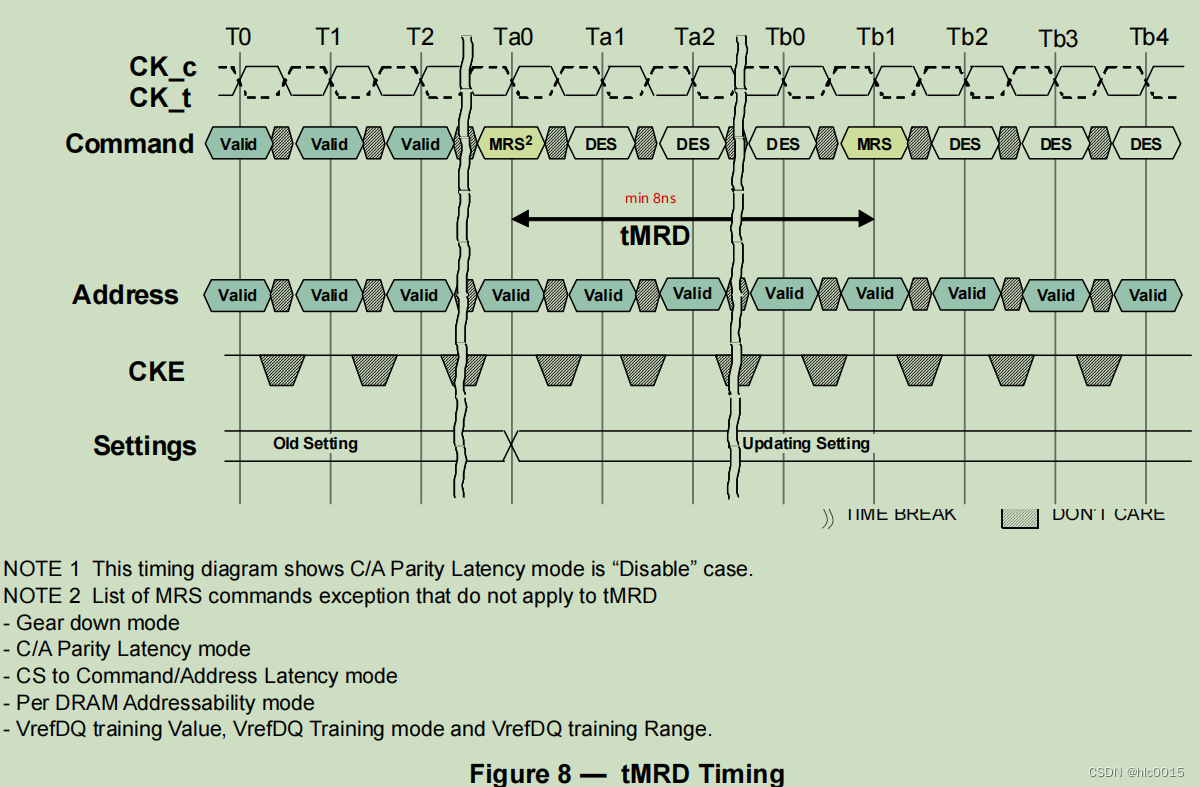

图8表明两个MRS命令发送的时序间隔。

有一些MR的设置影响了ADDR/CMD/control的输入功能,在此情况下,当当前MRS命令完成后,下一个MRS命令才会被允许发出。

在此情况下,MRS命令间的间隔时间并不是像图8上的tMRD时序,这些MRS命令间的间隔需要根据不同的功能描述来确定。

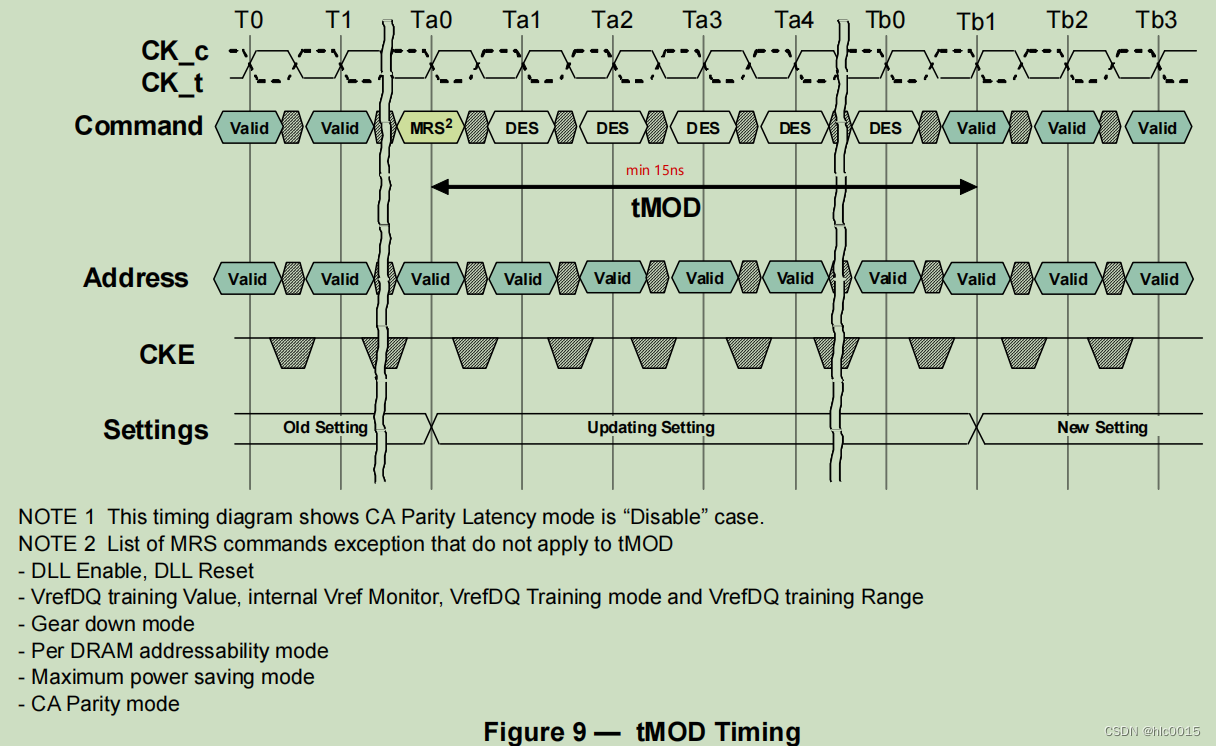

大多数MRS命令到Non-MRS命令(不是MRS命令的命令)间的间隔为tMOD,tMOD时间可以让DRAM来更新MR寄存器,准确来说应该是加载MR寄存器的内容,tMOD是MRS到non-MRS命令的最小时间要求(其中包括DES命令),如图9所示。

在某些MR setting的情况下,其function update需要更长的时间来更新(比tMOD时间更长)。在图9的NOTE2注释中,列出了不应用于除DES之外的下一个有效命令的MRS命令。这些MRS命令输入的情况具有独特的MR设置过程,因此请参考其对应的具体的功能描述。

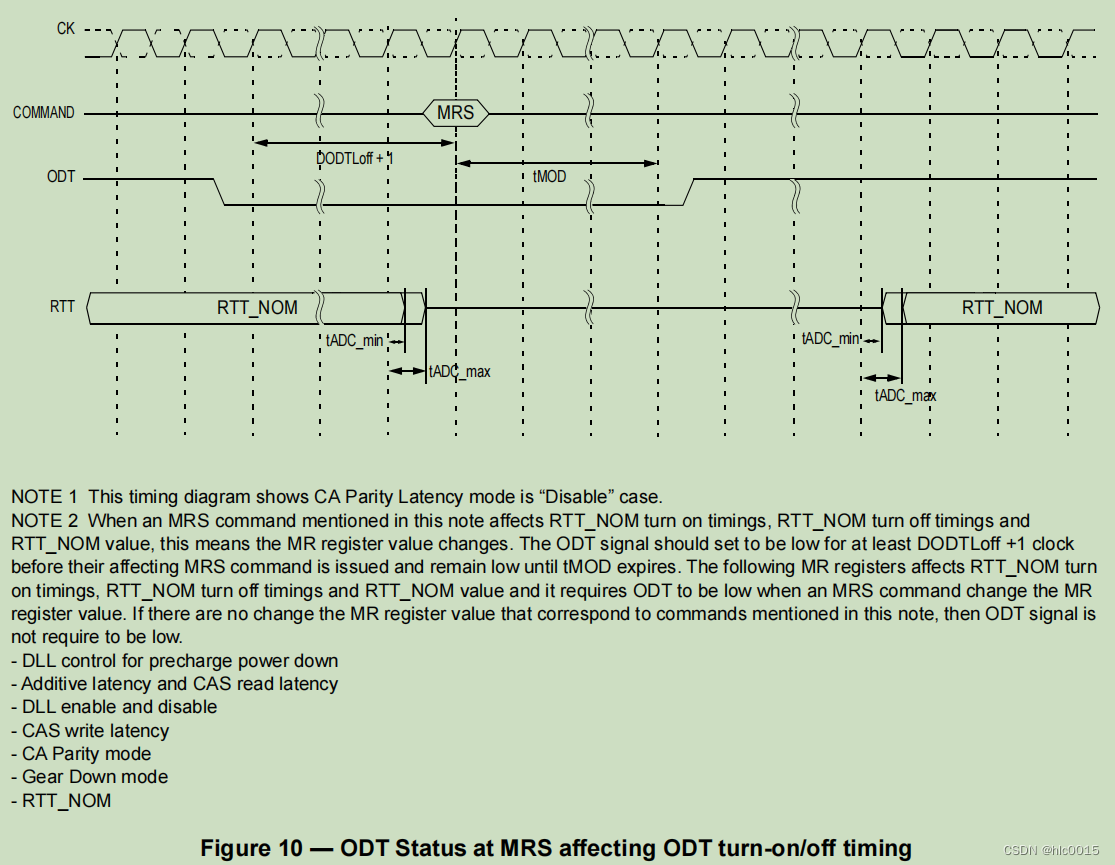

上图中出现了ODT pin的改变,在做ODT时需要注意。其中,图10的NOTE2翻译如下:

DLL control for precharge power down, Additive latency and CAS read latency, DLL enable and disable, CAS write latency, CA Parity mode, Gear down mode等这些MRS命令会影响RTT_NOM的打开时序/关闭时序以及影响RTT_NOM的取值,这意味着MR寄存器的值被改变了。此时,在能够影响RTT_NOM开关时序或RTT_NOM值的MRS命令发送之前,ODT pin应该拉低至少DODTLoff + 1个时钟周期,并且在MRS发送后,持续tMOD时间后,ODT pin才能拉高。除了上述命令外,其它的MRS命令的发送并不需要将ODT pin拉低。

只要DRAM处于idle状态,在正常操作情况下,MR寄存器中的内容以及时序要求可以被改变。例如在所有bank处于precharge状态,且tRP时序满足,所有的数据突发传输已经完成,且在发送MRS命令前CKE已经拉高。

对于MRS命令来说,如果想改变RTT_NOM的功能(从enable到disable,或者从disable到enable),ODT pin必须在MRS命令发送前拉低。参见图10的NOTE2所述。在tMOD结束后,ODT pin拉高。如果在MRS命令之前或之后将RTT_NOM功能禁用,则MRS命令并不关心ODT pin的高低状态。(其实这段话和图10的NOTE2是一个意思)。

3.5 模式寄存器

此处内容大多为图表,不贴图,移步手册自行查阅。

在MR3中存在4个MPR page(MPR页),每个MPR page又分为4个location:MPR0~3,共16个MPR。其中MPR page3为制造商自定义的。

MR7在DDR4中未用到。

1105

1105

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?