最近在DDR4方面做了一些工作,但依然对整个流程理解得不够透彻,遂在去年4月阅读DDR4标准的基础上再次阅读该手册,理清了不少含糊的脉络。由于阅读的英文很快便会忘记,加之阅读英文时脑海中不自觉地翻译,于是大脑不堪重负,忘记速率更快了,遂萌生将其直接翻译的想法。

前两章和第六章之后不翻译,只翻译设计和验证时所需的基本概念,此包括3、4、5章节。翻译过程中结合了不少资料,其中包括CSDN上前辈的翻译:hierro_sic的博客_CSDN博客-DDR4标准,DDR3,SNPS-PHY领域博主

还有些其它的参考博客,分布在各个章节内。

4.7 Write Leveling

关于write leveling的含义和目的,可以参见DDR学习时间(PartB-3):Write Leveling。

Write Leveling可以用来调整DQS_t/c和CK_t/c之间的关系。Memory Controller必须有能够调整DQS_t/c和CK_t/c的延迟的功能,从而使得DQS_t/c和DRAM时钟的上升沿对齐。在DQS_t/c的上升沿采样CK_t/c,并通过DQ总线返回。Memory Controller重复此过程,直到DQS采样CK为1,从而保证tDQSS满足规定的时序要求。

除了tDQSS,tDSS和tDSH也需满足规定的时序要求。一个同时实现这些时序要求的做法是,将实际的tDQSS和DQS_t/c的占空比和抖动结合起来考虑。取决于实际的tDQSS,实际的tDQSL和tDQSH可能比手册中定义的时间要长(详见AC Timing Parameters章节)。

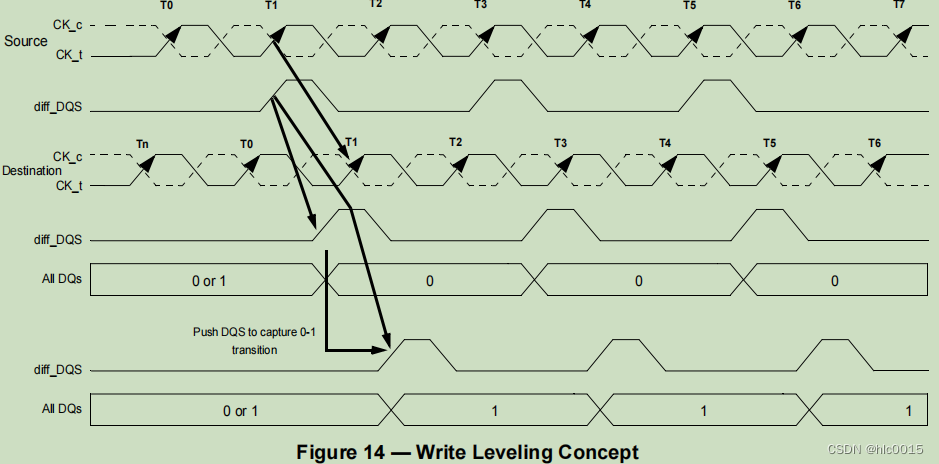

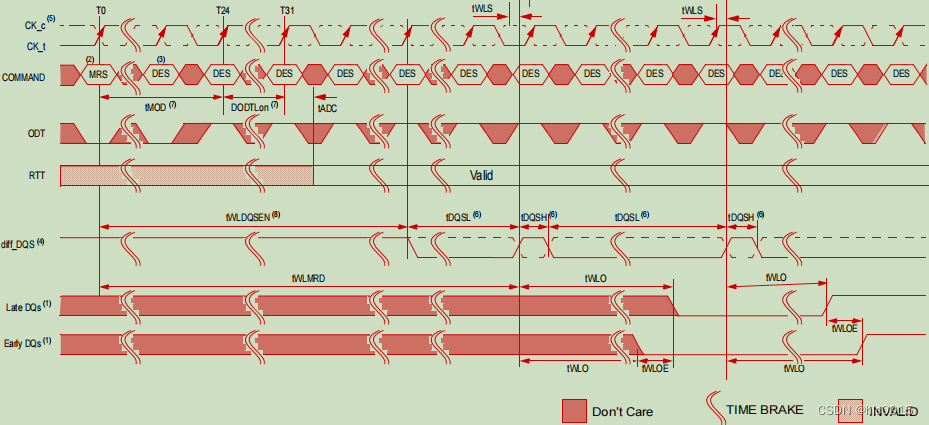

下图显示了Write Leveling的过程。

DQS_t - DQS_c driven by the controller during leveling mode must be terminated by the DRAM based on ranks populated. Similarly, the DQ bus driven by the DRAM must also be terminated at the controller。这句话说的是在Write Leveling时,DQS由memory controller驱动,且送到DRAM颗粒,也就是说DRAM不驱动DQS(在正常的RD操作中,DQS是数据返回的有效信号,由DRAM驱动,在write leveling模式下,DQS由MC驱动),这是一个单向的过程。DQ由DRAM驱动送到memory controller处,MC不驱动DQ,同样,这也是一个单向的过程。

所有的数据bit都应该返回write leveling的结果,无论器件是X4, X8还是X16。由于write leveling是以字节为单位进行的,所以对于X16器件,两个byte lanes必须分别进行leveling。因此,必须实现对每个byte lane的单独的反馈机制。对于X4和X8器件来说,利用diff_DQS进行反馈,但是对于X16器件来说,利用diff_UDQS(高8位)和diff_LDQS(低8位)进行反馈。

4.7.1 Write Leveling中的DRAM设置以及DRAM termination功能(这里的termination指终端电阻)

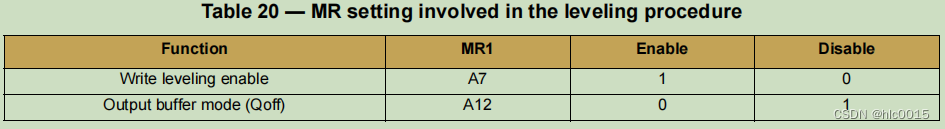

表20展示了Write Leveling时的MR设置。

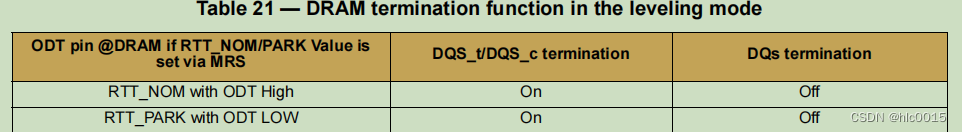

表21展示了Write Leveling模式下DRAM终端电阻的功能。需要注意的是,不同于正常操作模式,在Write Leveling模式下,ODT pin仅仅影响DQS_t/c的终端电阻的使能与否,表21正好也展示说明了这一点。

NOTE1: 在Write Leveling模式下,MR1的A7一定为1,无论MR1的A12电平的高低,所有的RTT_NOM和RTT_PARK的设置都是可以的。

NOTE2: 在Write Leveling模式下,不支持动态ODT功能,并且在进入Write Leveling模式前,需将MR2的A11-9设置为0,以此关闭动态ODT。

4.7.2 Write Leveling模式的流程

内存控制器通过设置MR1的A7为1来使DRAM进入Leveling模式。进入此模式后,DQ管脚便处于undefined的驱动状态。在此模式期间,仅允许DES和MRS命令发送,且MRS命令仅限定于改变Qoff(MR1的A12)和退出write leveling模式(MR1的A7)。在发送MRS退出write leveling模式时,除了MR1的A7会改变,MR1的A12-A8,A2-A1也可以改变。由于内存控制器在做write leveling时每次只能对一个rank进行write leveling,故必须通过设置MR1的A12为1来disable其它rank的输出(此处留一个疑问,我自己也想知道答案:根据什么来选择disable的rank的输出?)。内存控制器可以在tMOD之后(因为tMOD之后DRAM能够接受ODT pin上的信号)置位ODT(让ODT有效)。

DQS_t用实线表示,DQS_c用虚线表示。如下图所示。在发送MRS命令后的tWLDQSEN时间后,DQS_t/c被驱动,且此时DRAM会将终端电阻用于DQS_t/c信号上,从而驱动它们。在tDQSL和tWLMRD时间后(两者是并行的关系),内存控制器驱动DQS_t/c信号来采样由内存控制器驱动的CK_t/c信号。tWLMRD的最大值与控制器有关。

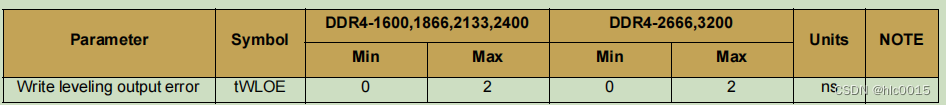

在tWLO时间后,采样的结果通过所有的DQ bit进行异步反馈,最早到来的DQ信号和最晚到来的DQ信号有一个时间差,其定义为tWLOE,其最小值为0,最大值为2ns。回传的DQ信号不像正常操作DRAM一样需要DQS_t/c信号用于指示。内存控制器通过采样DQ信号从而决定DQS_t/c的延迟值。一旦DQS_t/c采样CK_t/c信号的采样值从0变为了1,内存控制器将锁定此时对应的延迟值。

时序图中,

- DDR4通过所有的DQ信号来回传leveling结果

- MRS:将MR1设置为进入write leveling模式

- DES: DESELECT命令

- diff_DQS = DQS_t - DQS_c。时序图上的起点为零点。

- CK_t以实线表示,CK_c以虚线表示。

- DQS_t/c需要满足脉冲宽度的最小值tDQSH(min)和tDQSL(min),这俩值的定义参见正常写数据的值,脉冲的最大宽度由系统决定。

- tMOD(min)= max(24nCK, 15ns), WL = 9(CWL = 9, AL = 0, PL = 0), DODTLon = WL - 2 = 7。

- 当ODT有效时,tWLDQSEN必须满足如下等式:

在DLL有效时,tWLDQSEN > tMOD(Min) + ODTLon + tADC;

在DLL无效时,tWLDQSEN > tMOD(Min) + tAONAS;

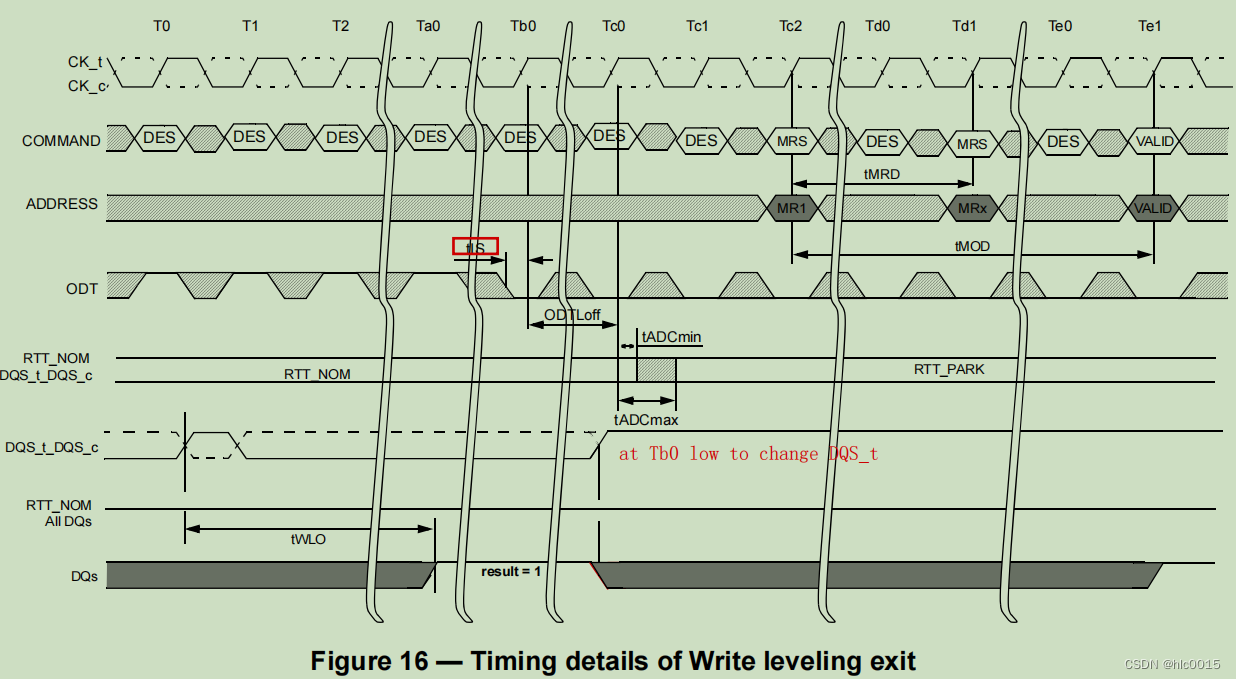

4.7.3 Write Leveling模式的退出

如下图所示。

1. 在T0时为最后一个DQS-t/c信号的脉冲,且在Tc0时刻停止驱动DQS-t/c信号。且从此刻开始直到tMOD过后,也就是Te1时,所有的DQ管脚才会真正有效,在此之前都是undefined状态。

2. 在Tb0是驱动ODT管脚为0,tIS时序必须满足。

3. 关闭RTT后,也就是ODT管脚为0后,通过MRS命令使其退出Write leveling模式(详见Tc2时刻)。

4. 在tMOD时间后,其它有效的命令才能被允许发出。当然,MRS设置MR1的命令发出后,其它的MRS命令可以在tMRD之后发出。

4.8 温控的刷新模式(这个用得也挺少)

通过MR4的A3进行启用/不启用此模式。同时也支持在MR4的A2中选择为正常模式还是extended模式。

4.8.1 正常温控模式

此时MR4的A3 = 1, A2 = 0,刷新命令应当在平均的刷新间隔周期进行发送,正常模式下(0℃-85℃),对于2Gb,4Gb,8Gb,16Gb的器件来说,平均刷新周期间隔为7.8us。此模式下,系统应该保证温度不要超过85℃。

在45℃以下,DDR4会通过跳过(略过)外部刷新命令与gear ratio来调整内部的平均刷新周期间隔。在此模式下,在任何温度下跳过的外部刷新命令都能不超过四分之三。内部的平均刷新周期间隔的调整在DRAM内部自动完成,用户无需提供额外的控制。

4.8.2 扩展的温控模式(extended temperature mode)

此时MR4的A3 = 1, A2 = 1,刷新命令应当在平均的刷新间隔周期进行发送,扩展模式下(85℃-95℃),对于2Gb,4Gb,8Gb,16Gb的器件来说,平均刷新周期间隔为3.9us。此模式下,系统应该保证温度不要超过95℃。

在45℃以下,DDR4会通过跳过(略过)外部刷新命令与gear ratio来调整内部的平均刷新周期间隔。在此模式下,在任何温度下跳过的外部刷新命令都能不超过八分之七。内部的平均刷新周期间隔的调整在DRAM内部自动完成,用户无需提供额外的控制。

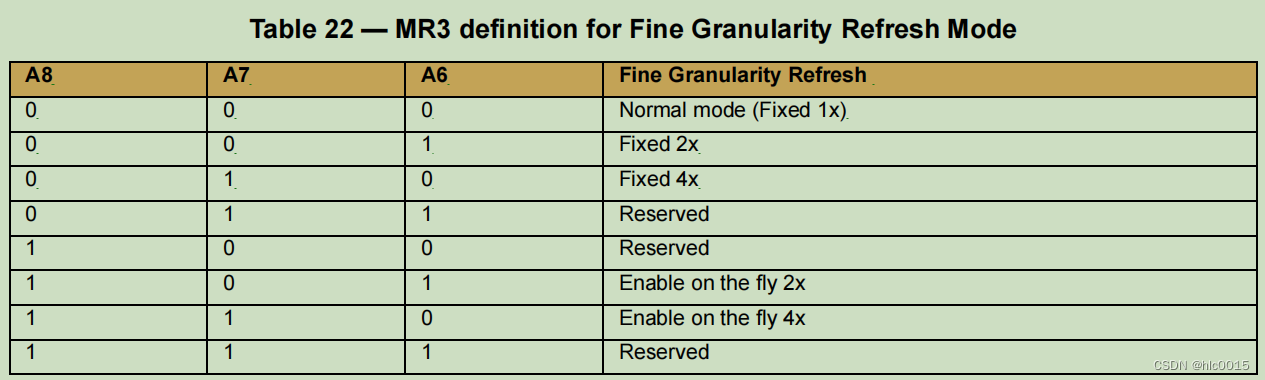

4.9 细粒度刷新模式

4.9.1 MR和命令真值表

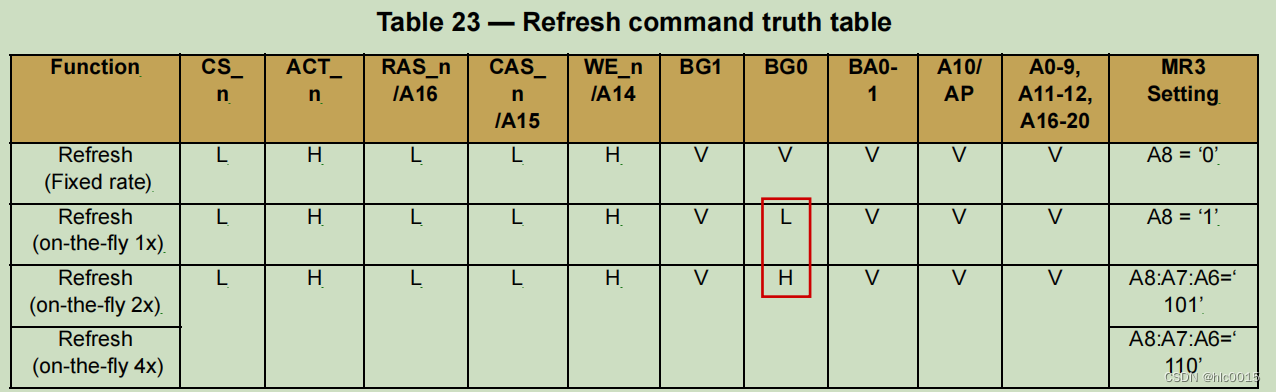

DDR4的刷新周期时间(Refresh cycle time,tRFC)和平均刷新间隔(tREFI)能够通过MRS命令进行更改。在固定模式下(fixed mode),MR寄存器中应该设置一组tRFC和tREFI值,在on the fly模式下,需要设置两组时间值。在发出任何on the fly刷新命令之前,MRS必须像表22所示地启用on the fly模式。

合理地设置MR寄存器的值便可选择两种类型的on the fly模式(1x/2x,1x/4x模式)。当两种on the fly模式中的一种被选择时,也就是A8 = 1时,且当发送刷新命令时,DDR4 SDRAM通过判断BG0的值,来动态切换内部刷新配置值(在1x和2x间或1x和4x间切换),并执行对应的刷新操作。命令真值表如表23所示。

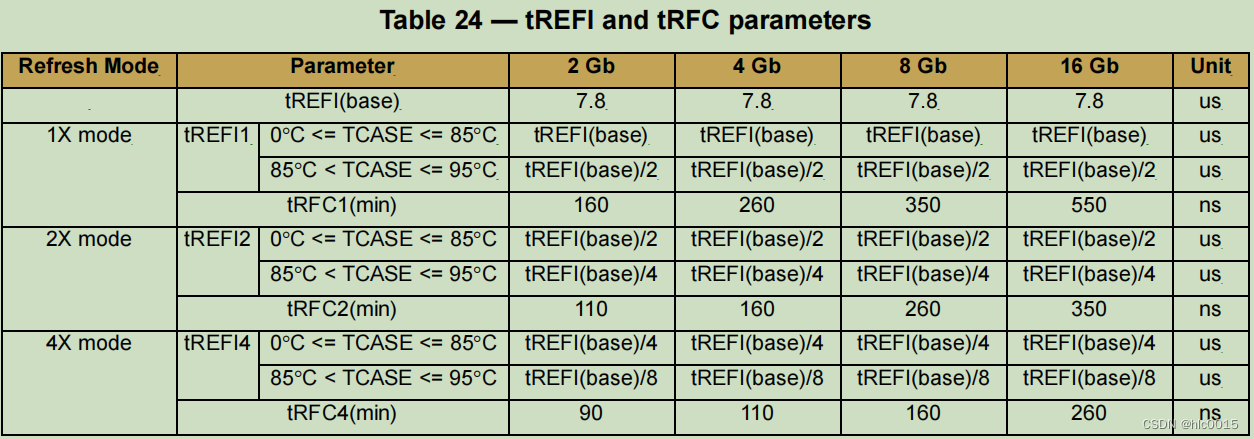

4.9.2 tREFI和tRFC参数

默认的刷新模式为1x模式,其对应的参数为tREFI1(tREFI1=tREFI(base))和tRFC1;在2x模式下,无论是fixed 2x模式还是on the fly的2x模式,其参数tREFI2(tREFI2=tREFI(base)/2,在4x模式下,tREFI4=tREFI(base)/4。在每个模式下,tRFC的值参见表24。

以正常频率发送刷新命令,且一次刷新的时长也为正常的刷新时长,则为REF1x命令;当刷新命令的发送频率为正常的两倍时,为REF2x命令;以此类推,当刷新命令的发送频率为正常的四倍时,为REF4x命令。

当然,在固定的1x模式(fixed 1x mode),只能发送REF1x命令;在固定的2x模式(fixed 2x mode),只能发送REF2x命令;在固定的4x模式(fixed 4x mode),只能发送REF4x命令。当处于on the fly 1x/2x模式下,可以发送REF1x和REF2x命令;当处于on the fly 1x/4x模式下,可以发送REF1x和REF4x命令。这些都是一一对应的关系。

可见,上表中在extended温度模式下,发送的刷新频率快了一倍。

4.9.3 改变刷新速率

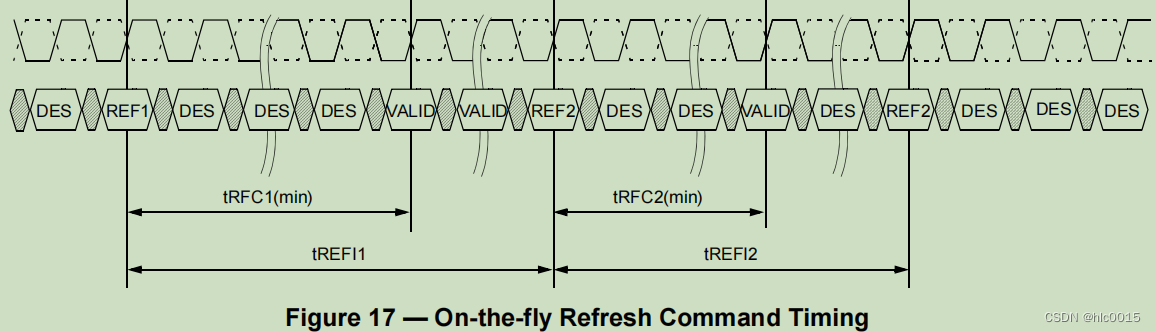

无论是通过MRS还是通过on the fly的方式改变刷新速率,只要改变了,在改变的时刻处就会立马启用新的刷新时间参数(tREFI和tRFC)。如图17所示,当REF1x命令发送时,对应的tRFC1和tREFI1参数被立即使用;当REF2x命令发送时,对应的tRFC2和tREFI2参数也被立即使用。

在刷新速率改变之前,必须满足如下条件,否则,DDR4 SDRAM内的数据可能出错。

- 在fixed 2x刷新速率模式下或在on-the-fly 1x/2x刷新模式下,必须发送偶数个REF2x命令。

- 在on-the-fly 1x/2x刷新模式下,必须在任何两个REF1x命令间发送偶数个REF2x命令。

- 在fixed 4x刷新速率模式下或在on-the-fly 1x/4x刷新模式下,发送的REF4x命令的个数必须为4的倍数。

- 在on-the-fly 1x/4x刷新模式下,必须在任何两个REF1x命令间发送4的倍数个REF4x命令。

对于1x刷新速率模式,无特殊限制。从fixed模式切换到on-the-fly模式,如果刷新频率没变,仅仅是模式变了,并不视为改变了刷新速率。

4.9.4 温控的刷新模式和其它刷新模式

当温控的刷新模式打开,只能用fixed 1x模式进行刷新;当用其它的模式进行刷新时,必须关闭温控的刷新。总而言之,两者是互斥的关系。

4.9.5 自刷新的进入和退出

在进入自刷新模式之前,无论是处于1x, 2x还是4x模式,也无论发送了多少个刷新命令,都不影响自刷新的进入。然而,一旦退出自刷新,则对刷新命令有额外的要求。这些要求取决于自刷新进入前的条件。具体条件如下:

- 对于fixed 1x模式,无任何要求。

- 在fixed 2x模式或者on-the-fly 1x/2x模式下,推荐的做法为,在进入自刷新之前需要发送偶数个REF2x命令。如果满足这个条件,那么在自刷新退出时,无需额外的刷新命令。如果未满足上述条件,在自刷新退出时,要么发送一个额外的REF1x命令,要么发送额外的两个REF2x命令。这些额外的刷新命令不计入平均刷新间隔tREFI的计算。

- 在fixed 4x模式或on-the-fly 1x/4x模式下,推荐的做法为,在进入自刷新时需发送4的整数倍个REF4x命令。如果满足这个条件,那么在自刷新退出时,无需额外的刷新命令。如果未满足上述条件,在自刷新退出时,需发送一个额外的REF1x命令,或4个额外的REF4x命令。这些额外的刷新命令不计入平均刷新间隔tREFI的计算。

243

243

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?