1.概述

很久没有写文章了,有空余时间还是分享一点技术干货。今天写一下zynq+nvme高速存储设计思想,zynq处理器是将ARM和FPGA集成在一起的处理器,区别于以前ARM+FPGA的板间架构,采用AXI内部总线实现ARM和FPGA内部的通讯,支持低速AXI-GP接口(类型Local Bus),高速AXI-HP接口,ARM端简称PS,FPGA端简称PL。如果数据过PS端,那么数据会经过HP接口,软件上的数据解析和拷贝,这样存储速率大约为130MB/s,速率比较慢,所以就引入了本文方案,控制走PS,数据PL实现分流操作。

2.方案设计

存储方案使用处理器为xilinx公司的xz7045芯片,SSD选用m.2接口的固态硬盘,SSD盘支持pcie接口和nvme协议,SSD盘挂载到PL,数据输入挂载到PL,PL的PCIe IP支持接口2.0,PS运行Linux操作系统。本次存储方案采用linux文件系统进行管理,使用文件系统接口,通过读写文件就能实现数据的下盘和导出操作。FPGA将数据缓存在DDR中,PS直接控制数据从FPGA直接写入到SSD,从而实现高速存储,存储方案如图 1所示。

此处方案细节已经删除。

3.FPGA设计

FPGA设计包括,DDR乒乓设计,PCIE接口转BRAM,高速GTX接口等。vivado设计框图如下nter)

4.软件设计

软件设计分为四个部分,PCIE驱动,NVME驱动,自定义驱动和应用程序。PCIe驱动负责解析PCIe接口,NVME驱动解析NVME协议,自定义驱动用于管理NVME驱动和与应用程序交互,应用程序负责文件信息管理,与上位机交互等操作。

软件设计有几个细节需要注意,文件信息可以放到SSD中,对速度不影响,异常掉电软件需要好好处理,数据不是完整的8M块也需要处理。异常掉电和数据不是完整8M块可以放到一起处理,异常掉电尽量让FPGA去检测。HP接口数据是直接到DDR,需要注意Cache一致性问题,因为存在HP接口Cache一致性,当从网络卸载数据时还存在网络MAC的DMA Cache一致性问题,这里涉及东西比较多,后期文章讲解。下图是自定义驱动的框架。

5.PCIE中断分析

PCIE中断分为硬中断和软中断,在zynq中中断处理比较特殊,因为PCIe的RC和协议解析是在不同处理上,中间只能通过GPIO和HP接口进行交互。

PCIe硬件中断如下所示

zynq中PCIe的软中断比较特殊,并不能完全按照MSI中断方式取处理。

PCIe真正软中断处理方式如下所示。

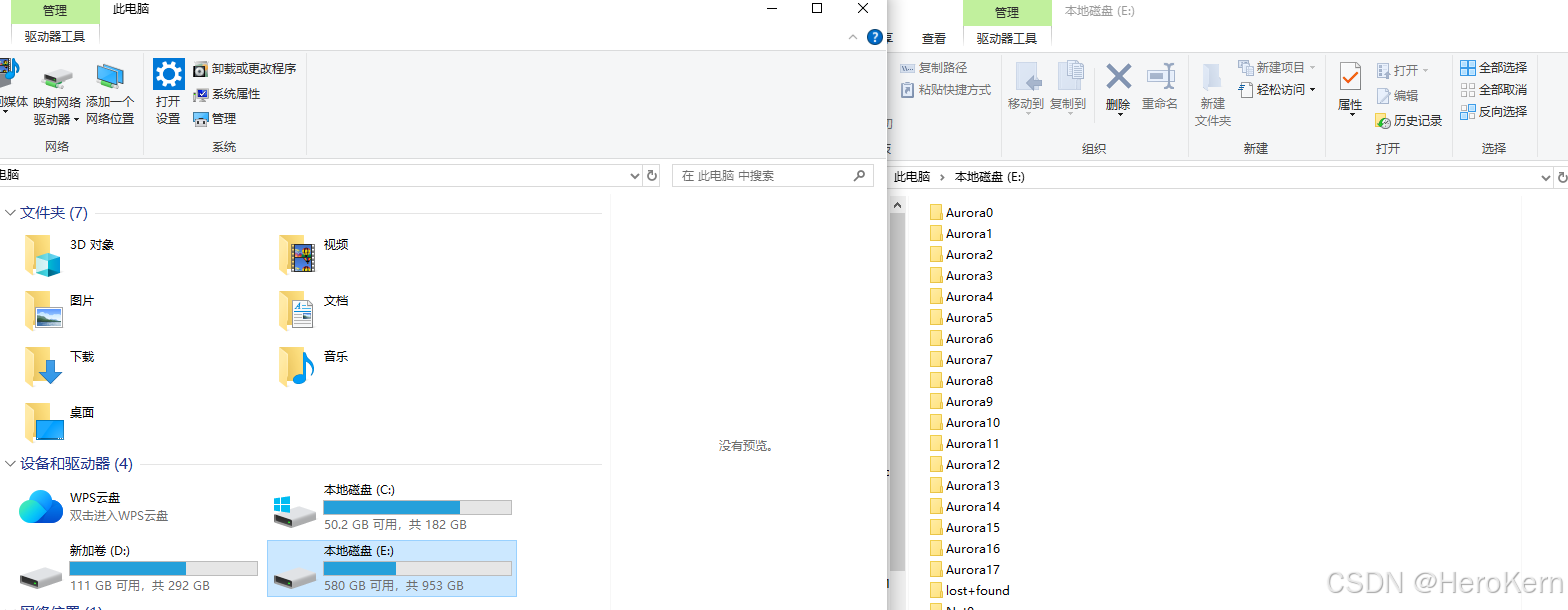

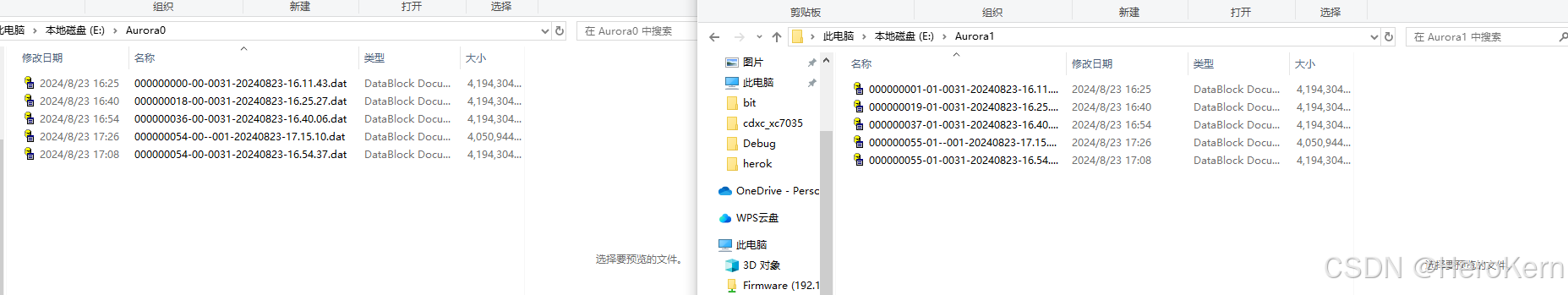

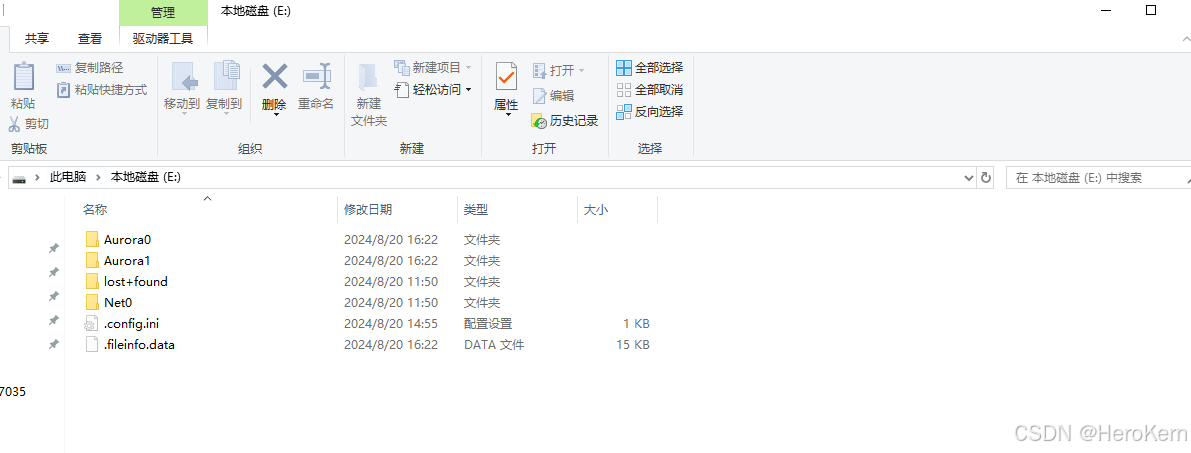

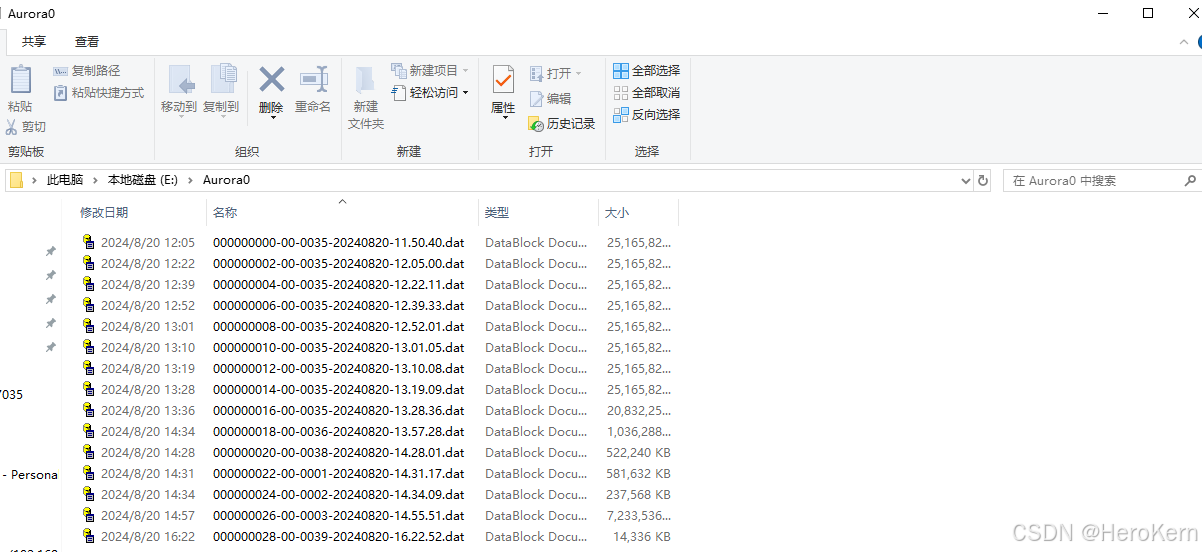

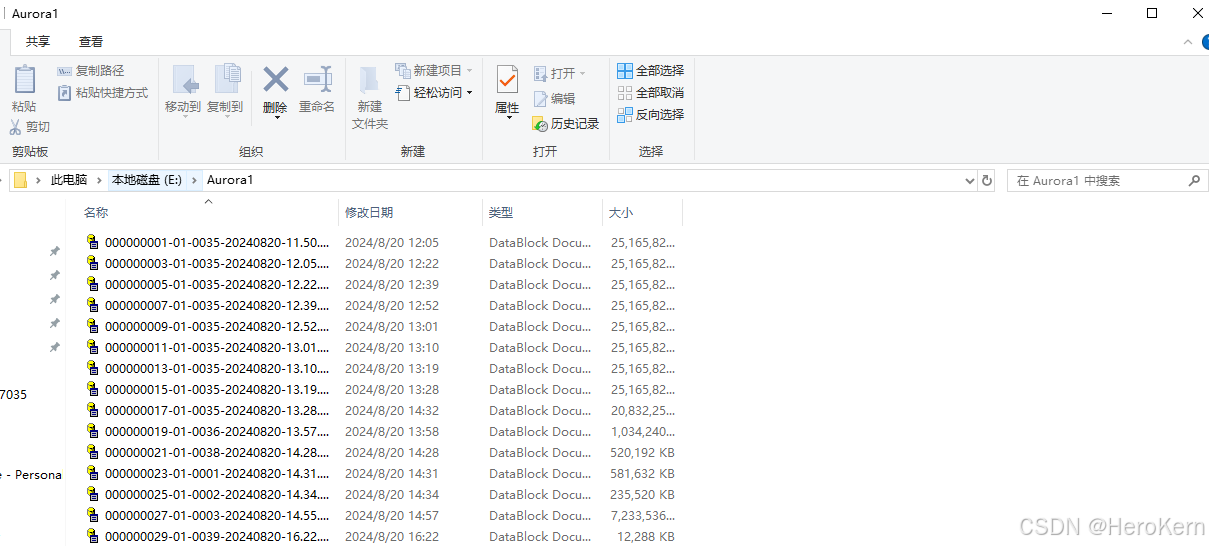

windows识别ext4目录

6.总结

按照本文方式处理,xc7z035处理器存储速率能够达到1.2GB/s。本方案设计比较简单,可移植性好,并且成本低,运行稳定,开发高效。速度测试结果如下图。

5个速度分别为:

- cpu data into ssd

- ssd data into cpu user

- ssd data into cpu kernel

- fpga data into ssd

- ssd data into fpga

可以清晰看到copy_to_user是非常耗时,所以对于CPU端数据卸载需要结合零拷贝技术

本文介绍了一种基于Xilinx Zynq的高速存储设计方案,利用NVMe SSD实现超过1.2GB/s的数据传输速率。该方案通过将ARM处理器与FPGA集成,在Zynq处理器上运行Linux,并使用PCIe接口连接至SSD,通过FPGA实现数据的快速缓存与写入。

本文介绍了一种基于Xilinx Zynq的高速存储设计方案,利用NVMe SSD实现超过1.2GB/s的数据传输速率。该方案通过将ARM处理器与FPGA集成,在Zynq处理器上运行Linux,并使用PCIe接口连接至SSD,通过FPGA实现数据的快速缓存与写入。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?