目录

1、状态机FSM

1.1 一段/二段/三段状态机对比

参考《如何写好状态机_Verilog_CH06_FSM》

一般来说,一段式代码长度会比两段式冗长大约80%到150%左右。所以一段式 FSM 描述是不推荐的FSM 描述方式,请读者一定要避免。为了使 FSM 描述清晰简介,易于维护,易于附加时序约束,使综合器和布局布线器更好的优化设计,推荐使用两段式FSM 描述方法。

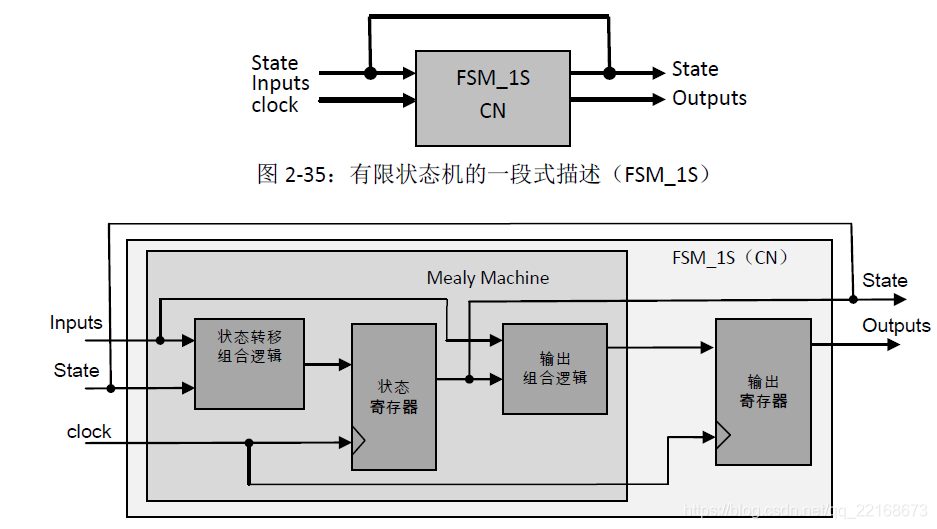

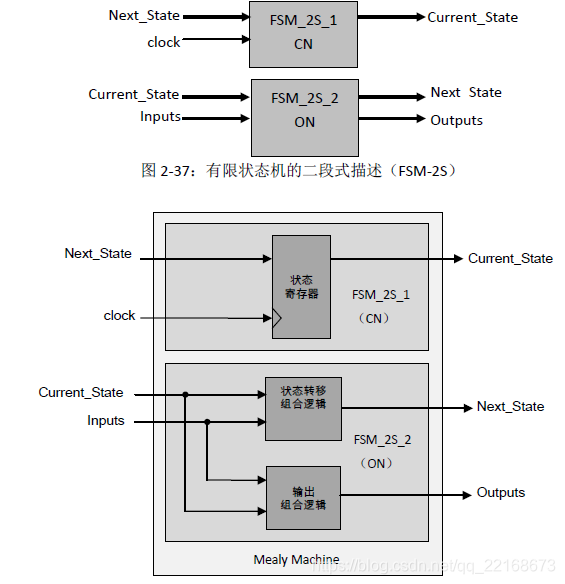

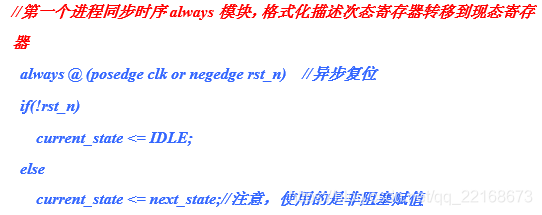

两段式写法:是推荐的 FSM 描述方法之一,在此我们仔细讨论一下代码结构。两段式FSM 的核心就是:一个always 模块采用同步时序描述状态转移;另一个模块采用组合逻辑判断状态转移条件,描述状态转移规律。两段式写法可以概括为图6-5 描述的结构。

本例中,同步时序描述状态转移的 always 模块代码如下:

always @ (posedge clk or negedge nrst)

if (!nrst)

CS <= IDLE;

else

CS <=NS;

其实这是一种程式化的描述结构,无论具体到何种 FSM 设计,都可以定义两个状态寄存器“CS”和“NS”,分别代表当前状态和下一状态,然后根据所需的复位方式(同步复位或异步复位),在时钟沿到达时将NS 赋给CS。需要注意的是这个同步时序模块的赋值要采用非阻塞赋值“<=”。

这个使用组合逻辑判断状态转移条件的 always 模块也可以看成格式化的书写结构。其中always 的敏感列表为当前状态“CS”,复位信号和输入条件(如果是米勒状态机,则必须有输入条件;如果是摩尔状态机,一般敏感表和后续逻辑判定没有输入),请大家注意电平敏感表必须列完整。

组合逻辑容易产生毛刺,因此如果时序允许,请尽量对组合逻辑的输出插入一个寄存器节拍,这样可以很好的保证输出信号的稳定性。

三段式FSM:

两段式 FSM 描述方法虽然有很多好处,但是它有一个明显的弱点就是其输出一般使用组合逻辑描述,而组合逻辑易产生毛刺等不稳定因素,并且在FPGA/CPLD 等逻辑器件中过多的组合逻辑会影响实现的速率(这点与ASIC 设计不同)。所以在上节我们特别提到了在两段式FSM 描述方法中,如果时序允许插入一个额外的时钟节拍,则尽量在在后级电路对FSM 的组合逻辑输出用寄存器寄存一个节拍,则可以有效地消除毛刺。但是很多情况下,设计并不允许额外的节拍插入(Latency),此时,解决之道就是采用3 段式FSM 描述方法。三段式描述方法与两段式描述方法相比,关键在于使用同步时序逻辑寄存FSM的输出。

三段式描述方法与两段式描述相比,虽然代码结构复杂了一些,但是换来的优势是使FSM 做到了同步寄存器输出,消除了组合逻辑输出的不稳定与毛刺的隐患,而且更利于时序路径分组,一般来说在FPGA/CPLD 等可编程逻辑器件上的综合与布局布线效果更佳。

FSM 的编码:

Binary(二进制编码)、gray-code(格雷码)编码使用最少的触发器,较多的组合逻辑,而one-hot(独热码)编码反之。one-hot 编码的最大优势在于状态比较时仅仅需要比较一个bit,一定程度上从而简化了比较逻辑,减少了毛刺产生的概率。由于CPLD 更多地提供组合逻辑资源,而FPGA 更多地提供触发器资源,所以CPLD 多使用gray-code,而FPGA 多使用one-hot 编码。另一方面,对于小型设计使用gray-code 和binary 编码更有效,而大型状态机使用one-hot 更高效。

1.2 FSM

一段/二段/三段FSM都可以描述为米利机,或者描述为摩尔机。

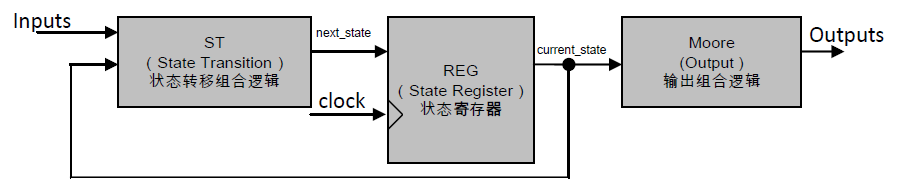

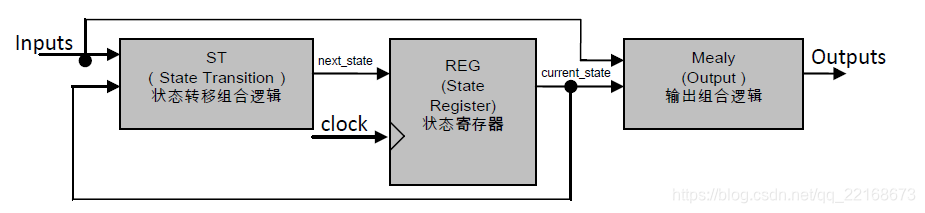

1.2.1 摩尔机(Moore Machine)

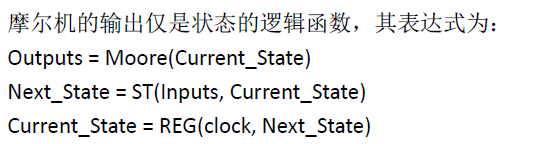

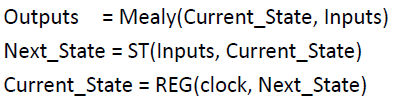

1.2.2 米利机(Mealy Machine)

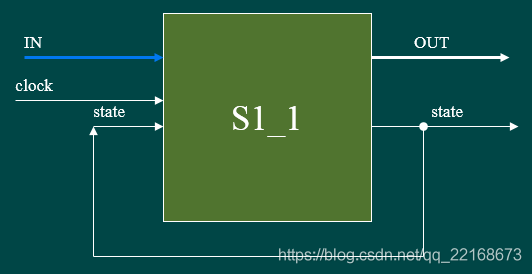

1.2.3 一段式状态机(时钟闭节点机器)

在同一个always块中编写

输出为同步信号,既时钟闭节点,因此务必使用posedge clock为敏感信号

由于输出state为同步信号,因此state可以闭合,满足一个时钟后响应的要求

一段式在一个行为语句块中,包括全部的摩尔机结构或者米利机结构,即包含了状态转移逻辑、状态寄存器逻辑和输出逻辑。

1.2.4 二段式状态机(时钟开节点机器)

用两个always分别描述S2_1和S2_2

S2_1输出current_state为同步信号,要求posedge clock为敏感信号

S2_2为组合逻辑,输出的Out为非同步信号,既时钟开节点机器(要求Out下游插入寄存器)

二段式中,第一个行为语句块包括状态寄存器的捕获,第二个行为语句块包含转移组合逻辑和输出组合逻辑。

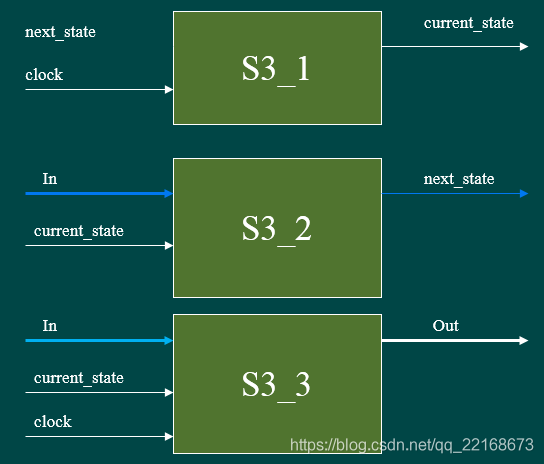

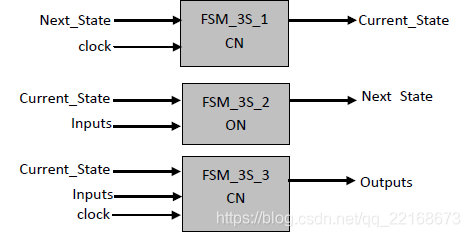

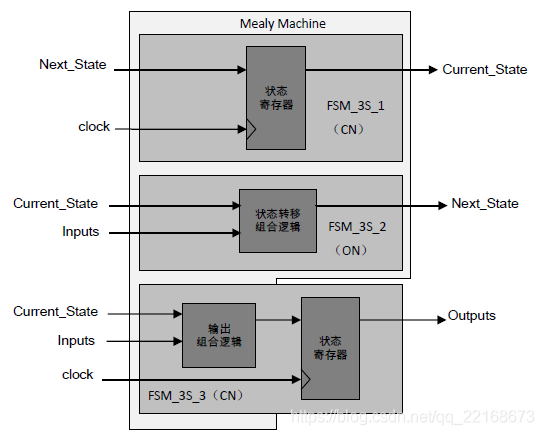

1.2.5 三段式状态机(时钟闭节点机器)

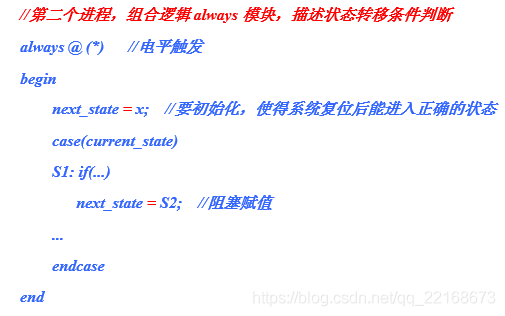

用三个always分别描述S3_1和S3_2和S3_3

S3_1输出current_state为同步信号,要求posedge clock为敏感信号

S2_2为组合逻辑,输出的next_state为非同步信号

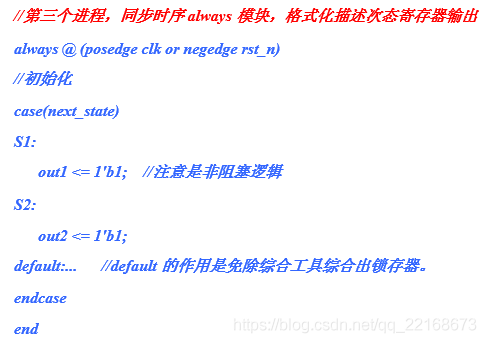

S3_3输出Out为同步信号,要求posedge clock为敏感信号

三段式中,第一个行为语句块包含状态寄存器的捕获,第二个行为语句块仅有状态转移的描述,第三个语句块仅有输出逻辑

2、状态机实践

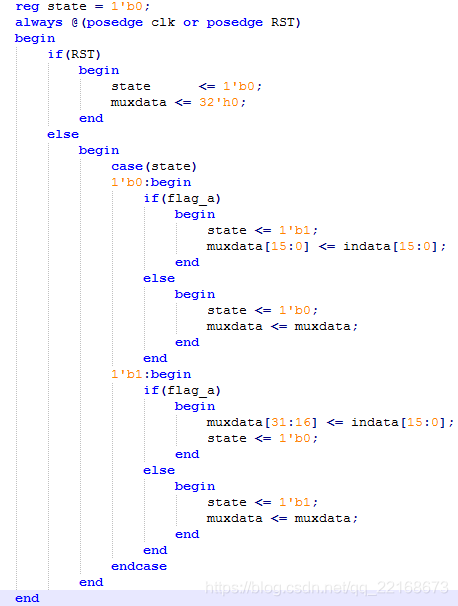

2.1一段式状态机

下图是一个简单的一段式状态机举例,用于数据高低位拼接。

2.2两段式状态机

2.3三段式状态机

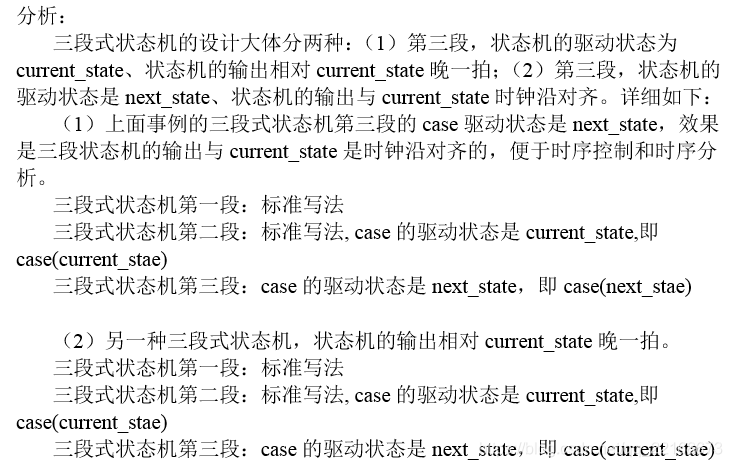

下面是三段式状态机的一种推荐写法

在状态机第3段中,

若case(current_state),优势是时序好,不足是输出相对current_state慢1拍;

若case(next_state),优势是输出相对current_state是同步对齐的关系,不足是这种方式的时序不是特别好。

参考博文

| 作者 | 博文 |

| 有限狀態機FSM coding style整理 (SOC) (Verilog) | |

1520

1520

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?