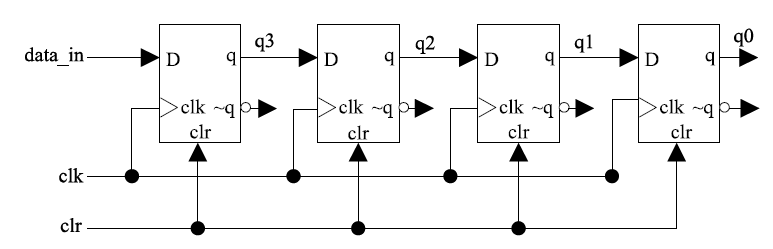

原理图:

Implementation part:

module ShiftRegister(q3,data_in,clk,clr);

output[3:0] q3;

input[3:0] data_in;

input clk;

input clr;

reg[3:0] q3,q2,q1,q0;

always@(posedge clk or posedge clr)

if (clr == 1)

begin

q3 <= 0;

q2 <= 0;

q1 <= 0;

q0 <= 0;

end

else

begin

q3<=q2;

q2<=q1;

q1<=q0;

q0<=data_in;

end

endmoduleSimulation part:

module ShiftRegisterTest5;

// Inputs

reg [3:0] data_in;

reg clk;

reg clr;

// Outputs

wire [3:0] q3;

// Instantiate the Unit Under Test (UUT)

ShiftRegister uut (

.q3(q3),

.data_in(data_in),

.clk(clk),

.clr(clr)

);

initial begin

// Initialize Inputs

data_in = 4'b0001;

#1 clr = 1'b0;

#1 clk=1'b1;

end

always begin

#3 clk = ~clk;

#5 data_in = data_in + 4'b0001;

end

endmodule

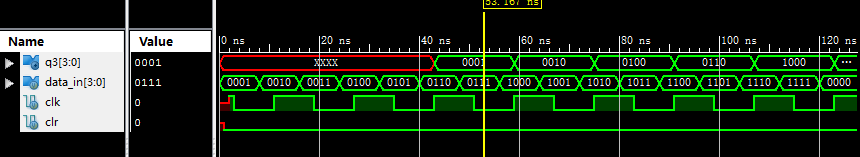

Simulation part:

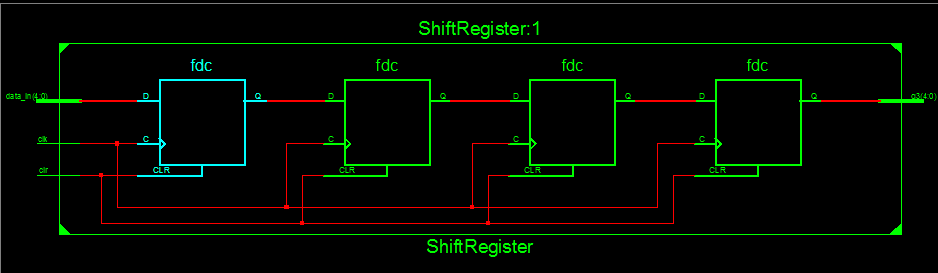

RTL Schematic:

总感觉应该是哪里做错了,以后检查一下QAQ

顺序好像和原理图相反,自己改改吧。

2632

2632

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?