弄完了梅老师的verilog例程,想要改成VHDL,做如下记录:

8位数据转16位源码

----------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 16:55:08 04/09/2018

-- Design Name:

-- Module Name: cmos_8bit_to_16bit - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

-- Uncomment the following librarydeclaration if using

-- arithmetic functions with Signed orUnsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following librarydeclaration if instantiating

-- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity cmos_8bit_to_16bit is

Port( rst :in STD_LOGIC;

clk :in STD_LOGIC; --cmoscamera pixclk

pdata_i :in STD_LOGIC_VECTOR (7 downto 0);--cmoscamera ouput 8bit data

de_i :in STD_LOGIC; --cmoscamera output a enable signal(HREF)

de_v_i :in STD_LOGIC; --cmoscamera output VSYNC

pdata_o :out STD_LOGIC_VECTOR (15 downto 0);

hblank :out STD_LOGIC;

de_o :out STD_LOGIC;

de_v_o :out STD_LOGIC);

end cmos_8bit_to_16bit;

architecture Behavioral ofcmos_8bit_to_16bit is

signalcnt :STD_LOGIC;

signalpdata_i_d0 :STD_LOGIC_VECTOR (7 downto 0);

begin

process(rst,clk)

begin

if('1' = rst) then

cnt<= '0';

elsif(rising_edge(clk)) then

if('1' = de_i) then

cnt<= NOT cnt;

else

cnt<= '0';

endif;

endif;

endprocess;

process(clk)

begin

if('1' = de_i AND '1' = cnt) then

de_o<= '1';

else

de_o<= '0';

endif;

endprocess;

process(clk)

begin

if(rising_edge(clk)) then

de_v_o<= de_v_i;

endif;

endprocess;

process(clk)

begin

if(rising_edge(clk)) then

pdata_i_d0<= pdata_i;

endif;

endprocess;

process(clk,rst)

begin

if('1' = rst) then

pdata_o<= (others=>'0');

elsif('1'= de_i AND '1' = cnt) then

pdata_o<= pdata_i_d0&pdata_i;

else

pdata_o<= (others=>'1');

endif;

endprocess;

end Behavioral;

仿真文件

--------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 15:27:38 04/27/2018

-- Design Name:

-- Module Name: E:/XilinxDic/ov7670_VHDL/ov7670/src/cmos8to16test.vhd

-- Project Name: ov7670

-- Target Device:

-- Tool versions:

-- Description:

--

-- VHDL Test Bench Created by ISE formodule: cmos_8bit_to_16bit

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

-- Notes:

-- This testbench has been automaticallygenerated using types std_logic and

-- std_logic_vector for the ports of theunit under test. Xilinx recommends

-- that these types always be used for thetop-level I/O of a design in order

-- to guarantee that the testbench willbind correctly to the post-implementation

-- simulation model.

--------------------------------------------------------------------------------

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

-- Uncomment the following librarydeclaration if using

-- arithmetic functions with Signed orUnsigned values

--USE ieee.numeric_std.ALL;

ENTITY cmos8to16test IS

END cmos8to16test;

ARCHITECTURE behavior OF cmos8to16test IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT cmos_8bit_to_16bit

PORT(

rst : IN std_logic;

clk : IN std_logic;

pdata_i : IN std_logic_vector(7downto 0);

de_i : IN std_logic;

de_v_i : IN std_logic;

pdata_o : OUT std_logic_vector(15downto 0);

hblank : OUT std_logic;

de_o : OUT std_logic;

de_v_o : OUT std_logic

);

END COMPONENT;

--Inputs

signal rst : std_logic := '0';

signal clk : std_logic := '0';

signal pdata_i : std_logic_vector(7 downto 0) := (others => '0');

signal de_i : std_logic := '0';

signal de_v_i : std_logic := '0';

--Outputs

signal pdata_o : std_logic_vector(15 downto 0);

signal hblank : std_logic;

signal de_o : std_logic;

signal de_v_o : std_logic;

--Clock period definitions

constant clk_period : time := 10 ns;

BEGIN

--Instantiate the Unit Under Test (UUT)

uut: cmos_8bit_to_16bit PORT MAP (

rst => rst,

clk => clk,

pdata_i => pdata_i,

de_i => de_i,

de_v_i => de_v_i,

pdata_o => pdata_o,

hblank => hblank,

de_o => de_o,

de_v_o => de_v_o

);

--Clock process definitions

clk_process :process

begin

clk<= '0';

waitfor clk_period/2;

clk<= '1';

waitfor clk_period/2;

end process;

--Stimulus process

stim_proc: process

begin

-- hold reset state for 100 ns.

wait for clk_period*1;

rst<= '1';

waitfor clk_period*3;

rst<= '0';

de_i<= '0';

de_v_i<= '0';

waitfor clk_period*3;

de_i<= '1';

pdata_i<= b"0101_0101";

waitfor clk_period;

pdata_i<= b"1100_0011";

waitfor clk_period;

pdata_i<= b"0011_1100";

waitfor clk_period;

pdata_i<= b"1100_0011";

waitfor clk_period*2;

de_i<= '0';

wait;

-- insert stimulus here

end process;

END;

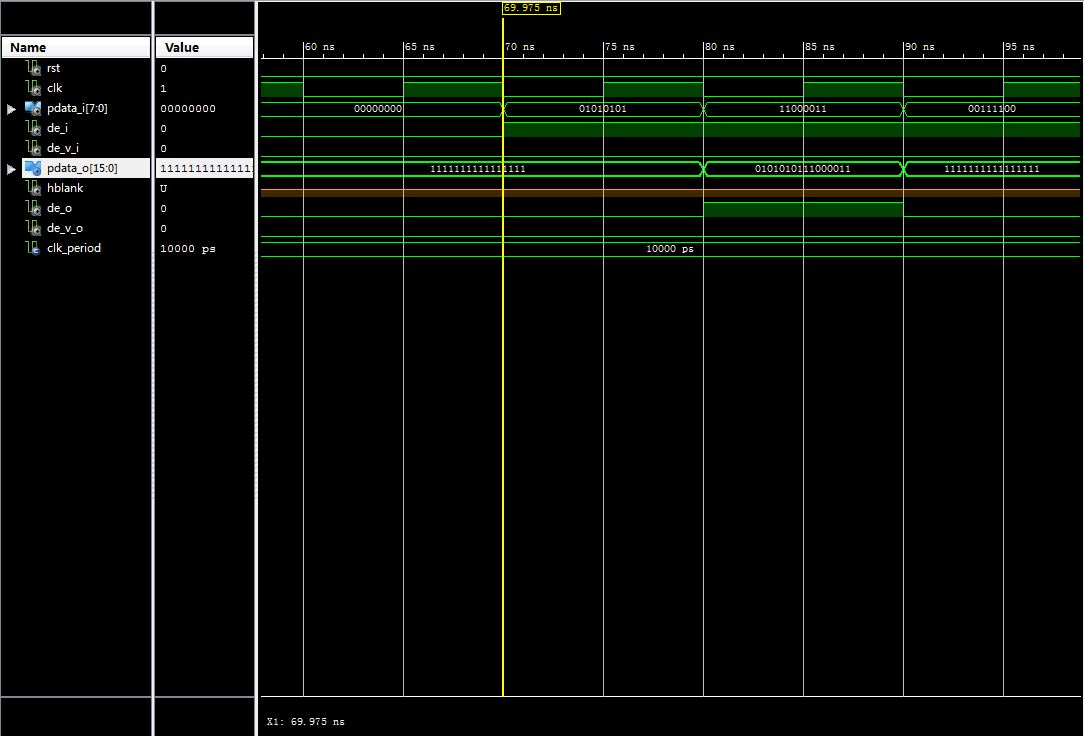

时序图

1471

1471

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?