zynq-PS知识点一 修改PS. IP核、生成HDF和helloworld小系统)

- 1 概述

- 最小系统

- 创建block design

- ZYNQ7 Prosscessing System

- DDR存储器配置

- UART外设添加

- UART电压检查

- BANK电压检查

- 配置PS时钟

- 验证设计

- 生成顶层(.HDF)硬件描述文件

- Vivado SDK工具使用

- Vivado hello world

- 下载工程代码

1 概述

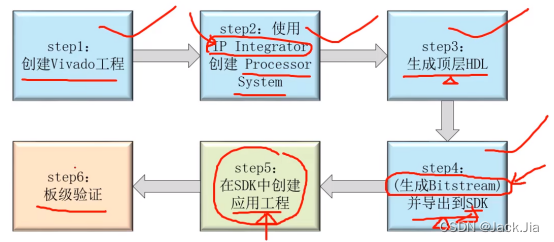

嵌入式开发流程

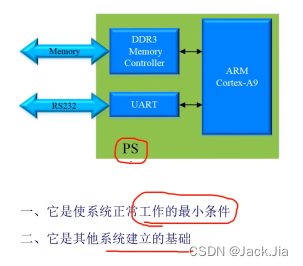

最小系统

只有PS部分

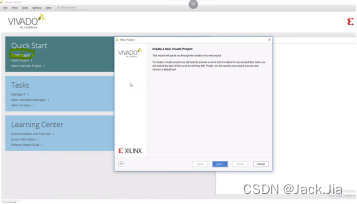

创建vivado工程

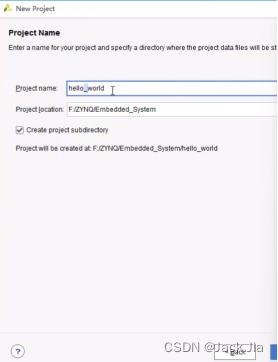

并修改工程名称、路径

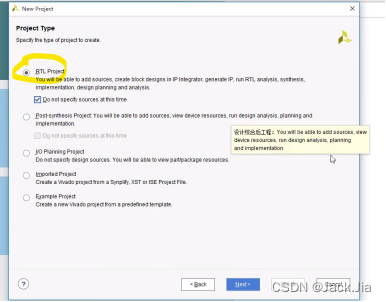

选择RTL工程

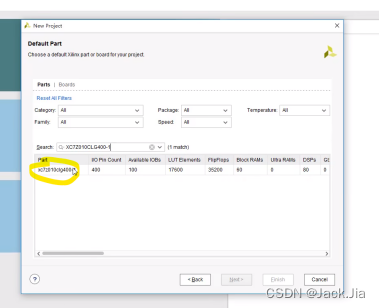

7010核心板 选择Zynq型号 XC7Z010CLG400-1

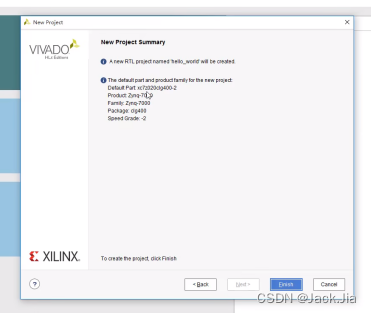

查看summary部分内容

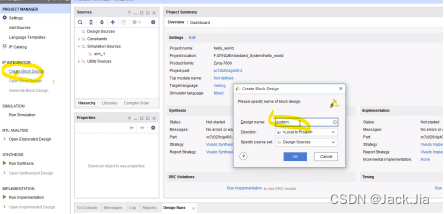

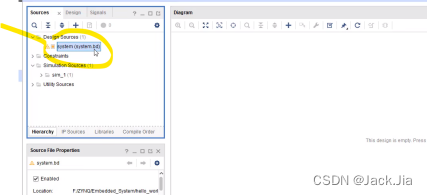

创建block design

即创建一个模块化设计

查看,system.bd

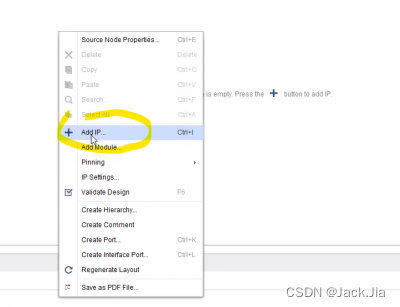

右键添加IP

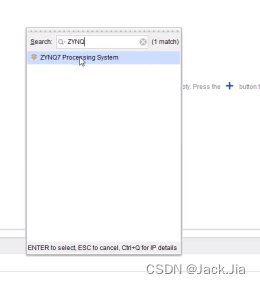

搜索关键词ZYNQ, 双击打开

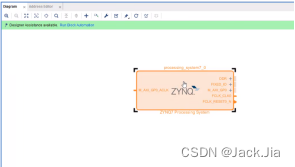

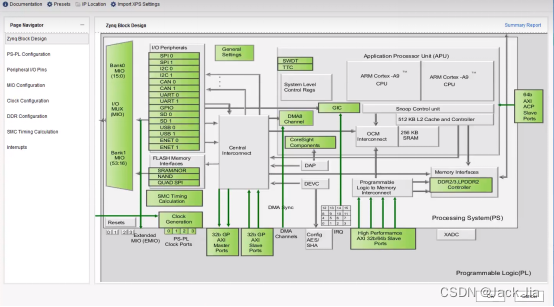

查看PS模块示意图

ZYNQ7 Prosscessing System

DDR

Fixed_IO

M_AXI_GP0

FCLK_CLK0 (是PS给PL提供的时钟信号)

FCLK_RESET0_N

M_AXI_GP0_ACLK (是M_AXI_GP0的时钟信号)

外设并未在上面的图片展示。

双击PS模块之后,可以查看到内部结构:

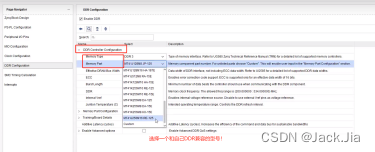

DDR存储器配置

选择一个与自己DDR兼容的型号!

MT41256M16-RE125

解析:

MT 美光

16 数据位宽16bit

容量256M * 16 = 4096M = 4Gbit

如果用来2块ddr3,则4G*2 = 8Gbit

因为用了2块16bit数据位宽的DDR,所以一下有效数据位宽选择32bit

以上DDR就配置ok了。

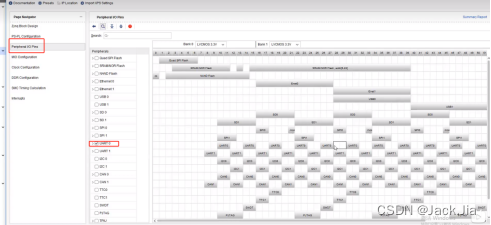

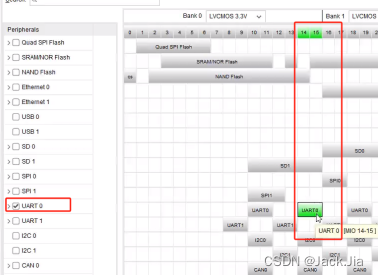

UART外设添加

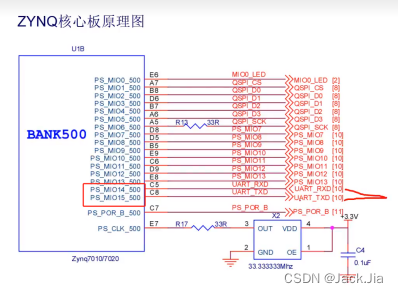

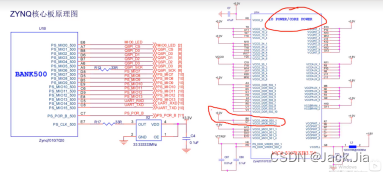

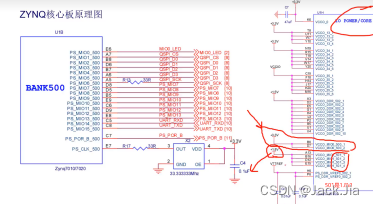

根据硬件原理图查找io对应关系

PS_MIO14 RX

PS_MIO15 TX

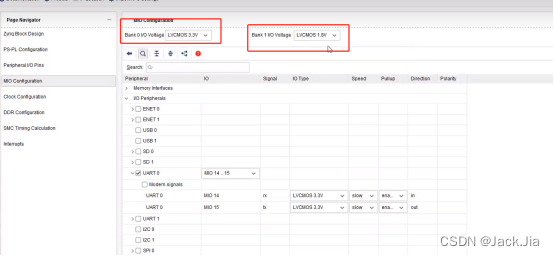

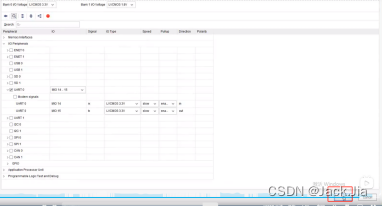

选择相应MIO

MIO选择也可以在MIO Configuration中选择,

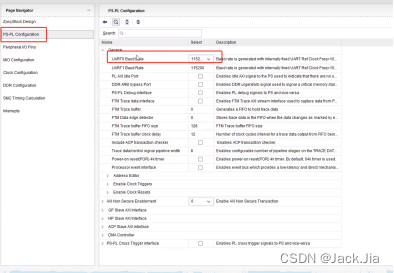

配置uart0的波特率

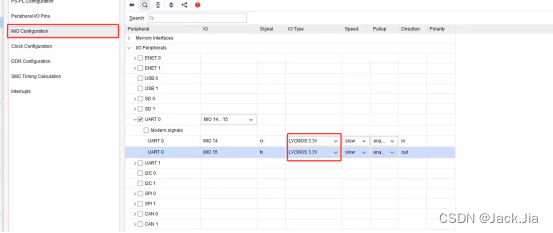

UART电压检查

BANK电压检查

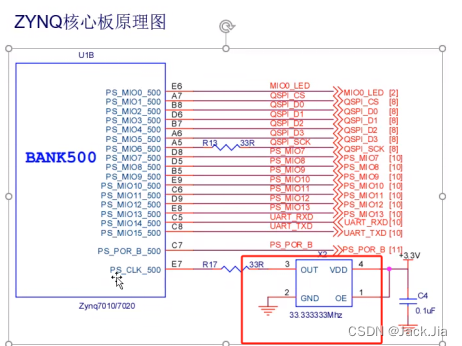

Bank500是3.3V

Bank501是1.8V

最终配置如下

配置完成后点击ok

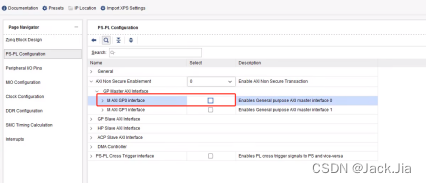

如果不需要M_AXI_GP0,则取消如下选项

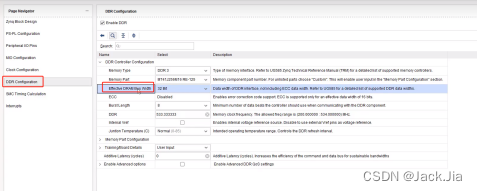

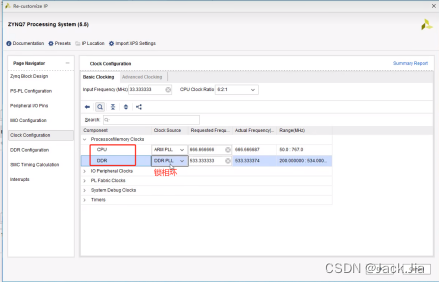

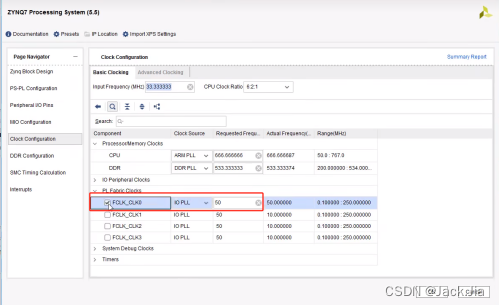

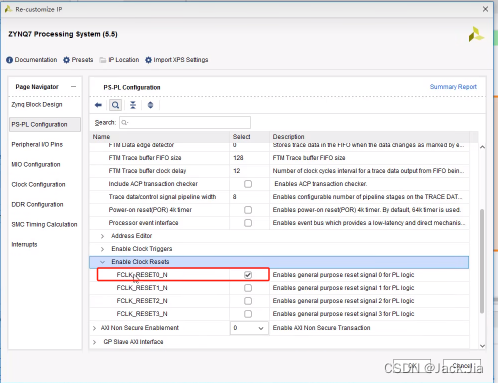

配置PS时钟

查看原理图,查找 输入(源时钟)PS_CLK_500时钟频率:33.333333Mhz

CPU时钟

DDR时钟

如果不需要PL,则取消勾 选FCLK_CLK0

如果不需要PS对PL的复位信号,则取消勾 选FCLK_RESET0_N

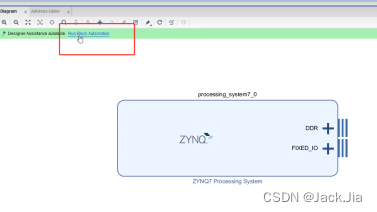

最终得到最小系统如下:

点击RUN BLOCK AUTOMATION,自动创建模块端口。

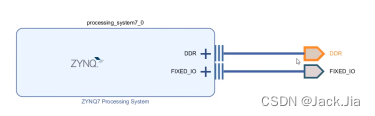

创建完成,如下:

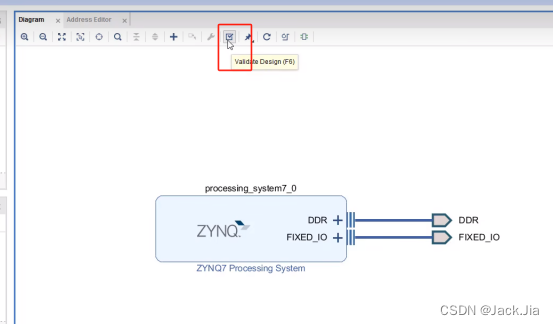

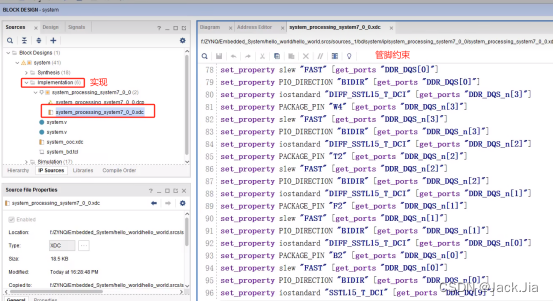

验证设计

如下:

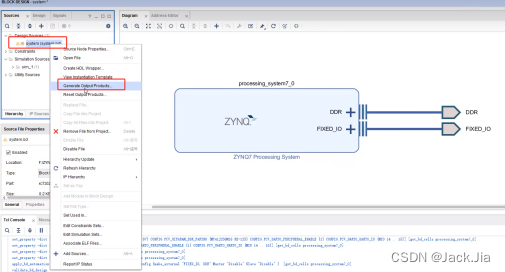

生成输出结果,如下:

选择默认选项,IP核独立进行输出;

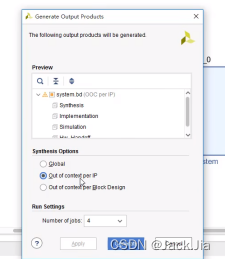

生成结果:

综合

实现

仿真

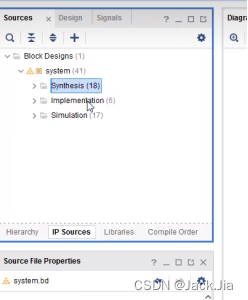

管脚分配约束如下:

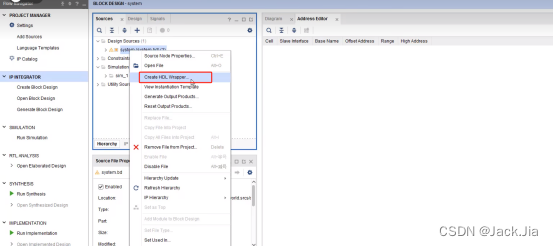

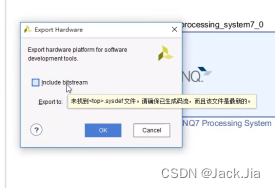

生成顶层(.HDF)硬件描述文件

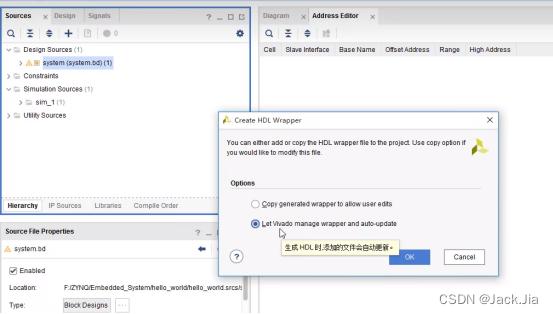

选择默认选项,如下:

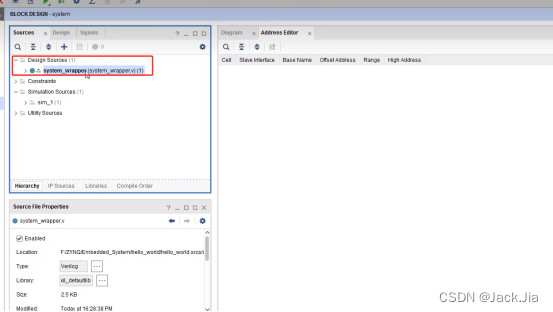

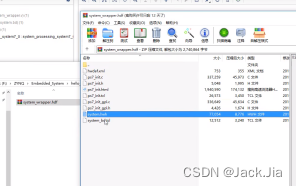

生成system_wrapper, 内容是顶层fpga代码

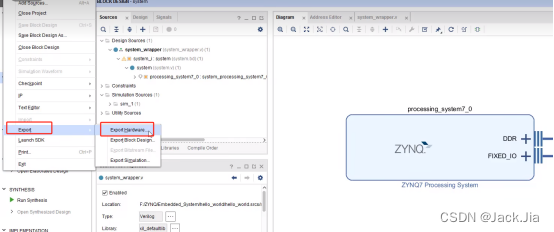

导出硬件描述文件

是否包含PL bit,如果需要选择上

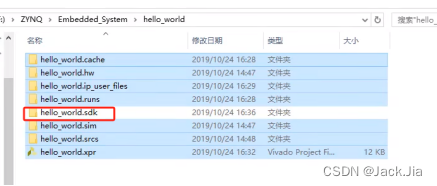

生成文件目录

可以用解压缩文件,解压查看

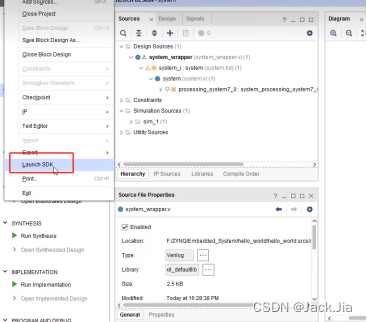

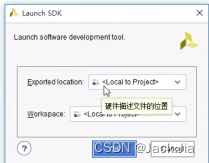

Vivado SDK工具使用

启动软件开发工具

保持为当前工程路径

启动sdk

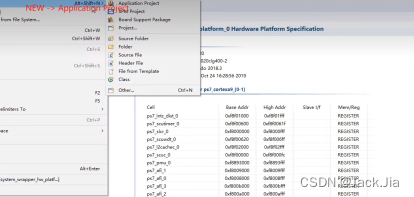

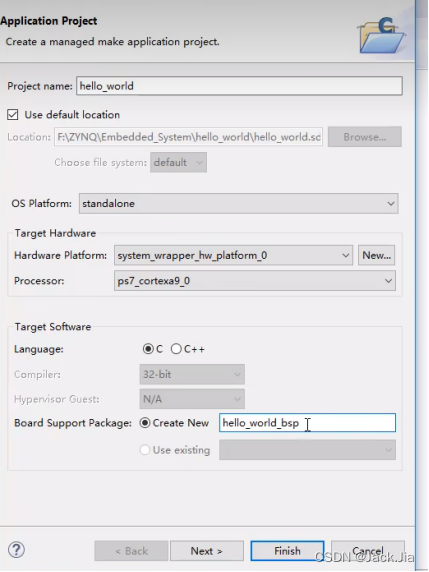

创建sdk工程

设置工程名称

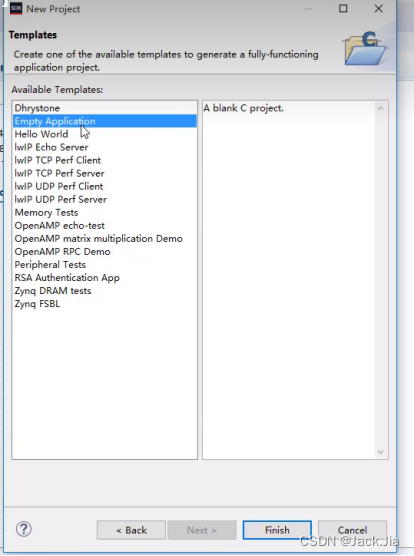

选择空的工程模板

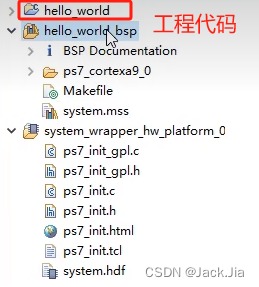

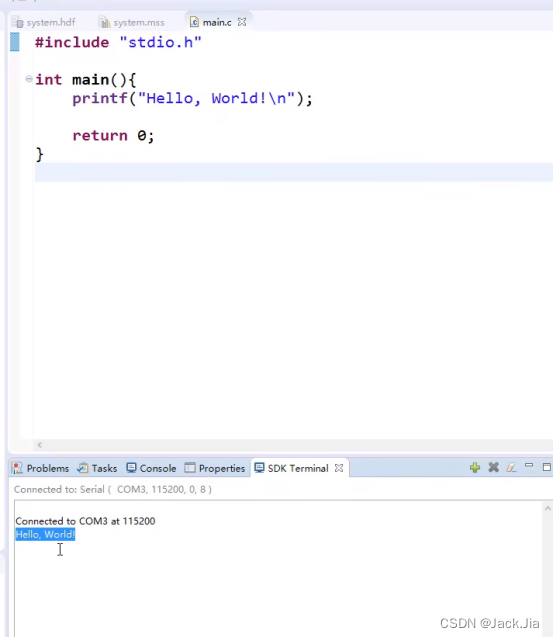

Vivado hello world

创建生成的代码, 如下

第一个是软件应用,

第二个是bsp是硬件和软件应用中间的支持包.

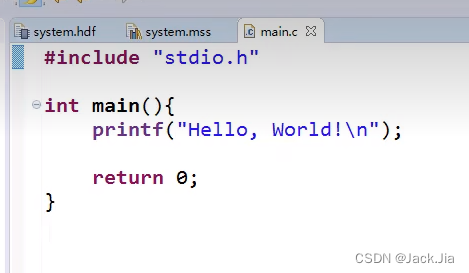

创建main函数

串口打印添加

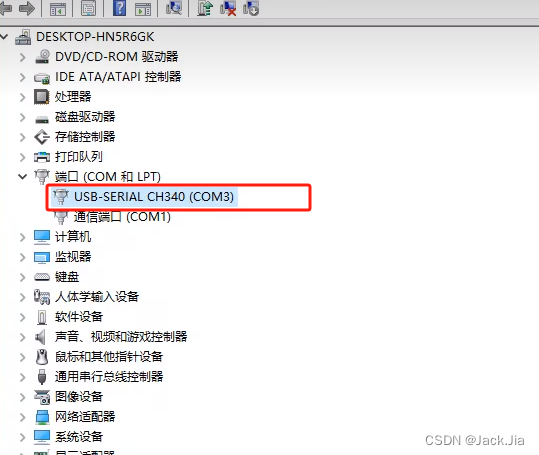

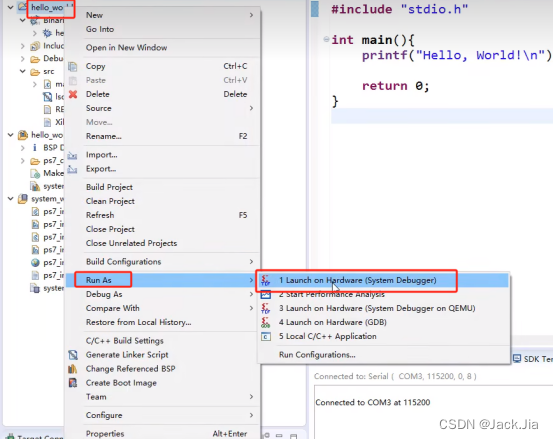

下载工程代码

下载验证,如下:

感谢阅读,祝君成功!

-by aiziyou

7868

7868

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?