寄存器实验

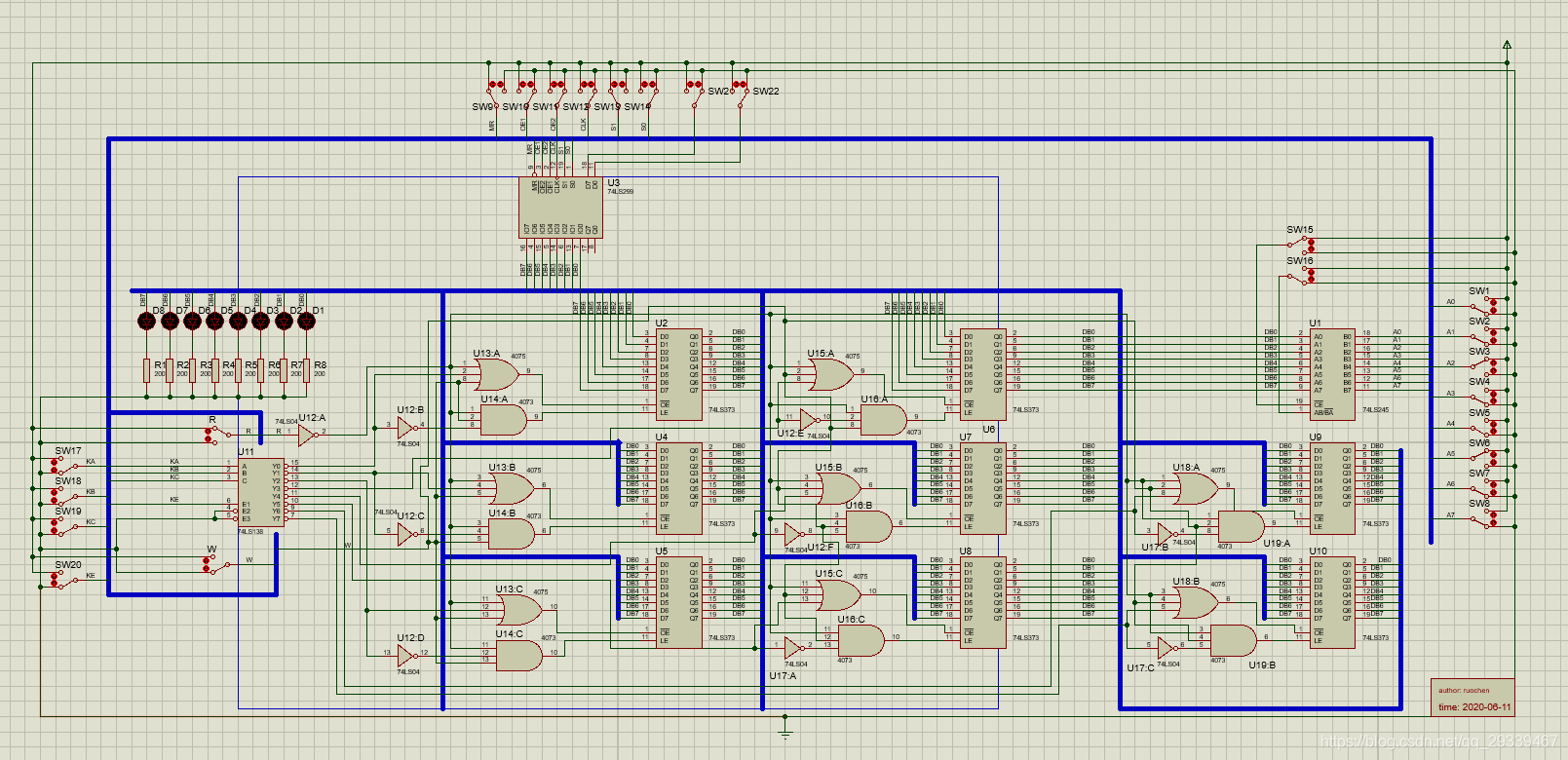

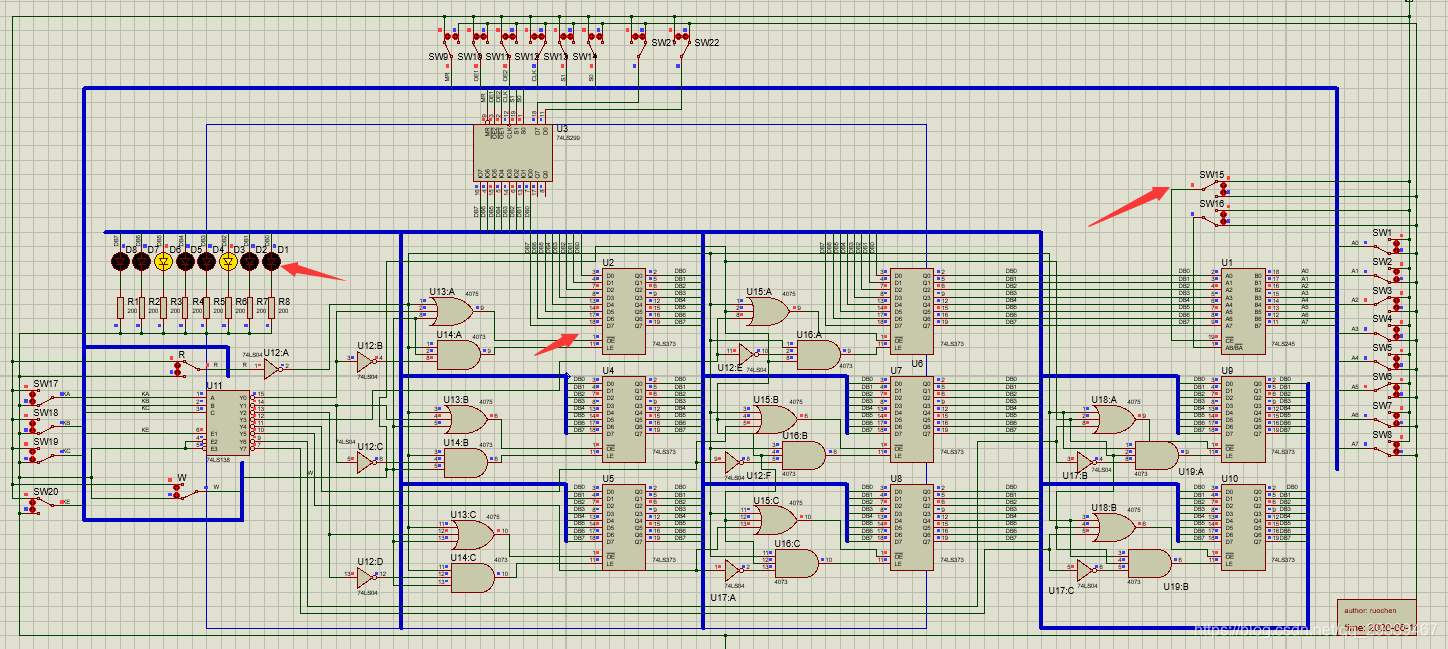

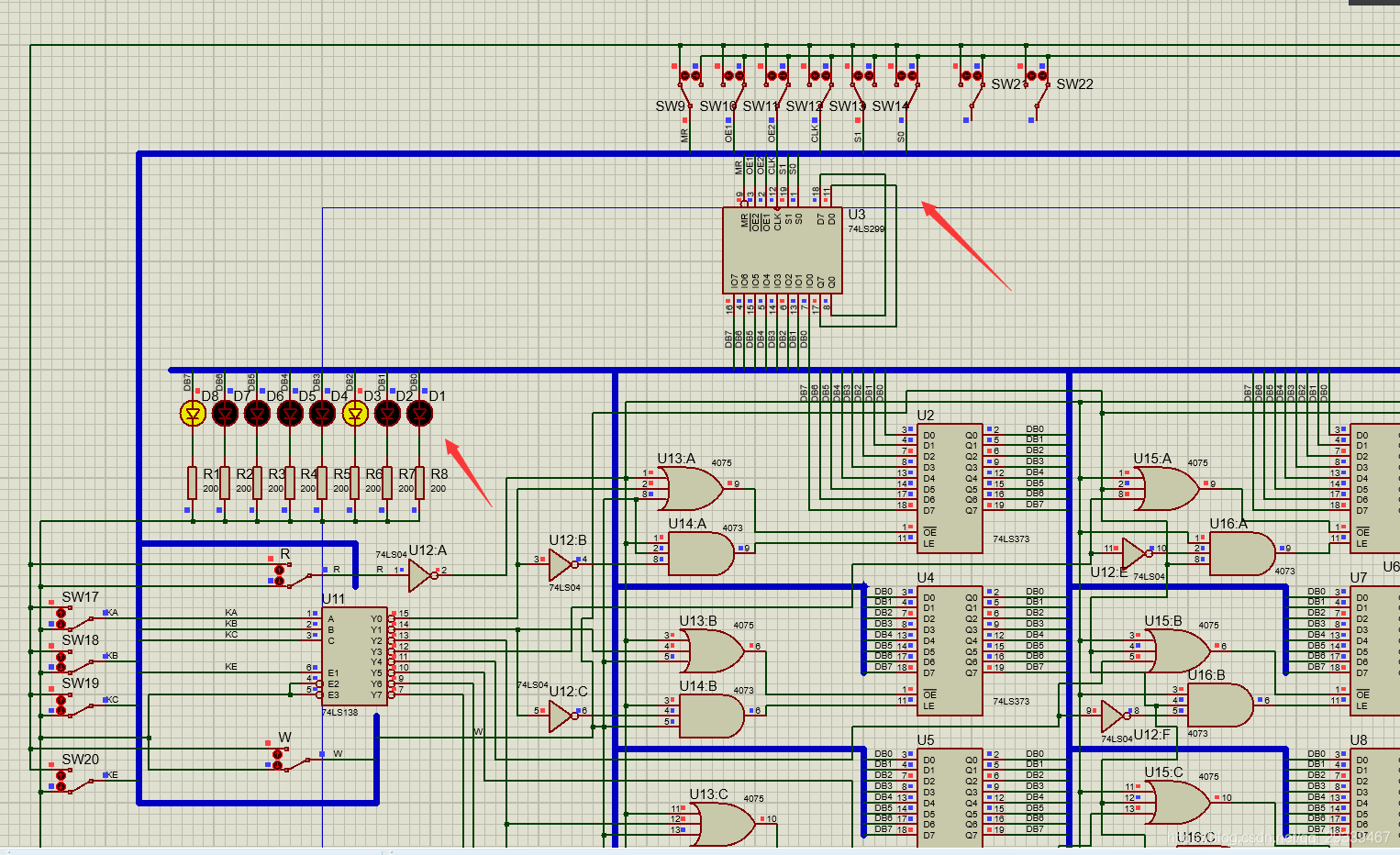

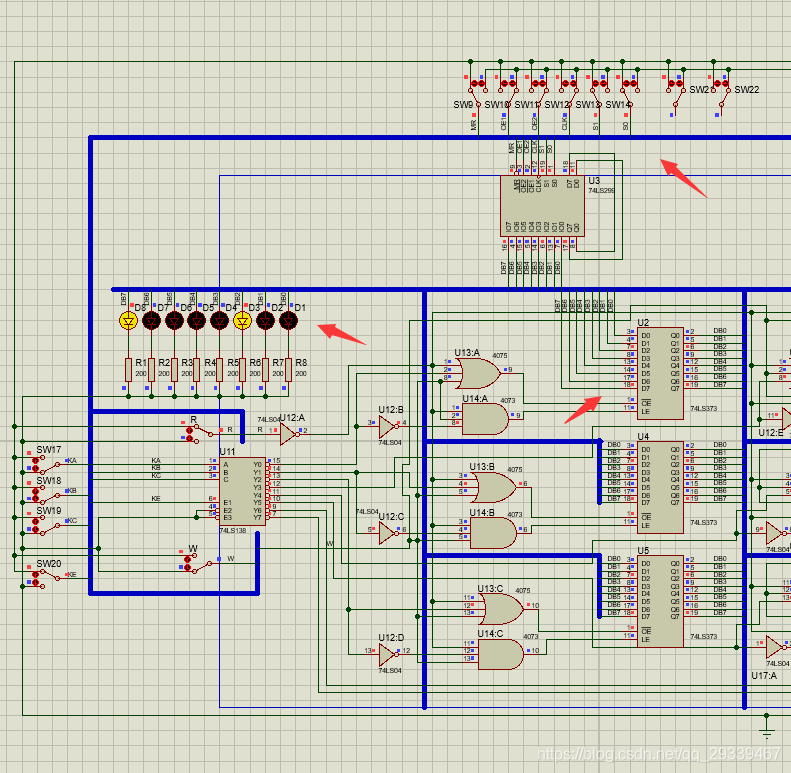

先放一张 Proteus 总体仿真图,设计过程还是比较复杂的,需要考虑总体的布局,线路的排布等等。。。

我将原工程文件放在文末,需要可自取

实验要求

- 基本要求

- 理解CPU运算器中寄存器的作用

- 设计并验证寄存器组(至少四个寄存器)

- 利用寄存器或组合逻辑电路实现移位运算功能(至少含左移、右移、循环左移、循环右移四种运算功能)

- 扩展要求

- 实现更多的寄存器

- 实现多总线结构寄存器访问

分析

-

实验要求设计验证寄存器,还有实现移位功能,扩展功能是使用多总线结构和更多寄存器,这里我使用双总线结构,八个寄存器。

-

实验中用到的元器件如下

- 74LS373(寄存器)

- 74LS299(通用移位/存储寄存器)

- 74LS138(译码器,用来控制八个寄存器)

- 74LS245(数据传送)

- SW-SPDT(单刀双掷开关)

- LED(用来显示输出)

- RES(LED下拉电阻)

- 4073(与门)

- 4075(或门)

- 74LS04(非门)

-

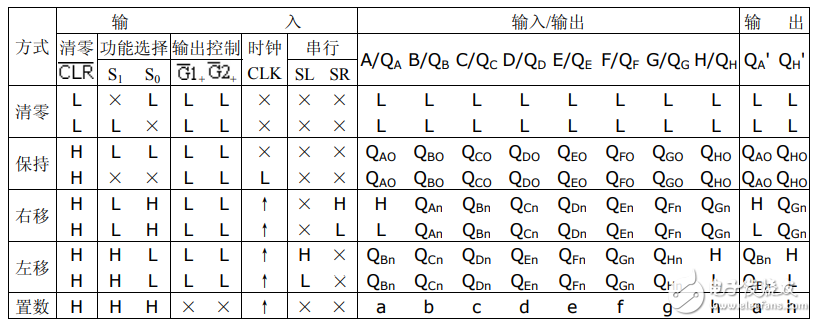

74LS299 功能表如下

- 其功能被表引脚与Proteus元器件有些许不同

- CLR 对应 MR(低电平有效)

- 不管任何状态,强制清零

- 输出控制 G1、G2对应 OE1、OE2(低电平有效)

- 需要输出时,将这两个引脚置0

- CLK

- 脉冲信号

- 查看功能表即可,需要上升沿时,就将开关拨高再拨低

- D7、D0

- 下一位移位的数

- Q7、Q0

- 保存最高位和最低位

- CLR 对应 MR(低电平有效)

- 其功能被表引脚与Proteus元器件有些许不同

-

其他元器件的使用自行百度即可

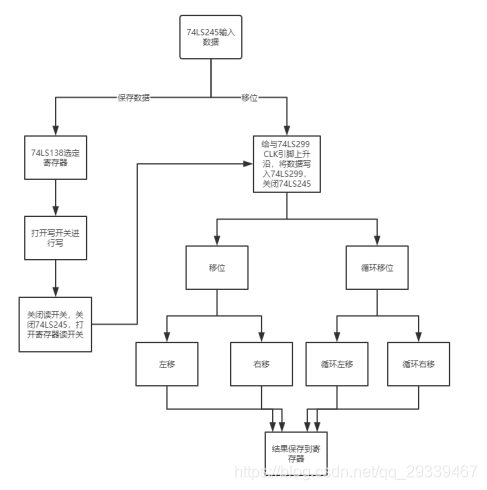

设计

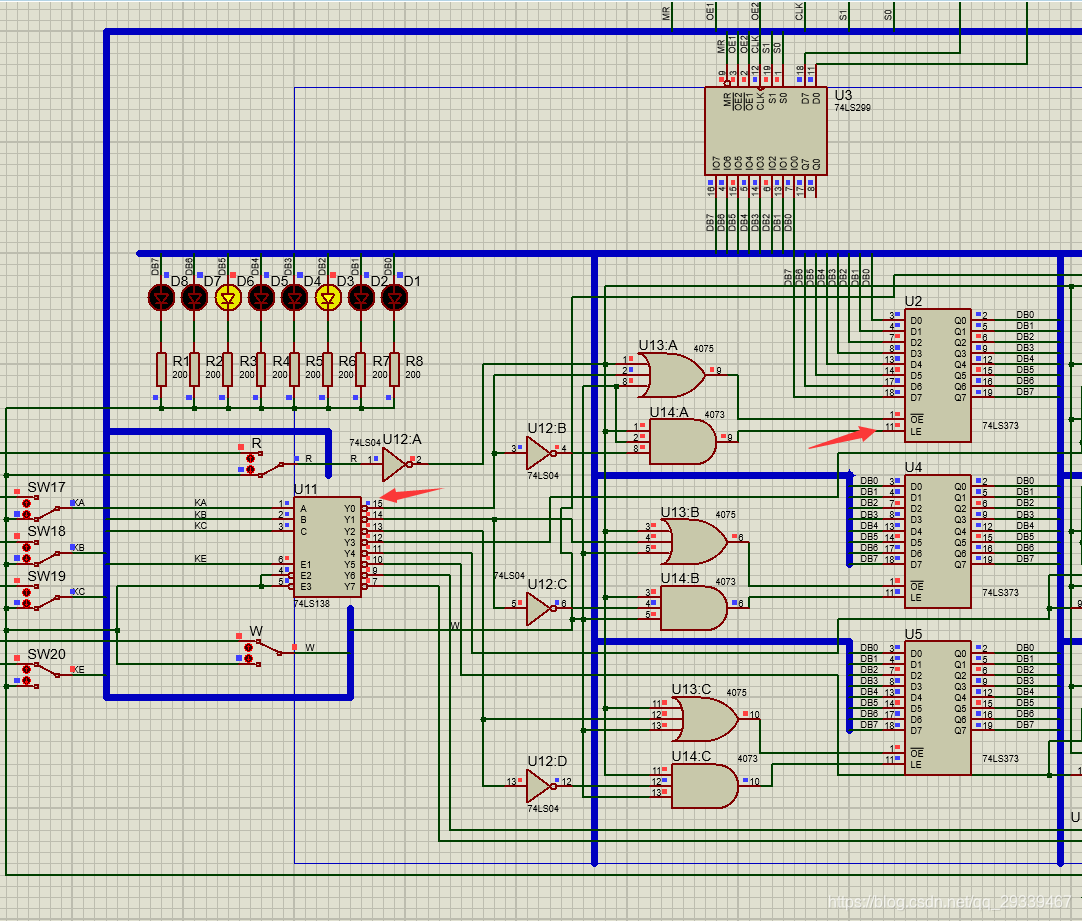

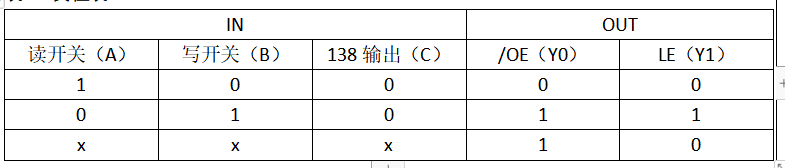

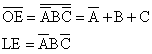

这里说一下怎么使用 74LS138 和门电路组合实现控制八个 74LS373

- 我们使用 74LS138 的输出和 两个开关(一个读开关、一个写开关)作为输入,因为我们实现能够 同时控制 74SL373 的读/写

- 对应的输出就是 74LS373 的读和写

- 可得到如下真值表

- 对应表达式如下

- 最后根据表达式进行连线即可

- 运行流程图如下

- 电路设计可根据下述操作慢慢理解

具体实现

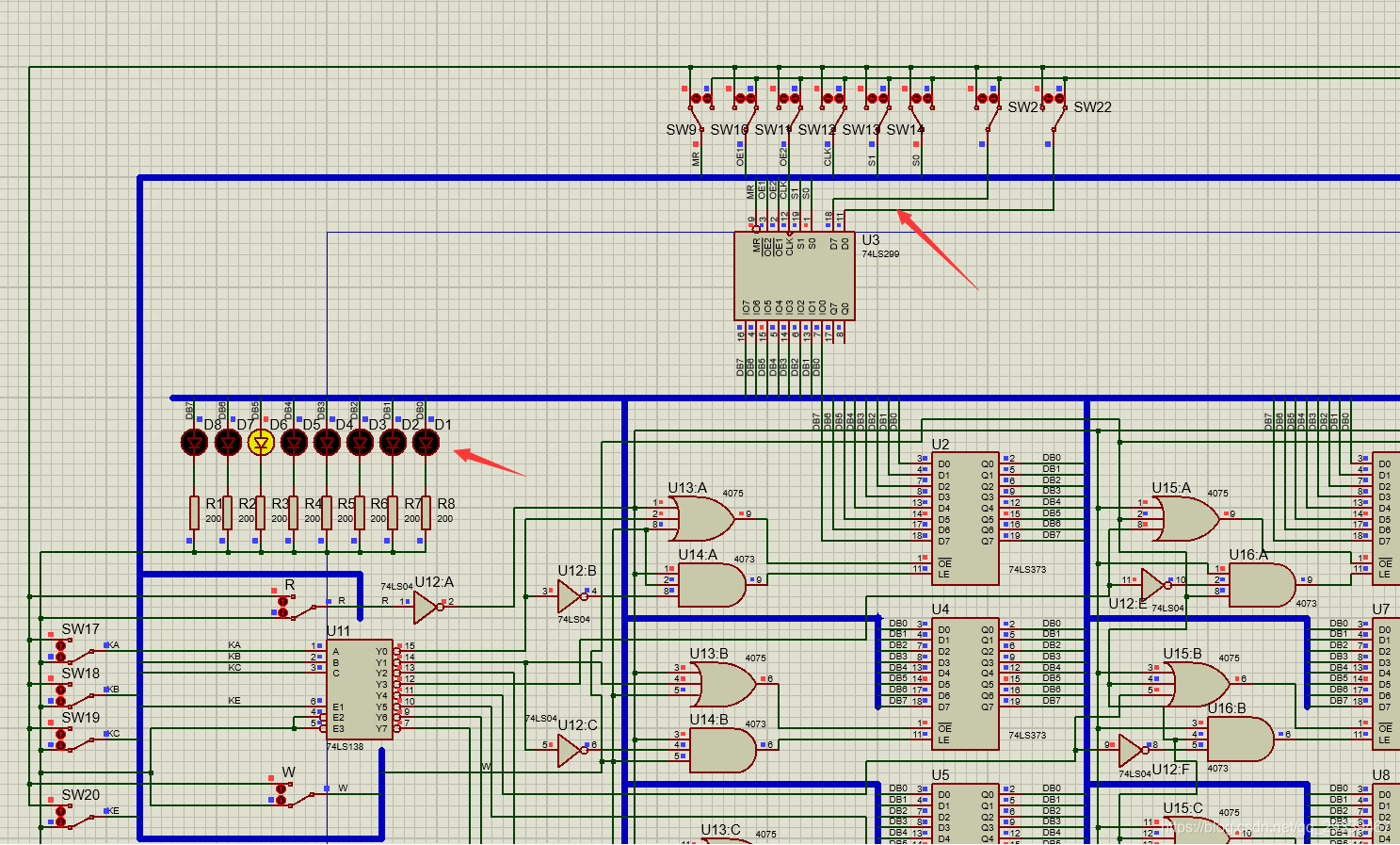

(一)验证寄存器写操作

- 首先,通过开关给 74LS245 输入数据,打开 74LS245 开关(CE引脚置0),将数据传送到总线上。如果需要对数据进行保存,通过 74LS138 输入开关(A、B、C)选通某个 74LS373 寄存器,打开 74LS373 的写开关(OE引脚),将数据写入 74SL373 ,然后关闭写开关,关闭 74LS245(CE引脚置1)。关闭 74LS245 后,此时总线上无数据。(放一张中间的图吧,下图对应的 74LS138 选通的是第一个寄存器,打开 74SL373 写开关)

我这里测试的八位数据是

00100100,选择的寄存器是第一个

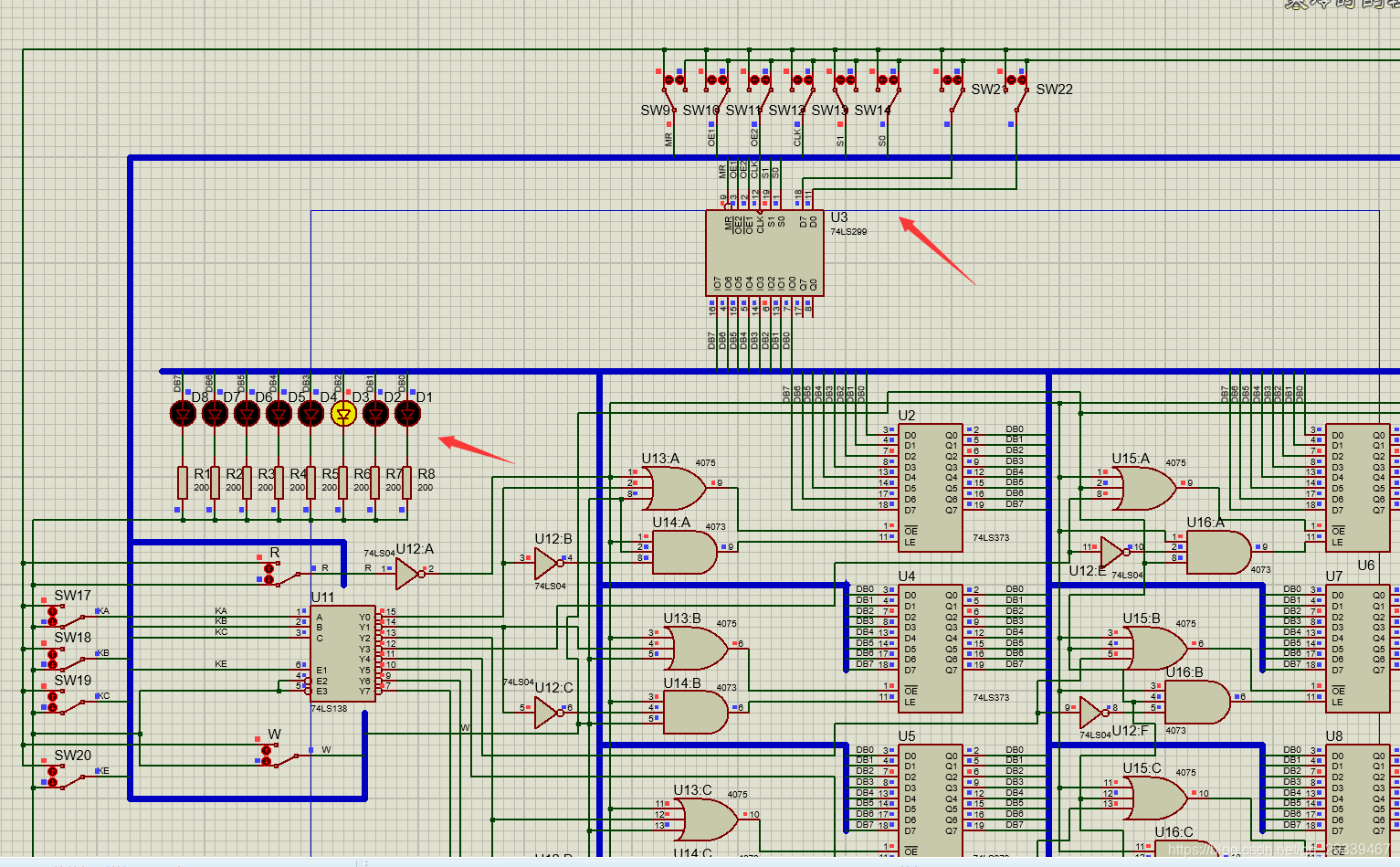

(二)验证寄存器读操作

- 接着上一步,将 74LS373 的读开关(LE引脚)打开,将 74LS373 中所存的数据输出到总线上,读操作完成。

- 如图,此时 74LS245 是关闭的(CE引脚为1)的,打开 74LS373 的读开关后,数据输出到总线

(三)移位操作

移位和循环移位的区别

- 循环移位区别于一般移位的是移位是 没有数位的丢失。

- 循环左移时,用从左边移出的位填充字的右端,而循环右移时,用从右边移出的位填充字的左侧

- 例: 10110011

- 右移1位得到 :01011001

- 循环右移1位得到:11011001

-

进行移位操作前,需要先将总线上的数据写入 74LS299 ,接着上一步,我们已经将 74LS373 的数据输出到总线上,然后我们给与 74LS299 的 CLK 引脚一个上升沿,就可以将总线上的数据写入 到74LS299 中, 然后关闭 74LS373 的读开关(此时总线无数据)

-

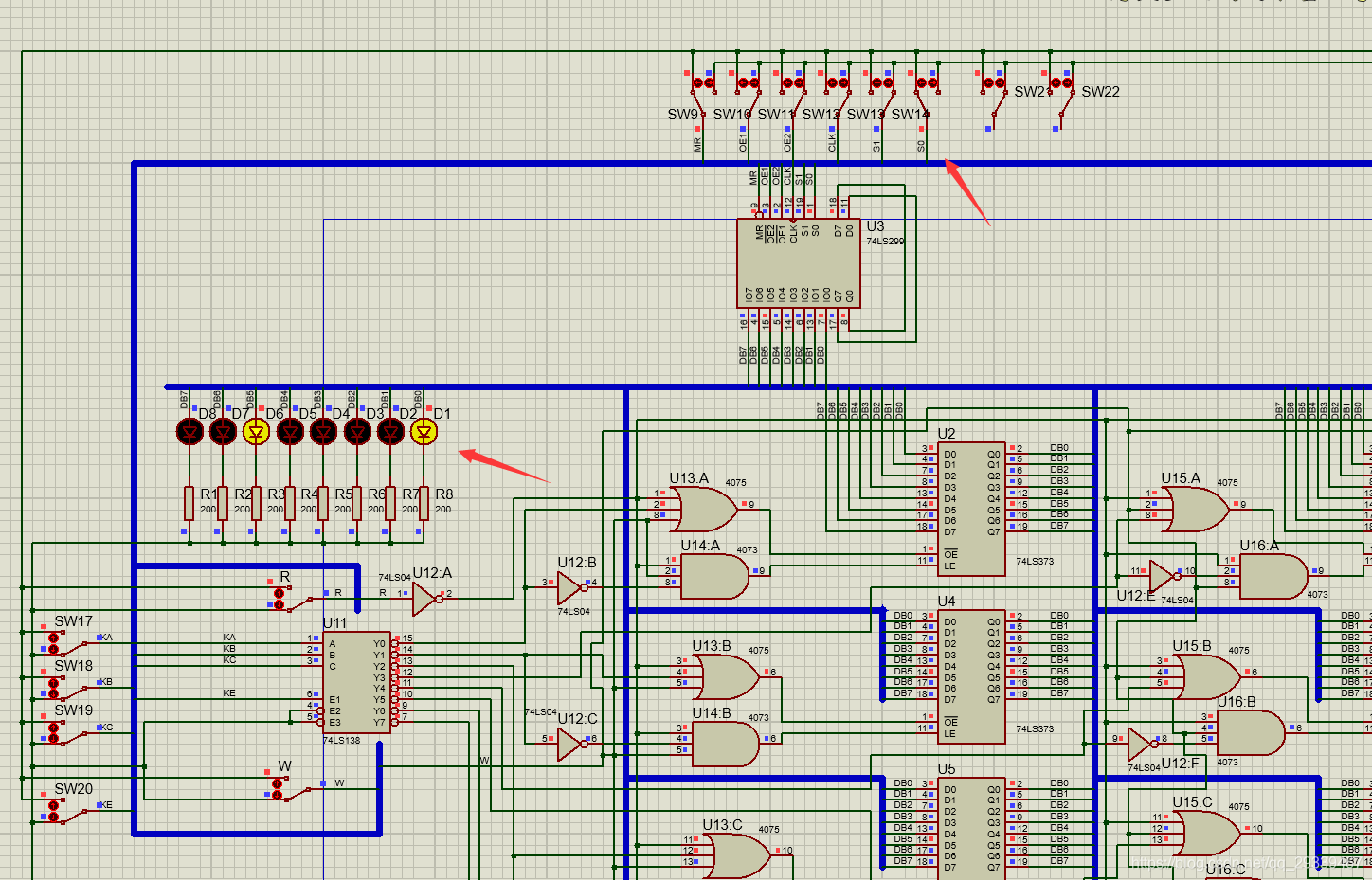

左移操作

- 74LS299 的 OE1、OE2、S1 、D7、D0 引脚均置 0,S0、MR 引脚置1(MR为0强制清零),持续给 CLK 上升沿就可以了(将开关重复拨上拨下) ,观察 LED 的变化。

- 如下图,持续进行左移操作,发现 最高位被移出

- 右移操作

- 右移 S1置1,S0 置0,OE1、OE2、S0 、D7、D0 引脚均置 0,S1、MR 引脚置1,同样持续给与 CLK 引脚上升沿,然后观察 LED 的变化。

- 如下图,持续进行右移操作,发现 最低位被移出

(四)循环移位操作

- 循环左移

- 将 74LS299 的 D7 引脚接到Q0引脚,D0 引脚接到 Q7 引脚,OE1、OE2、S1 、D7、D0 引脚均置 0,S0、MR 引脚置1,持续给与 CLK 上升沿,观察 LED 变化。

- 如下图进行循环左移操作,我们可以看出,循环左移最高位移动到了最低位

- 循环右移

-

将 74LS299 的 D7 引脚接到Q0引脚,D0 引脚接到 Q7 引脚,OE1、OE2、S0 、D7、D0 引脚均置 0,S1、MR 引脚置1,持续给与 CLK 上升沿,观察 LED 变化。

-

如下图进行循环右移操作,我们可以看出,循环右移最低位移动到了最高位

-

我们可以将循环右移后的总线上的数据写入 74LS373 中。如图,将总线上的数据写入到 74SL373 中,并进行了

读操作(LE)

-

思考问题

-

最后有一个小的思考问题

思考随着寄存器的增多,电路设计的复杂度是什么比例增大 -

寄存器增多,设计上来说复杂度是成倍的增加,电路的设计难度也有一定的提高。

原工程文件:

链接:https://pan.baidu.com/s/1mVnxtAznoFetXNdCohPYkg

提取码:hmcq

如果本文对你有小小的帮助,请点个赞再走吧 😄

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?