软件版本: Vivado 2019.1 (2019.1版本之前还使用SDK工具,2019.2版本后使用新的vitis)

FPGA: Artix7 xc7a100tfsg484-2

DDR3: MT41K256M16TW-107 两片共1GByte

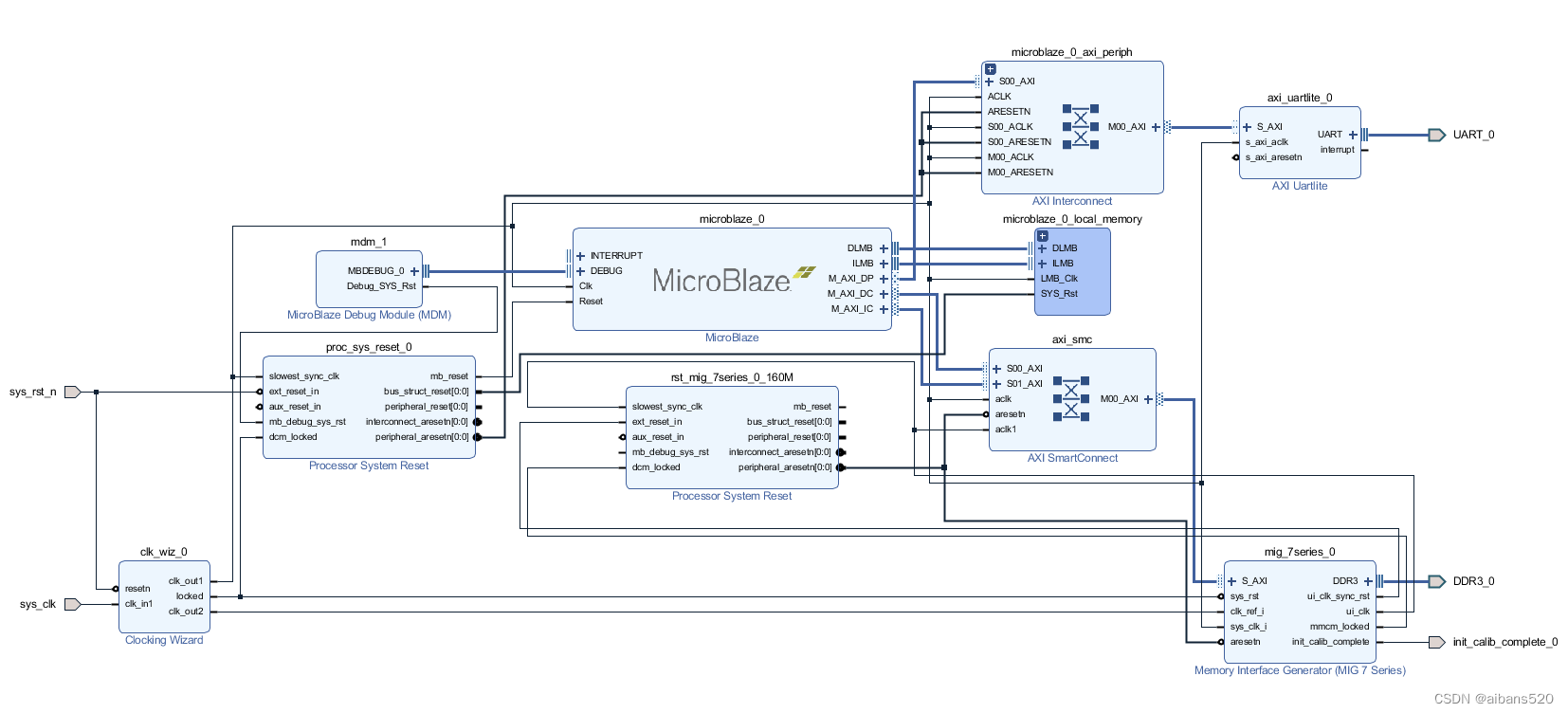

1. Vivado下新建工程,创建Block Design如下:

clk_wiz_0配置两个频率输出:clk_out1=160Mhz连接MicroBlaze及外围,同时提供给MIG sys_clk_i。clk_out2=200Mhz连接到MIG clk_ref_i(参考时钟为200MHz)

MIG ui_clk=160Mhz(配置360MHz 2:1)

因为 sys_clk_i为clk_wiz_0提供,sys_rst 应连接到locked。

MIG aresetn应连接到rst_mig_7series_0_160M的peripheral_aresetn, 这是官方建议的。

AXI SmartConnect 是MicroBlaze和MIG通信桥梁,因为两者使用不同时钟源,这里配置了2个时钟,aclk应连接clk_wiz_0 160Mhz, aclk1连接ui_clk 160Mhz。

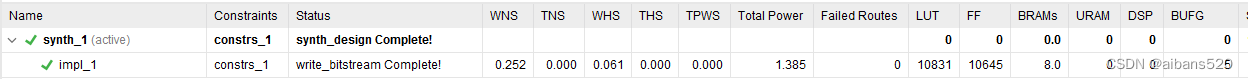

综合后资源情况:

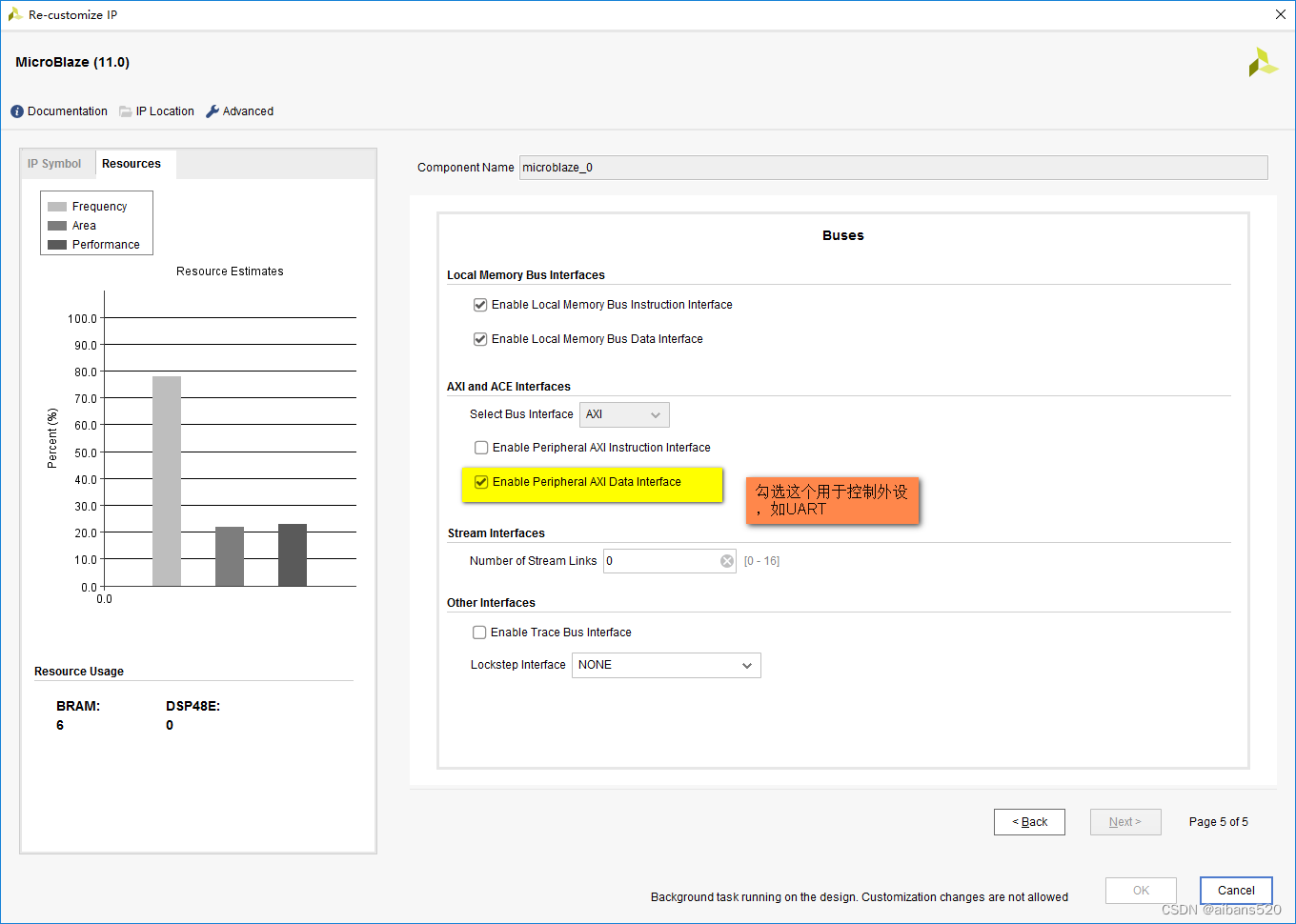

MicroBlaze配置:

General面页默认即可

Debug面页默认即可。

2. 生产bitstream.

3.导出 Hardware

记得勾选 Include bitstream

![]()

这时在工程目录下生产top_wrapper.hdf 文件。

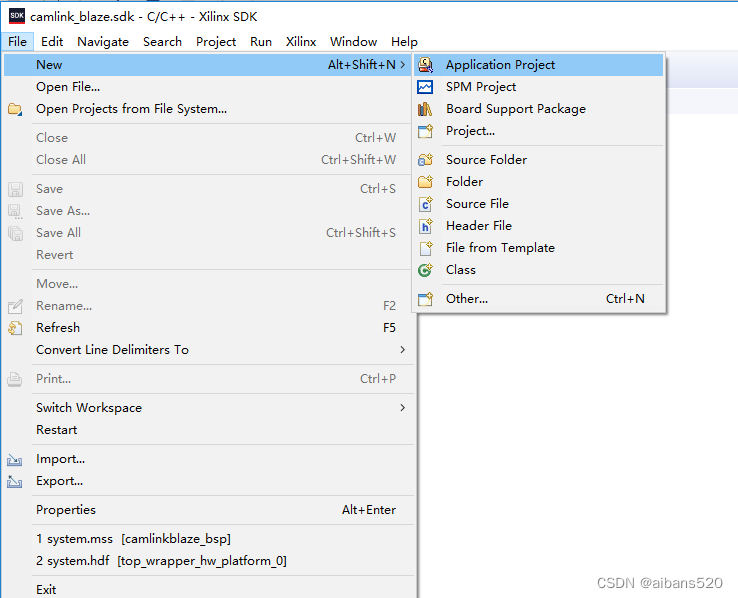

4. 打开SDK

如果之前没有安装SDK包,可以点击菜单Help-Add Design Tools or Devices 添加

默认OK。

此时,SDK软件自动打开

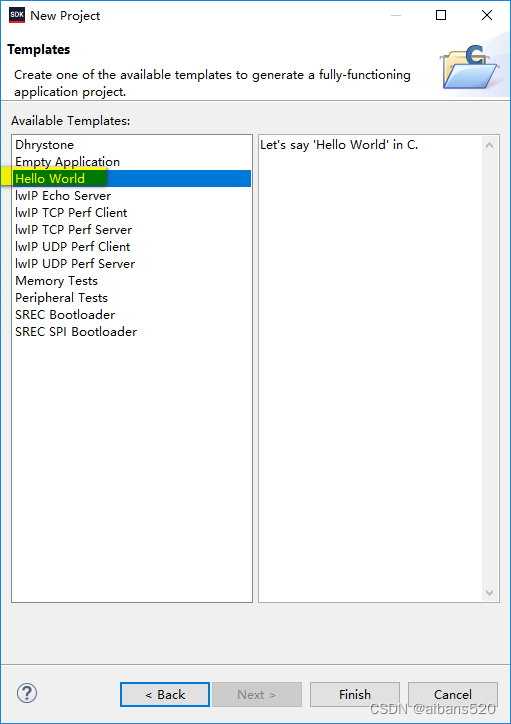

新建工程。

输入工程名,Next

选择简单的Hello World模板,Finish

加载比较慢,20核心电脑用了一分钟????

在左边src目录下就是源文件了。打开helloworld.c进行编辑

添加下面测试代码:

int main()

{

init_platform();

print("Hello World\n\r");

//

unsigned int*DDR_MEM = (unsigned int*)XPAR_MIG_7SERIES_0_BASEADDR;

*DDR_MEM =0x12345678; //Write 0x12345678 to DDR at MIG_7SERIES_0_BASEADDR

unsigned int value =*(unsigned int *)XPAR_MIG_7SERIES_0_BASEADDR; //Read data from DDR at same address

xil_printf("value= 0x%x\n", value);

cleanup_platform();

return 0;

}

保存,Build.

下载到FPGA

![]()

点击Program

运行

如果Run As选项下没有1-5, 可尝试右击工程,选择Clean Project

打开串口软件查看结果

打印成功。

6442

6442

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?