IP核(PLL核)如何调用

1、建立工程

2、PLL核配置

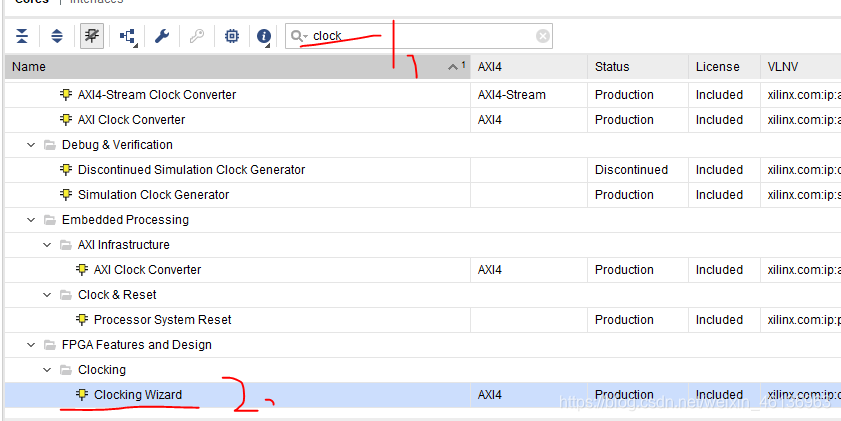

---------点击 Project Manager 界面下的 IP Catalog--------搜索clock -------双击clocking wizard,打开配置界面

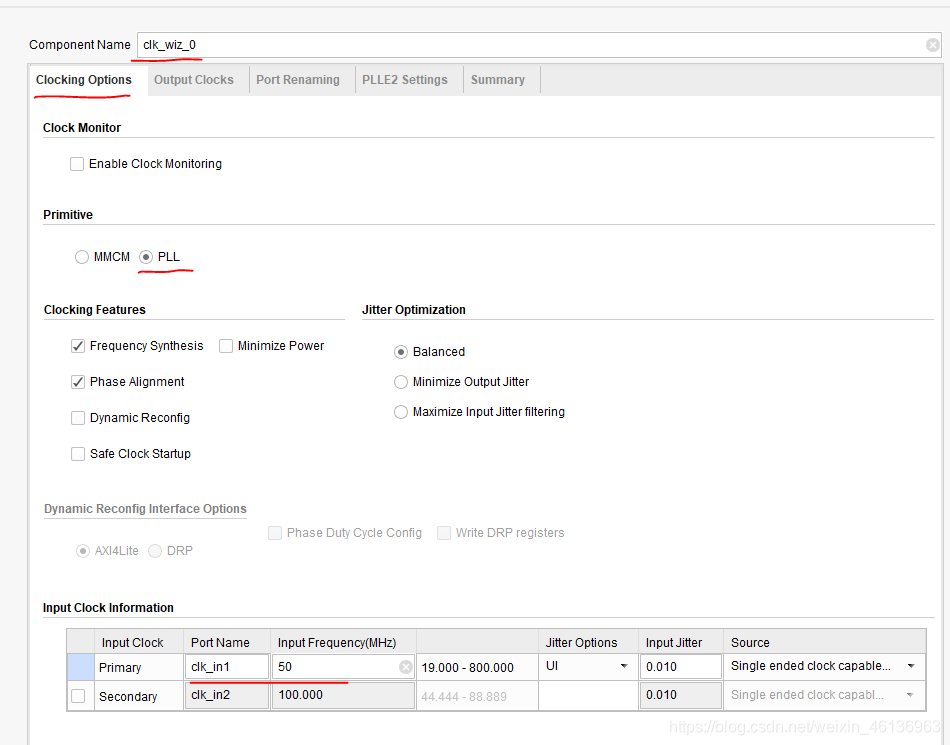

------默认这个 Clocking Wizard 的名字为 clk_wiz_0, 这里我们不做修改。在第一个界面 Clocking

------默认这个 Clocking Wizard 的名字为 clk_wiz_0, 这里我们不做修改。在第一个界面 Clocking

Options 里, 我们选择 PLL 资源,输入的时钟频率为 50Mhz。

---------------在 Output Clocks 界面里选择 clk_out1~clk_out4 四个时钟的输出,频率分别为 200Mhz,

100Mhz, 50Mhz, 25Mhz。这里还可以设置时钟输出的相位,我们不做设置,保留默认相位,

点击 OK 完成,然后点击生成。

3、新建源文件,编写源文件

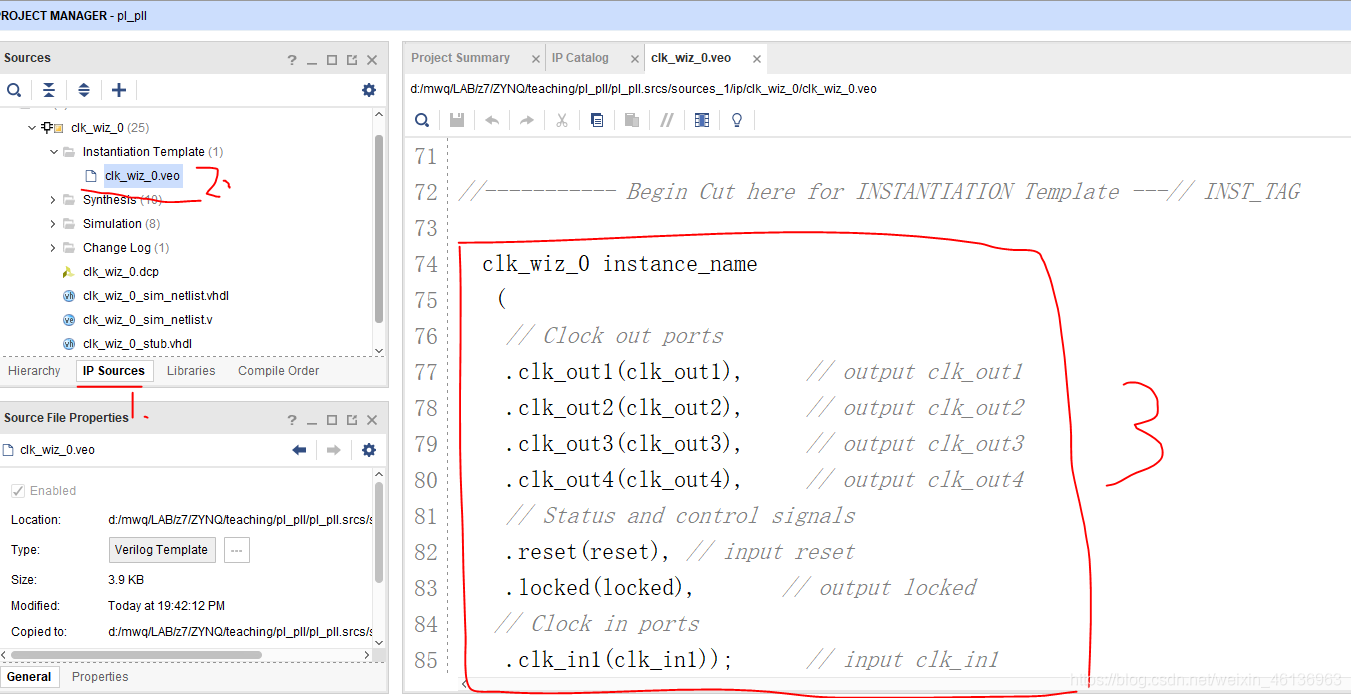

选择 IP Sources 这页,然后双击打开 clk_wiz_0.veo 文件,这个文件里提供了这个 IP 的实例化模板。我们只需要把框框的中内容拷贝到我们 verilog 程序中,对 IP 进行实例化。

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2021/05/21 19:43:27

// Design Name:

// Module Name: pl_pll

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module pl_pll(

input sys_clk,// PL端的时钟为50MHz

input rst_n,//复位,低电平有效

output clk_out,

output reg [3:0] led

);

reg [31:0] timer_cnt;

wire locked;

/ 调用 PLL IP /

// 功能说明:程序中先用实例化 clk_wiz_0, 把单端 50Mhz 时钟信号输入到 clk_wiz_0 的 clk_in1,把clk_out4 的输出赋给 clk_out。

clk_wiz_0 clk_wiz_0_uut

(

// Clock in ports

.clk_in1(sys_clk), //in 50Mhz 周期为20ns

// Clock out ports

.clk_out1(clk_out1), // output clk_out1 out 200MHz

.clk_out2(clk_out2), // output clk_out2 out 100MHz

.clk_out3(clk_out3), // output clk_out3 out 50MHz

.clk_out4(clk_out), // output clk_out4 out 25MHz

// Status and control signals

.reset(~rst_n), // reset表示PLL这个核的模块端口,rst_n表示送入的值

.locked(locked) // output locked

);

always @(posedge clk_out or negedge rst_n)

begin

if(!rst_n)//复位

begin

led<=4'd0;

timer_cnt<=32'd0;

end

else if (timer_cnt>=32'd24_999_999) //40ns*25*10^6=1s

begin

led=~led;// 计数到1s,LED灯的翻转

timer_cnt<=32'd0;

end

else

begin

led<=led;

timer_cnt<=timer_cnt+32'd1;

end

end

endmodule

4、新建约束文件,编写约束文件

create_clock -period 20 [get_ports sys_clk]

# 系统时钟的约束文件

set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]

set_property PACKAGE_PIN U18 [get_ports sys_clk]

# 复位的约束文件

set_property IOSTANDARD LVCMOS33 [get_ports rst_n]

set_property PACKAGE_PIN N15 [get_ports rst_n]

# 示波器探针的约束文件

set_property IOSTANDARD LVCMOS33 [get_ports clk_out]

set_property PACKAGE_PIN F17 [get_ports clk_out]

# led的约束文件

set_property PACKAGE_PIN J16 [get_ports {led[3]}]

set_property PACKAGE_PIN K16 [get_ports {led[2]}]

set_property PACKAGE_PIN M15 [get_ports {led[1]}]

set_property PACKAGE_PIN M14 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

create_clock -period 20.000 -name sys_clk -waveform {0.000 10.000} [get_ports sys_clk]

5、新建仿真文件,编写仿真文件

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2021/04/21 09:31:43

// Design Name:

// Module Name: sim_pll

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module sim_pll;

//input

reg sys_clk;

reg rst_n;

//output

wire clk_out;

// 初始化

pl_pll uut(

.sys_clk(sys_clk),

.rst_n(rst_n),//reset,low active

.clk_out(clk_out)

);

initial

begin

//初始化输入

sys_clk=0;

rst_n=1;// // pll reset, high-active

#1000;

rst_n=0;

end

// create clock;

always #10 sys_clk=~sys_clk;

endmodule

6、下载程序

实验结果

四个LED灯闪烁,周期为1s

1264

1264

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?