作为一名硬件工程师,调试单板或解BUG时测试会涉及到高速信号SPI、MIPI等通信协议,测试一般涉及电平和时序。SPI电平的测试包括幅值、过冲和下冲等;时序方面的测试,包括SCLK频率、保持时间和建立时间等。本文针对某型号规格书,对涉及SPI信号的测试项进行了简单介绍。

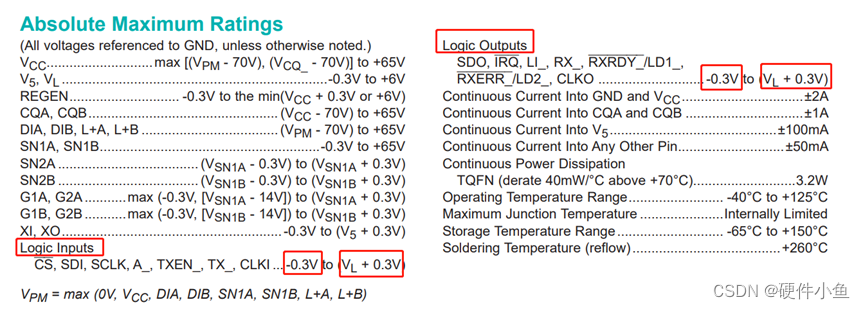

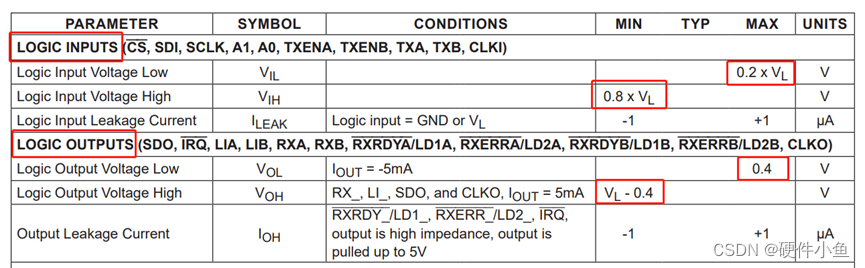

关于电平的测试标准,芯片规格书一般会在首页列出SPI等通信协议的电平范围,如下图的-0.3VL~VL+0.3V,再结合逻辑低电平的最大值(0.2VL)和高电平的最小值(0.8VL)等标准,就能判断出所测数据电平、过冲和下冲是否满足标准。

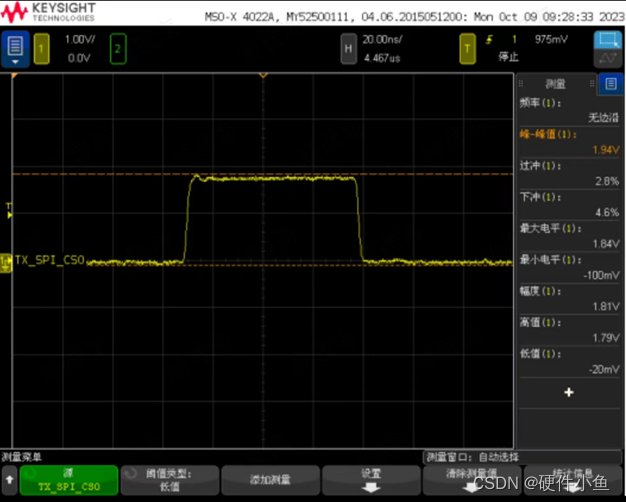

对于信号过冲和下冲信号的测试,需要合理运用示波器测量量进行结果判断。一般可以列出最大电平、最小电平、幅度、高电平平均值和低电平均值等测量量,尽量做到一次测试显示全部电平信息,避免反复测试浪费不必要的时间。下图给出了实测波形。

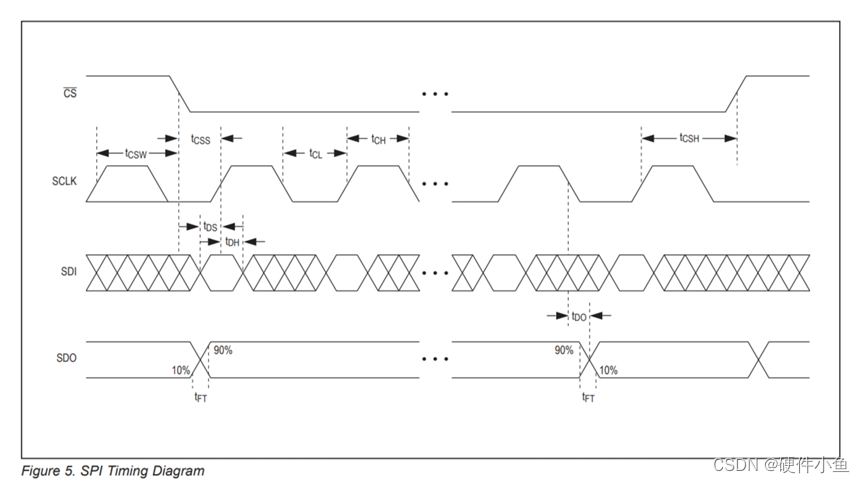

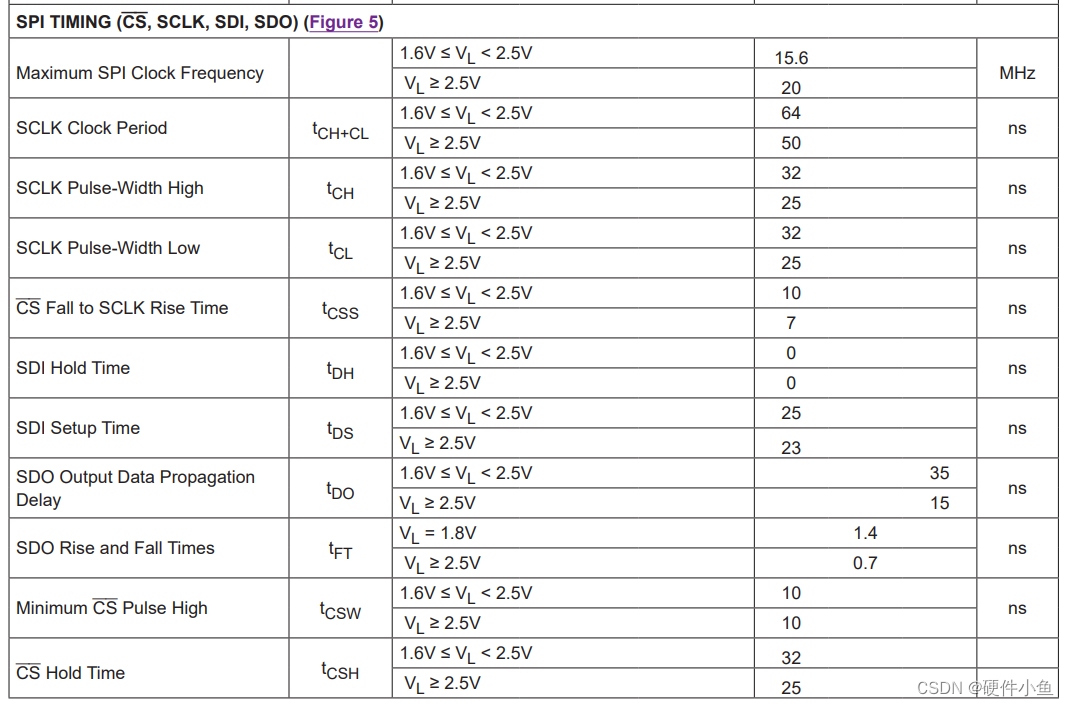

关于SPI时序的标准,芯片的规格书一般也会给出。测量SPI时序,主要涉及频率、建立时间和保持时间等参数的抓取,对测试不满足规格书要求的信号需要进行调试解决。

关于SPI的测试标准,取决于逻辑部分的外部供电大小(图里是VL),逻辑部分供电不同,时序的标准也会有所差别。信号线的测试项包括:各信号高低电平脉宽,频率,建立时间和保持时间。时序的测试一般满足标准的最小值即可。

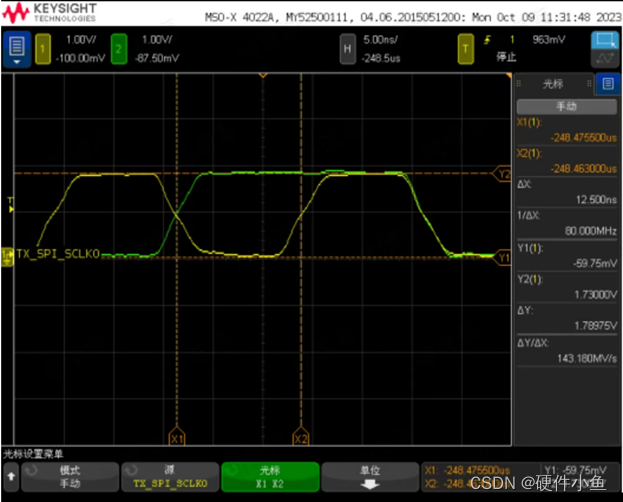

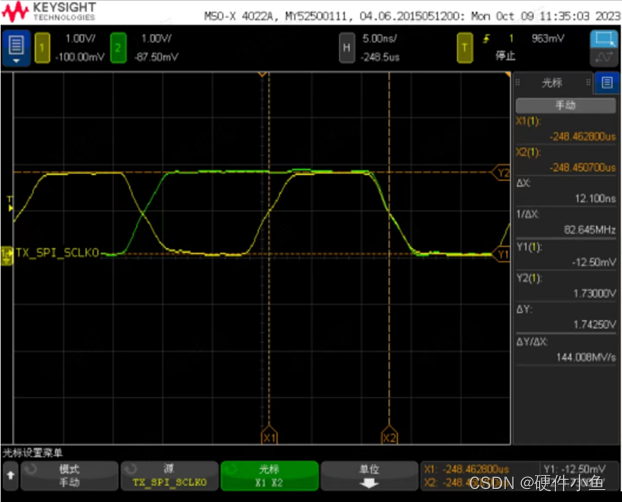

信号线间时序的测试只需取信号线上升沿或下降沿中间位置即可。测量时序时取信号中间点的原因在于方便找点位,这样避免找90%时的电平单位引入不必要的误差。SPI信号实测波形如下图所示:

(1)输入数据SDIO相对于时钟SCLK上升沿的建立时间tDS和保持时间tDH;

(2)输入数据SDIO相对于时钟SCLK上升沿的保持时间tDH;

本文详细介绍了硬件工程师在调试单板或处理SPI、MIPI通信协议时,如何进行电平和时序测试,包括电平范围判断、过冲/下冲测量、频率及保持时间的规格书依据,以及如何利用示波器进行高效测试和信号线间时序分析。

本文详细介绍了硬件工程师在调试单板或处理SPI、MIPI通信协议时,如何进行电平和时序测试,包括电平范围判断、过冲/下冲测量、频率及保持时间的规格书依据,以及如何利用示波器进行高效测试和信号线间时序分析。

669

669

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?