经过几天对linux 4.14内核源码中的spidev_test.c 、spidev.c的研究,初步实现FPGA 与BeagleBone的SPI通信。

-

BeagleBone端指令:

./spidev_test -D /dev/spidev2.0 -H -o result.txt -S4096 -I1 -v -b 16注:注意这个-符号,word会将其更改

./spidev_test -D /dev/spidev2.0 -H -S1024 -I1 -b16 -s1000000 -o result.bin -v参数说明:

-D --devicedevice to use (default /dev/spidev1.1),设置启动的SPI设备,spidev1.0 spidev1.1 spidev2.0 spidev2.1

-s --speedmax speed (Hz) 32个字节表示,4294967295Hz ,最大可设置为4296Mhz,肯定够用。

-d –delaydelay (usec),发送完成一帧数据后的延时时间,单位微秒。

-b --bpwbits per word,一帧数据的字节数,uint8_t bits = 8,默认八位。

-i --inputinput data from a file,SPI发送的数据来源于该文件,二进制读写 test.txt,不能与-p同时设置。

-o --outputoutput data to a file,SPI接受的数据存储的地方。

-l --loop回环模式,无参,自动检测通信,如果接受的数据和发送的数据一样则打印出来,不一样则报错。使用该模式必须指定-S –I

-H --cphaclock phase,时钟相位设置,无参,设置后SPI_CPHA=1

-O --cpolclock polarity,时钟极性设置,无参,设置后SPI_CPOL=1

-L --lsbleast significant bit first,无参,lsb最低位有效先传输还是最后传输,在大端模式下,二进制数据的最低有效位在右边,最高有效位在左边,默认则是传送二进制数据从左向右传,设置之后则变成从右向左传。

-C --cs-highchip select active high,拉高片选,无参。

-3 --3wireSI/SO signals shared,三线制SPI,收发数据公用一条线。

-v --verboseVerbose (show tx buffer),显示数据,无参,在终端中可打印出数据。

-p Send data "1234\\xde\\xad\" 终端键入发送数据的格式

-N --no-cs no chip select

-R --ready slave pulls low to pause

-2 --dual dual transfer,SPI的读写速度是普通序列式闪存的2-3倍,DI和DO是双向的,称作DI0 DI1

-4 --quad quad transfer,SPI的读写速度是普通序列式闪存的4-6倍;DI和DO是双向的,称作DI0 DI1,同时,/WP和/HOLD也变成输入输出管脚,称作DI2 DI3

-S --size transfer size\n" 发送随机数据的字节数,int,型不能超过 bufsiz=4096

-I --iter iterations\n"); 发送随机数据循环接收的次数,int型

BeagleBone中SPI程序未运行时:

cs : 高电平

miso : 低电平

mosi : 高电平

sck : 低电平

SPI:MODE1 CPOL=0 CPHA=1

第一个沿数据传输,第二个沿数据采集,sck空闲时低电平,片选低电平有效。

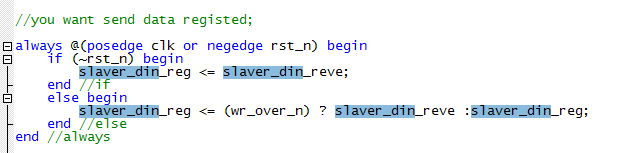

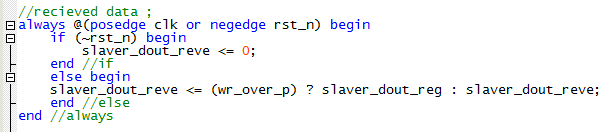

在实际分析时序之时,发现FPGA工程中写的片选信号在完成一个数据传输之后就拉高一次的时序与BeagleBone的SPI协议不符合,CS片选线只在一次完整的通信过程中拉低一次,所以需要对FPGA中SPI程序进行修改,将数据的触发保存信号改为wr_over信号,该信号由计数器计数,产生16个计数时,拉高一次,完成一个16位数据传输。wr_over信号的上升沿wr_over_p时刻,对采集到的数据保存;wr_over信号的下降沿wr_over_n时刻,将要发送的数据传入发送寄存器中保存。

-

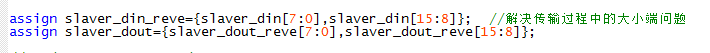

数据大小端问题

在实际数据通信的调试过程中,发现FPGA从二进制数据左侧高位开始发送,低位结束,满足Beaglebone采集顺序,但是因为是16位,两个字节,而先发过去的高位数据被放到了低位,低位数据被放到了高位,所以在FPGA中需要对数据顺序进行处理。

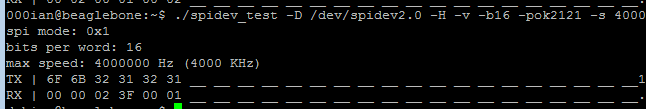

经过程序调试之后,测试结果如下:

6F6B : 0110 1111 0110 1011

3231 : 0011 0010 0011 0001

023F : 0000 0010 0011 1111

0001 : 0000 0000 0000 0001

Beaglebone TX < == > slaver_dout

Beaglebone RX < == > slaver_din

Speed : 4MHZ

Beagbone端发送6F6B,FPGA 的slaver_dout的接受到的第一个数据为无效数据,第二个数据为接受到的有效数据,为0110 1111 0110 1011b,与BBB端一致

BeagleBone端发送的第二个数据3231,FPGA接受到的第三个数据0011 0010 0011 0001b,一致。

FPGA端发送的第一个数据0000 0010 0011 1111,BeagleBone端接受到的第二个数据023F一致。

FPGA端发送的第三个数据0000 0000 0000 0001,BeagleBone端接受到的第三个数据0001一致。

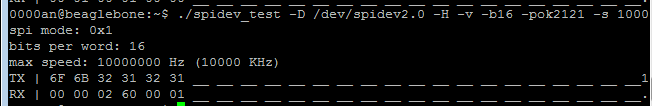

Speed : 10MHZ

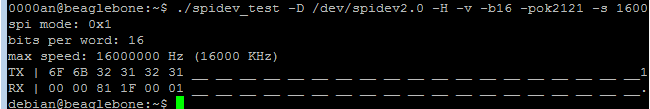

Speed : 16MHZ 数据异常

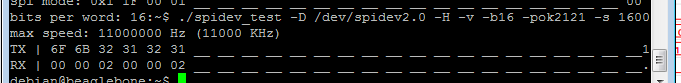

Speed : 11MHZ FPGA slaver_din异常

在正常10Mhz的速度下,传输经过FFT变换的1024个字节的数据,数据正常:

658

658

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?