项目场景:

AD9176 mode10调试记录

问题描述

-

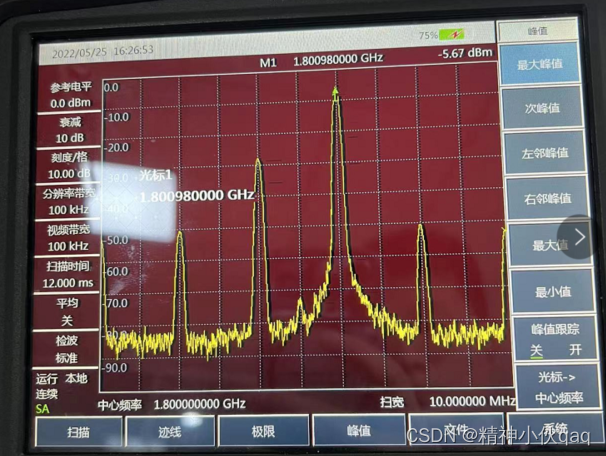

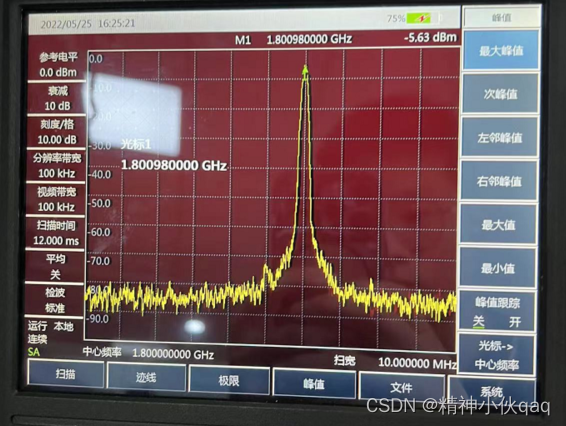

调试AD9176的过程中发现有时FPGA与DAC之间的JESD204B建链正常,但是出现了偶尔重新加载bit或者重启硬件后出现输出不正常的现象。如图1,此时DAC NCO配置为1.8GHz,FPGA产生的信号频率为9MHz。在频谱中显示出现多个峰值信号。

在此状态下,FPGA与DAC之间的JESD204B建链正常,sync信号稳定输出高电平,且通过ILA触发采集Sync信号沿变化时,始终无触发。

原因分析:

由于jesd204B接口sync信号稳定,说明204B建链正常。频谱中显示的最大峰值信号为实际需要输出的信号,但是在此信号左右还分布着幅度不一的其他信号,且均是等间隔分布。本人大胆猜测是由于IQ数字信号失调导致的!在此种情况下可能会引入别的频率分量。

解决方案:

1、由于是上电或者重新加载bit后概率性出现此现象,所以先检查FPGA工程架构,确认时钟网络正常。

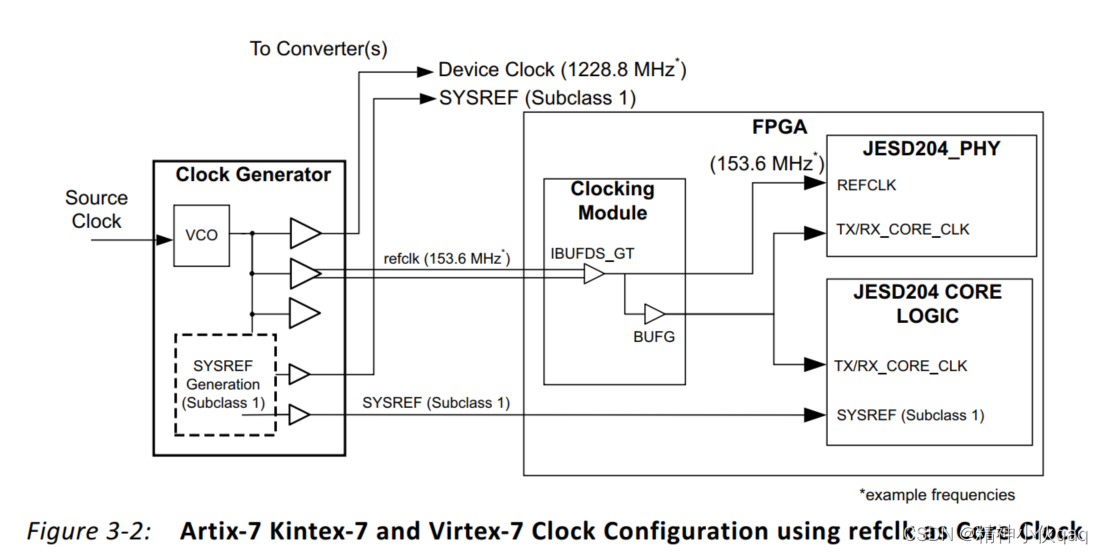

参阅PG066,对于7系列FPGA推荐使用以下的框图搭建时钟网络。

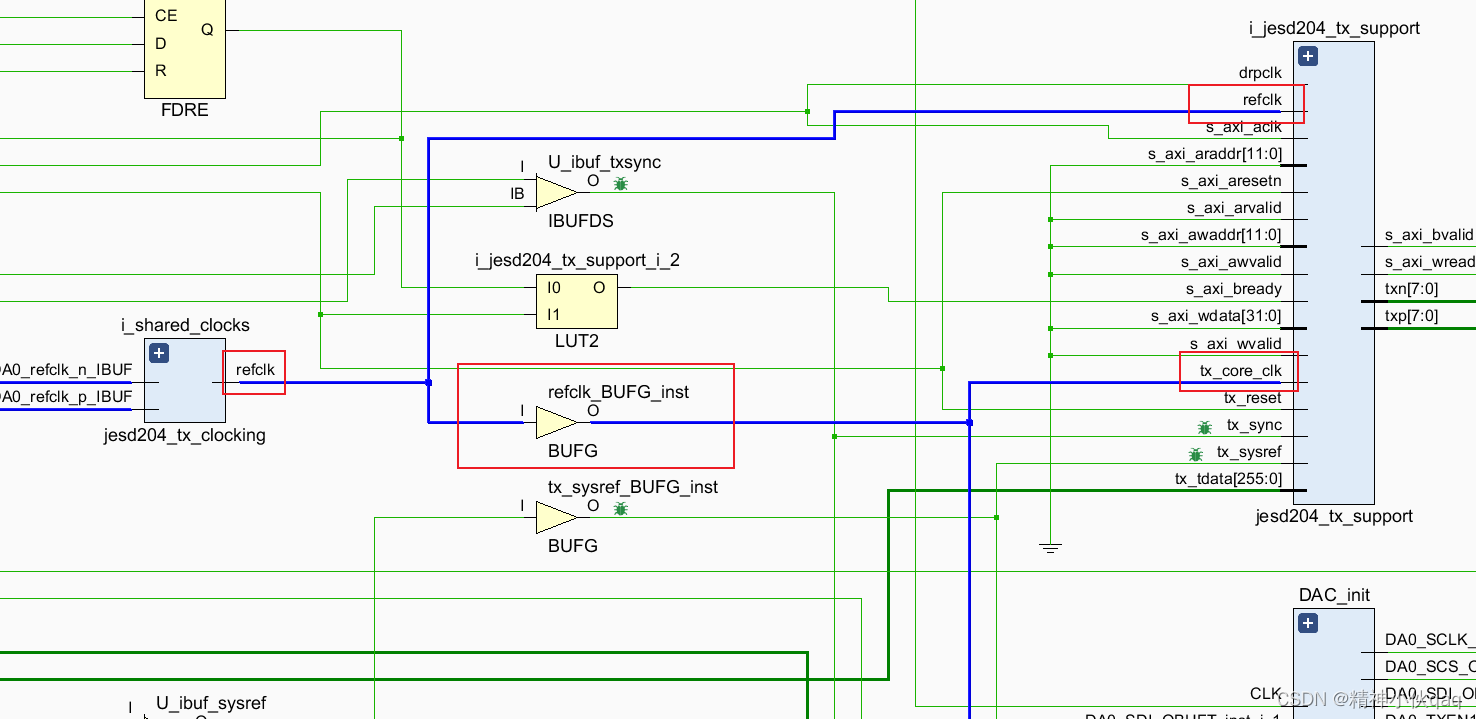

经过修改以后,工程时钟网络如下

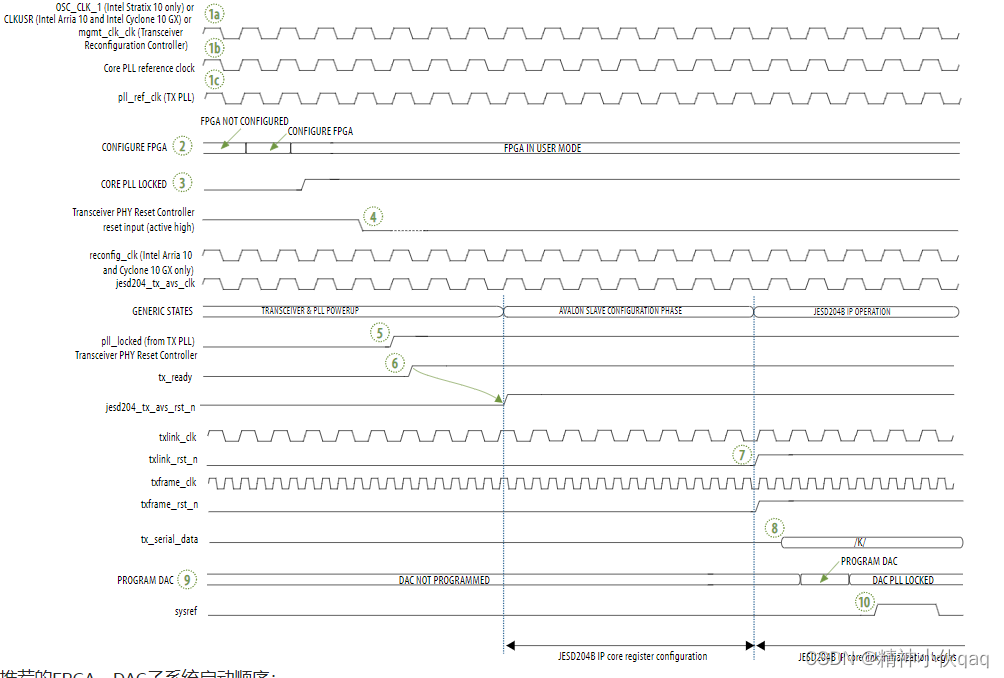

2、确认复位时序。DAC-FPGA jesd204B接口正确的复位时序应该是先复位FPGA端的tx_core,再复位DAC并进行spi配置。参阅https://www.intel.cn/content/www/cn/zh/docs/programmable/683442/20-2-19-2-0/fpga-dac-subsystem-reset-sequence.html

修改完以上两步后,精彩的来了!无论重新加点还是加载bit文件后,DAC输出始终处于上面描述的非正常状态!

说明此时FPGA-DAC系统应该是处于稳定的状态了!那么最后再去解决IQ失调的问题就可以了~!

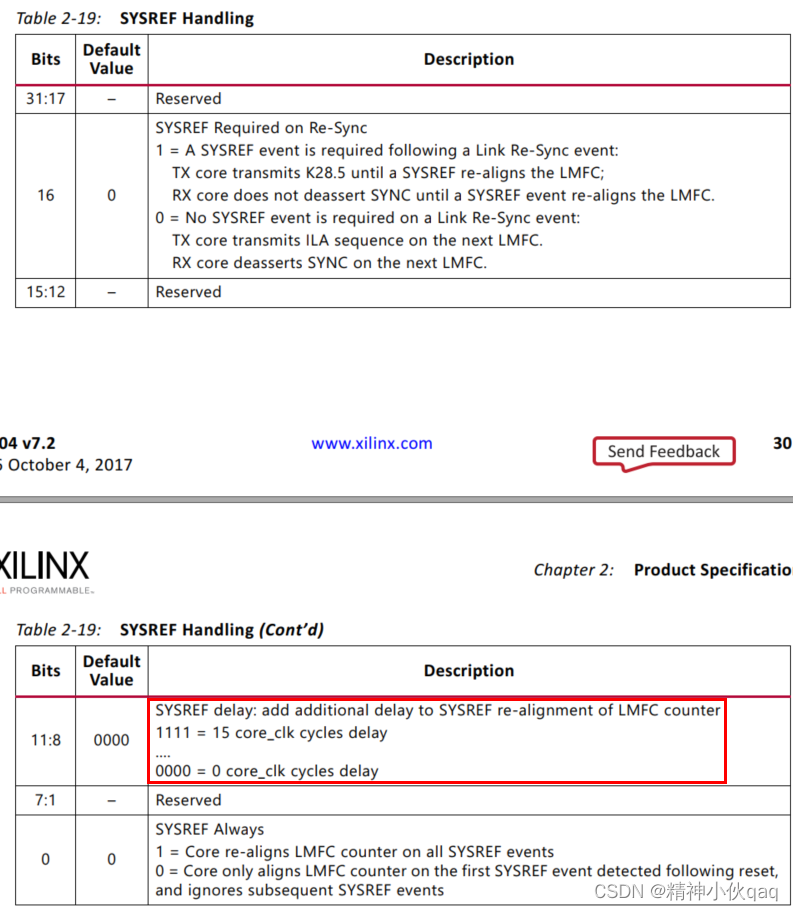

3、由于才疏学浅,对JESD204B的建链过程不够熟悉,了解不够深入,猜测IQ失调的根本原因在于FPGA和DAC两端的Lane数据不同步。即sysref延迟不一致!继续参阅PG066中关于sysref部分的描述及配置!

通过修改0x0010寄存器中关于sysref delay的值,发现有效果!

最后配置完后反复重启和加载bit后均没有出现之前不正常的现象!

最后附上AD9176 mode10下配置参数:

/*

AD9176 mode10 configuration

1.DAC Rate = 4.8G

2.Data Rate = DAC Rate / Total Interpolation = 4.8G / 4 = 1200M

3.Lane Rate = M/LNP(10/8)Data Rate

= 2/81610/81200M

= 6G

4.Refclk = Core clk = Lane Rate / 40 = 6G / 40 = 150M

5.SysRef = 6G/(10321*2) = 9.375M

6.DAC PLL Enabled, M = 4 ,N= 2 , VCO Frequrency divide by 2

7.Enabled NCO. NCO frequency = 1.8GHz,FTW = 0x6000_0000_0000

8.Disabled NCO modulus.

9.Total Interpolation = Datapath interpolation * Channel interpolation = 4 * 1 = 4.

*/

841

841

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?