系列文章之 上章

文章目录

前言

@和原子哥一起学习FPGA

开发环境:正点原子 ATK-DFPGL22G 开发板

参考书籍:

《ATK-DFPGL22G之FPGA开发指南_V1.1.pdf》

个人学习笔记,欢迎讨论

一、Verilog 简介

Verilog HDL(以下简称 Verilog),VHDL 是美国军方组织开发的,而 Verilog 是由一个公司的私有财产转化而来。

Verilog 是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻

辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

目前,Verilog-2001 是 Verilog 的最主流版本,被大多数商业电子设计自动化软件支持。

二、Verilog基础

1.逻辑值

逻辑 0:表示低电平,也就是对应我们电路的 GND;

逻辑 1:表示高电平,也就是对应我们电路的 VCC;

逻辑 X:表示未知,有可能是高电平,也有可能是低电平;

逻辑 Z:表示高阻态,外部没有激励信号是一个悬空状态。

2.进制

二进制表示如下:4’b0101 表示 4 位二进制数字 0101;

十进制表示如下:4’d2 表示 4 位十进制数字 2(二进制 0010);

十六进制表示如下:4’ha 表示 4 位十六进制数字 a(二进制 1010)。

当代码中没有指定数字的位宽与进制时,默认为 32 位的十进制,比如 100,实际上表示的值为

32’d100。

3.标识符

标识符(identifier)用于定义模块名、端口名和信号名等。Verilog 的标识符可以是任意一组字母、数

字、$和_(下划线)符号的组合,但标识符的第一个字符必须是字母或者下划线。另外,标识符是区分大小写的。

4.数据类型

寄存器类型

寄存器数据类型有很多种,如 reg、integer、real 等,其中最常用的就是 reg 类型.不能赋初值,寄存器类型的缺省值是 x(未知状态)。

如果该过程语句描述的是时序逻辑,即 always 语句带有时钟信号,则该寄存器变量对应为寄存器;

如果该过程语句描述的是组合逻辑,即 always 语句不带有时钟信号,则该寄存器变量对应为硬件连线

线网类型

线网表示 Verilog 结构化元件间的物理连线。

它的值由驱动元件的值决定,例如连续赋值或门的输出。如果没有驱动元件连接到线网,线网的缺省值为 z(高阻态)。

线网类型同寄存器类型一样也是有很多种,如 tri 和 wire 等,其中最常用的就是 wire 类型。

默认不指定就是线网类型!

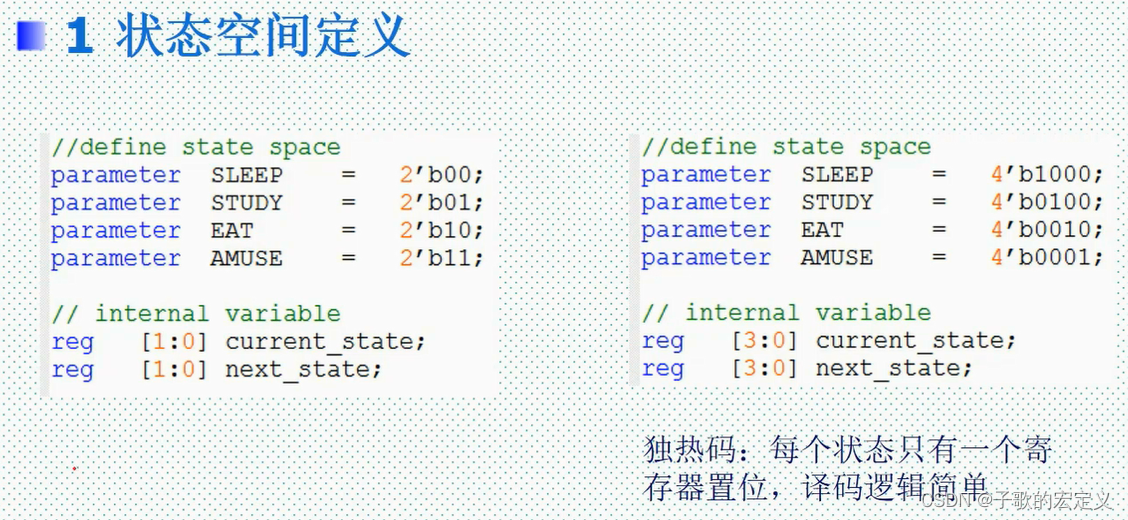

参数类型

参数其实就是一个常量,常被用于定义状态机的状态、数据位宽和延迟大小等

parameter DATA_WIDTH = 8; //数据位宽为8位

5.运算符

Verilog 中的运算符按照功能可以分为下述类型:

1、算术运算符

Verilog 实现乘除比较浪费组合逻辑资源,尤其是除法。除法只能整除。

2、关系运算符

3、逻辑运算符

4、条件运算符

5、位运算符

6、移位运算符

7、拼接运算符

{} 用这个运算符可以把两个或多

个信号的某些位拼接起来进行运算操作

三、Verilog 程序框架

1.注释

和C语言一致

正点原子建议的写法:使用//作为注释。

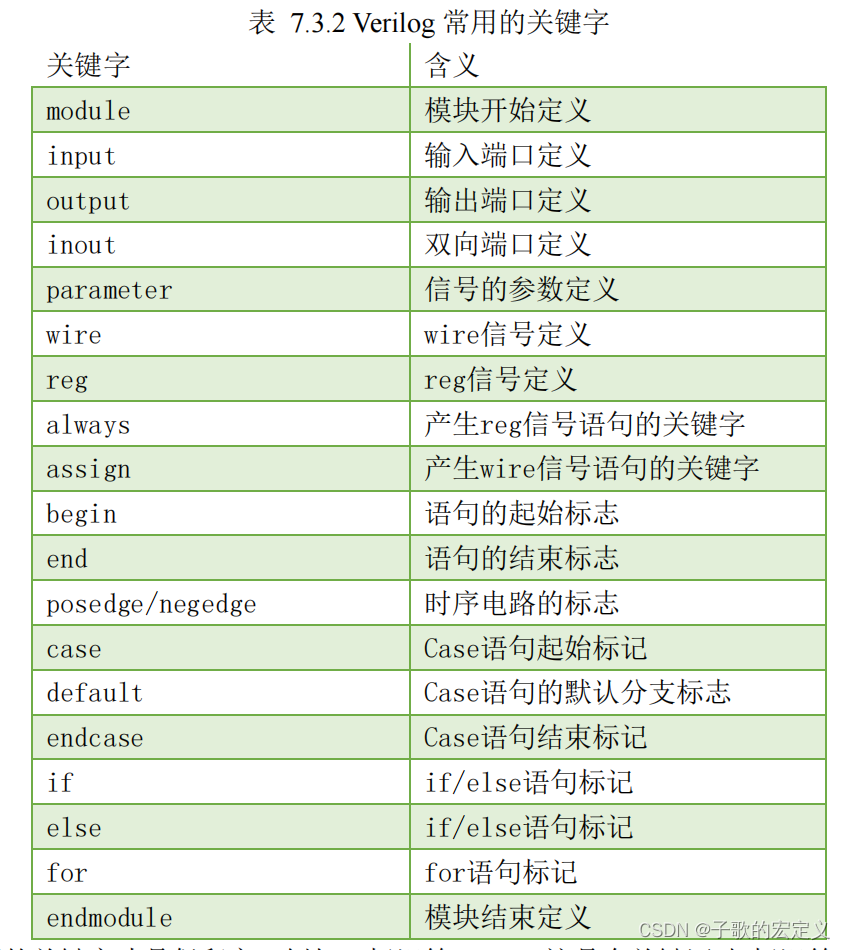

2.关键字

什么时候用reg,什么时候用wire

一般情况下,always用的是reg,assign用的是wire

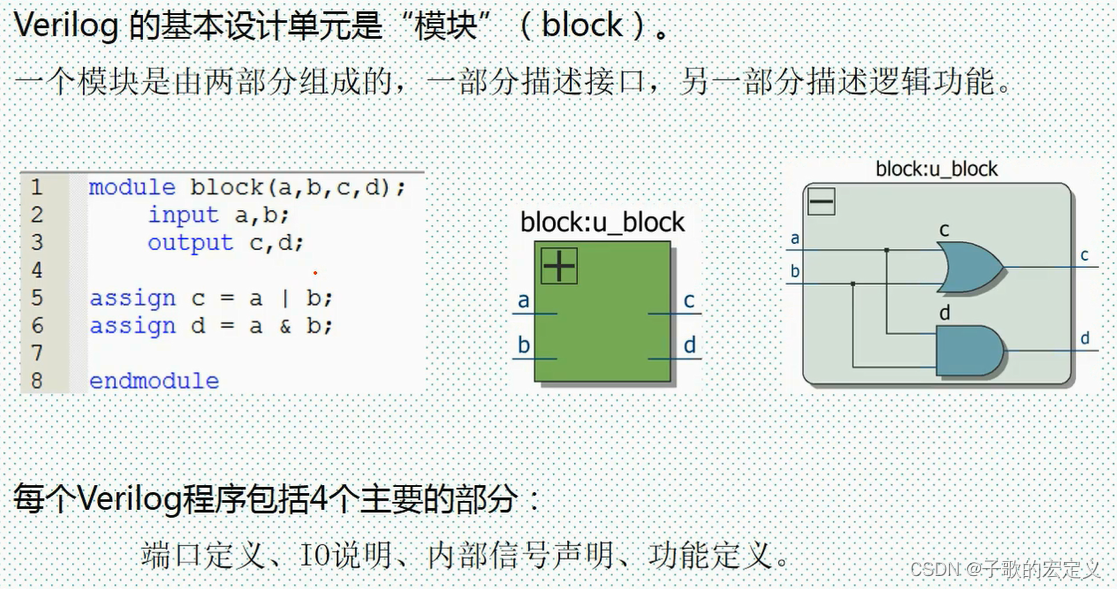

3.程序框架

四、Verilog 程序语句

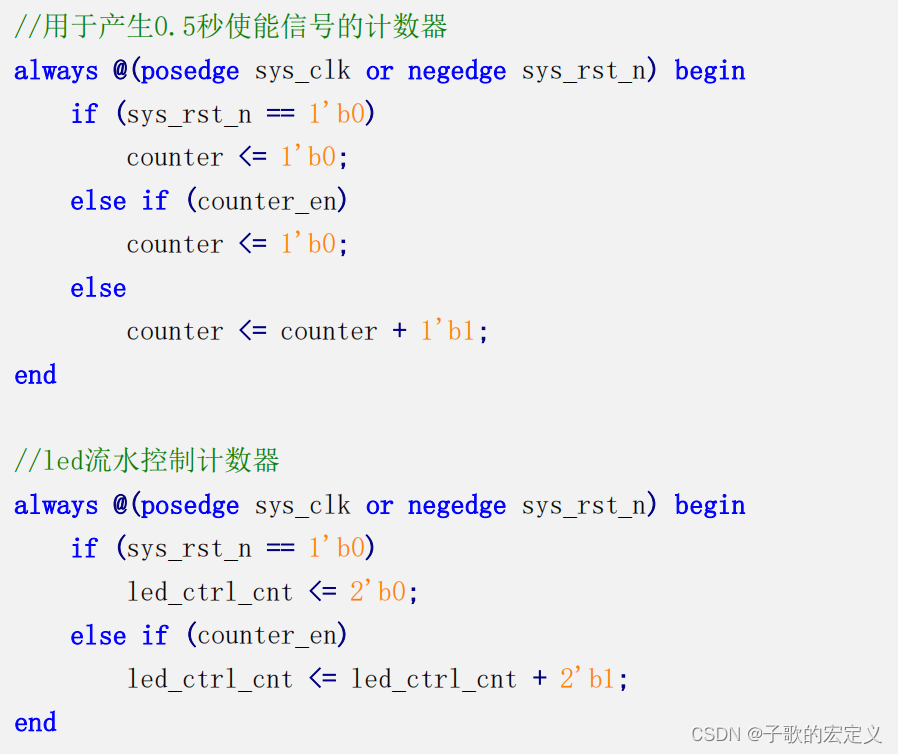

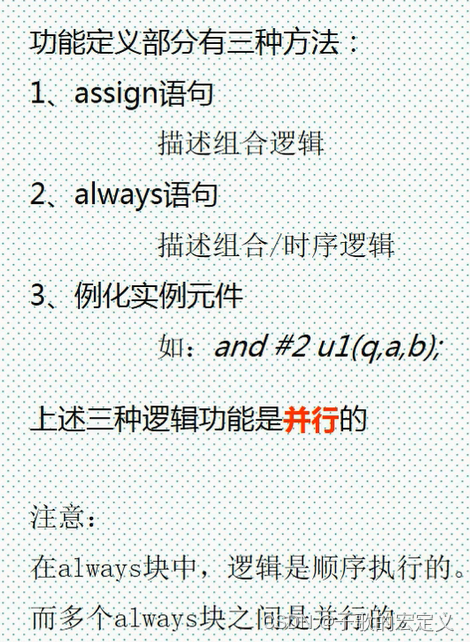

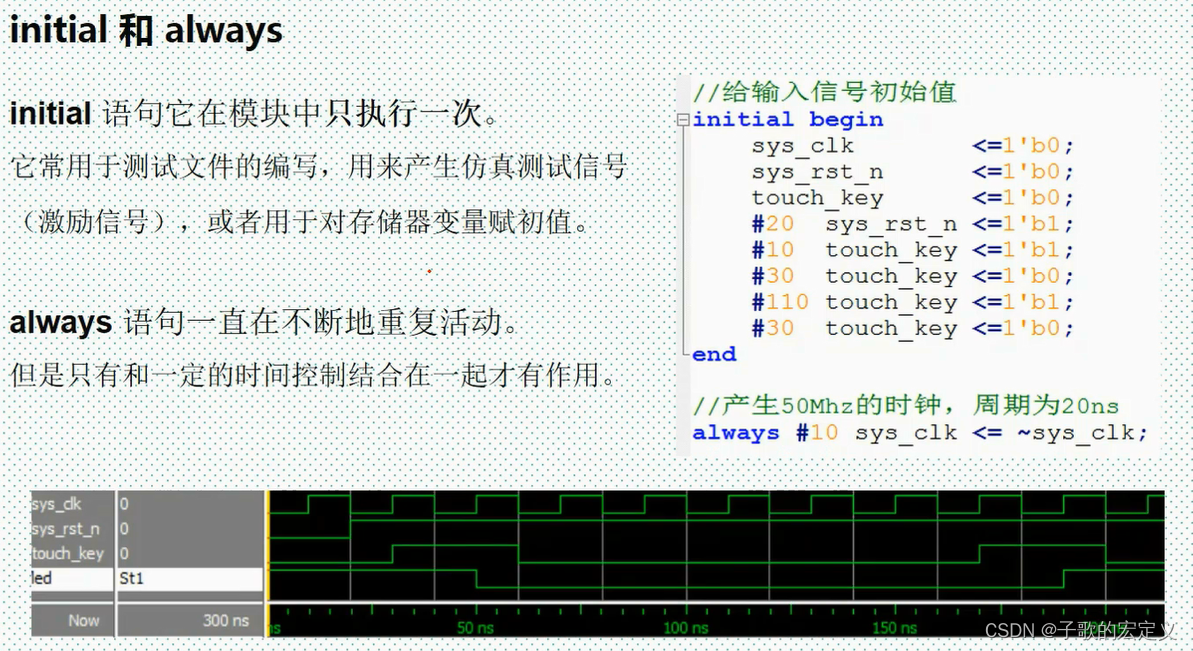

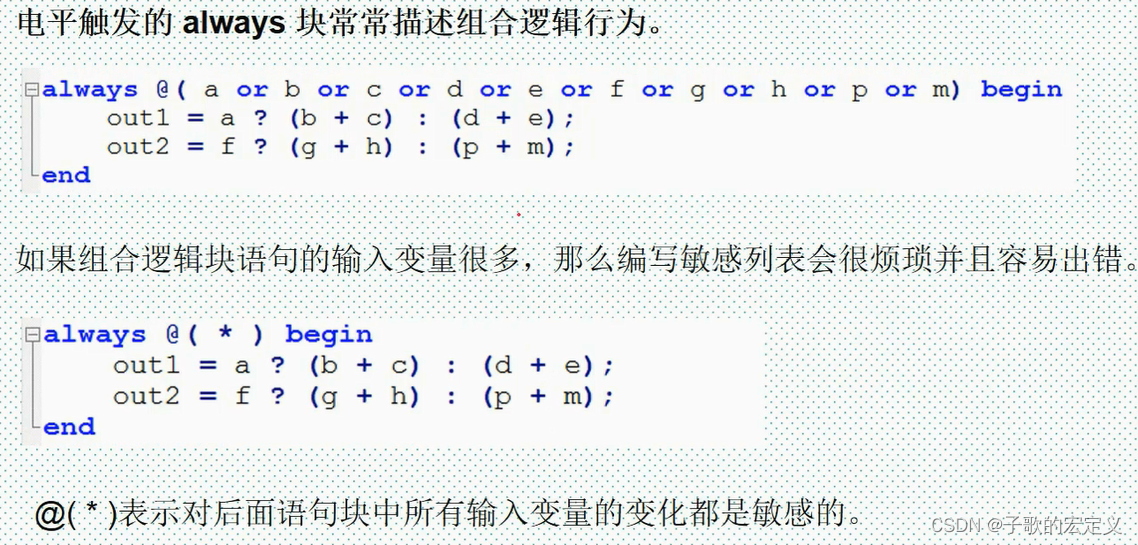

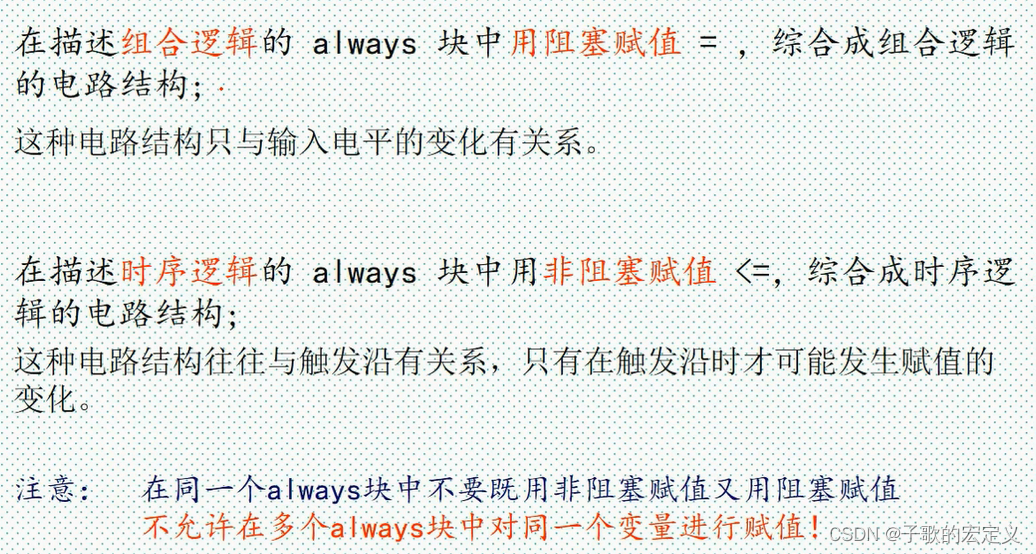

1.结构语句

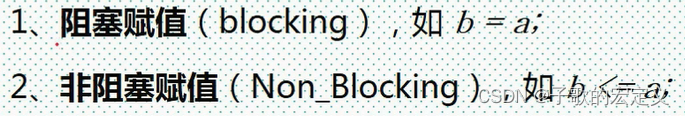

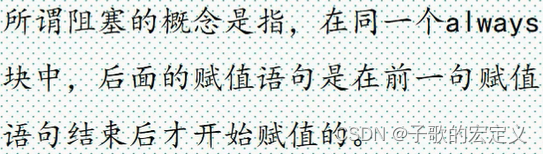

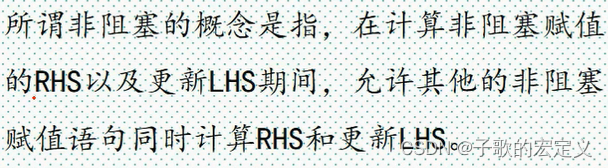

2.赋值语句

RHS:赋值等号右边的表达式或变量可以写作 RHS 表达式或 RHS 变量;

LHS:赋值等号左边的表达式或变量可以写作 LHS 表达式或 LHS 变量;

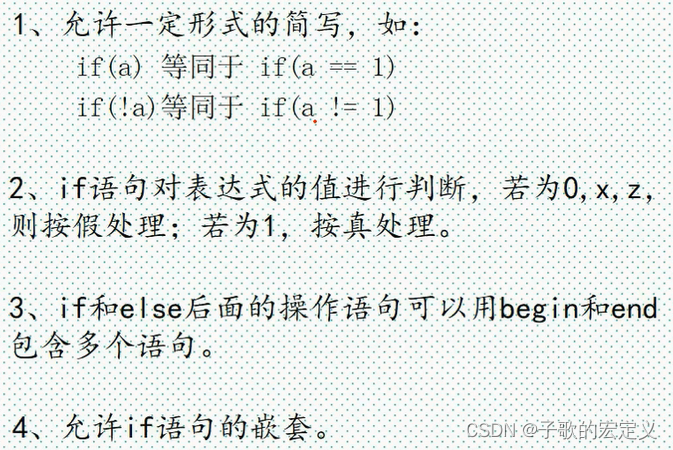

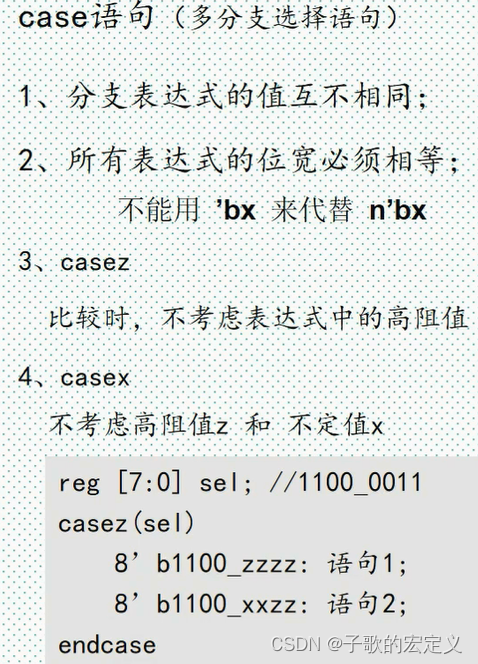

3.条件语句

四、Verilog 状态机

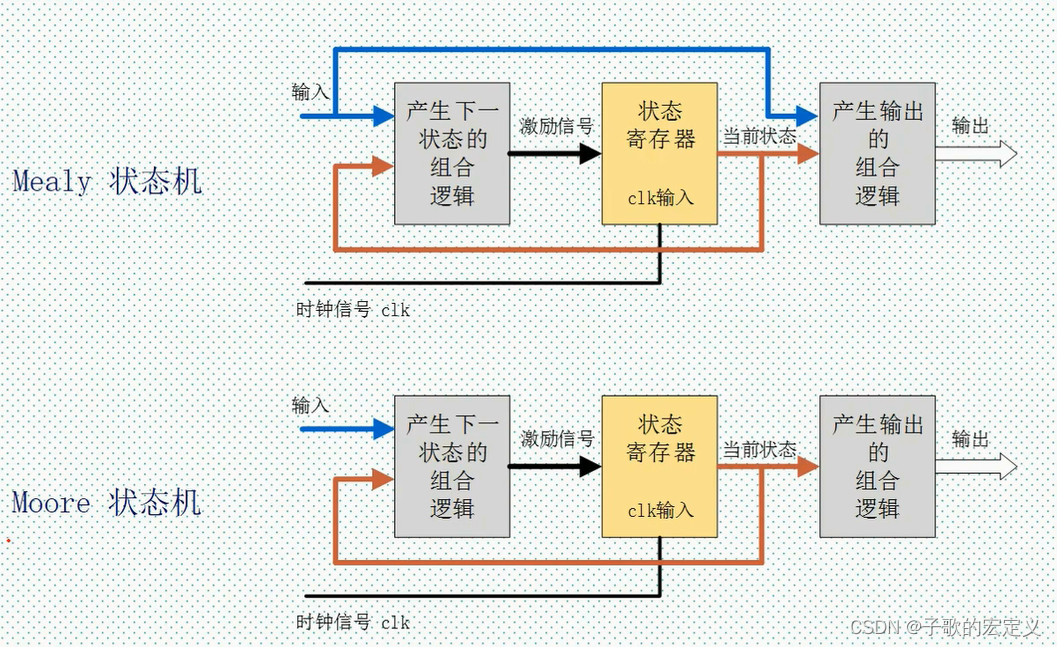

1.模型

状态机,全称是有限状态机(Finite State Machine,缩写为 FSM),是一种在有限个状态之间按一定规律转换的时序电路,可以认为是组合逻辑和时序逻辑的一种组合。

➢ Mealy 状态机:组合逻辑的输出不仅取决于当前状态,还取决于输入状态。

➢ Moore 状态机:组合逻辑的输出只取决于当前状态。

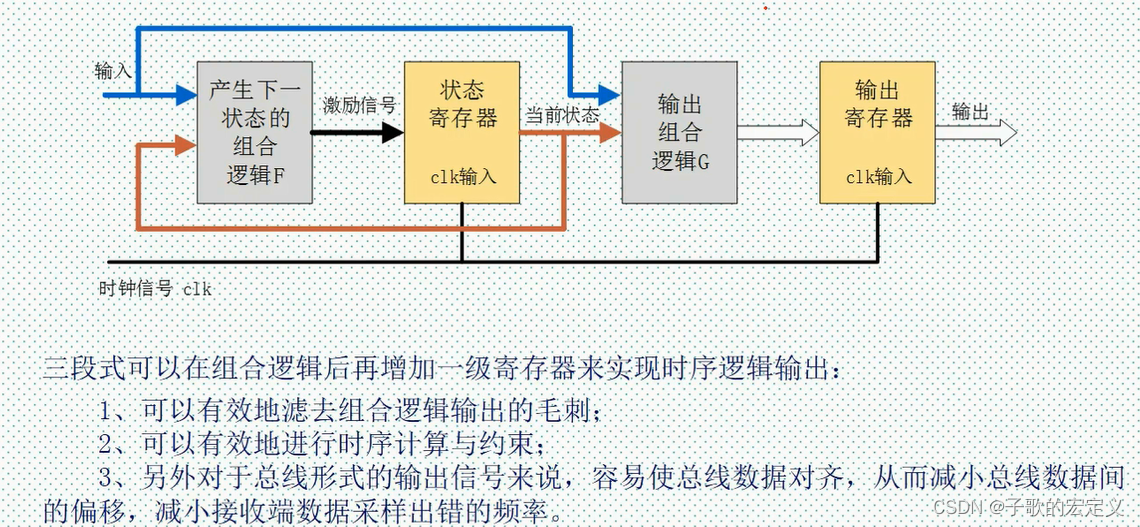

2.设计

四段论

1、状态空间的定义

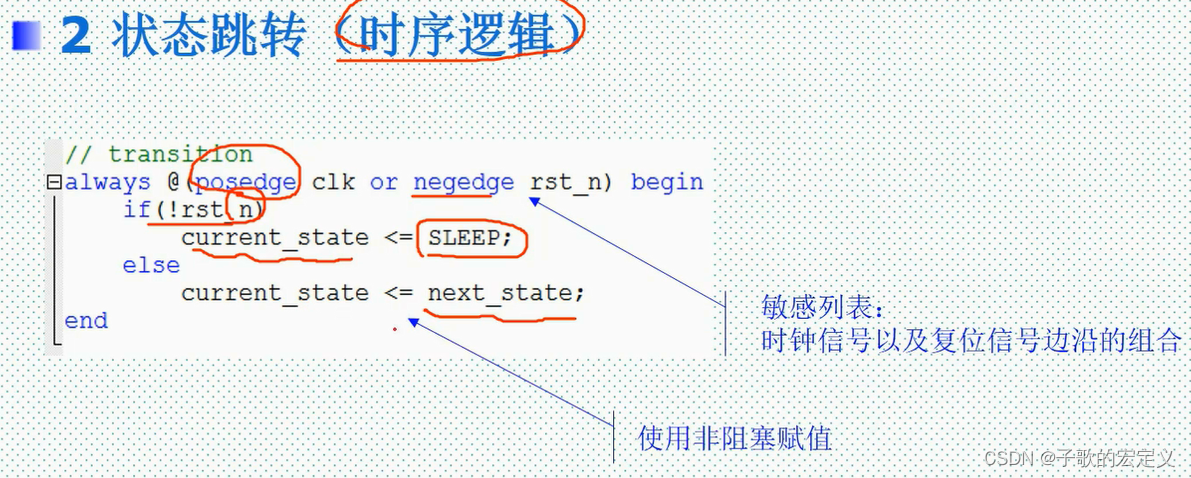

2、状态跳转

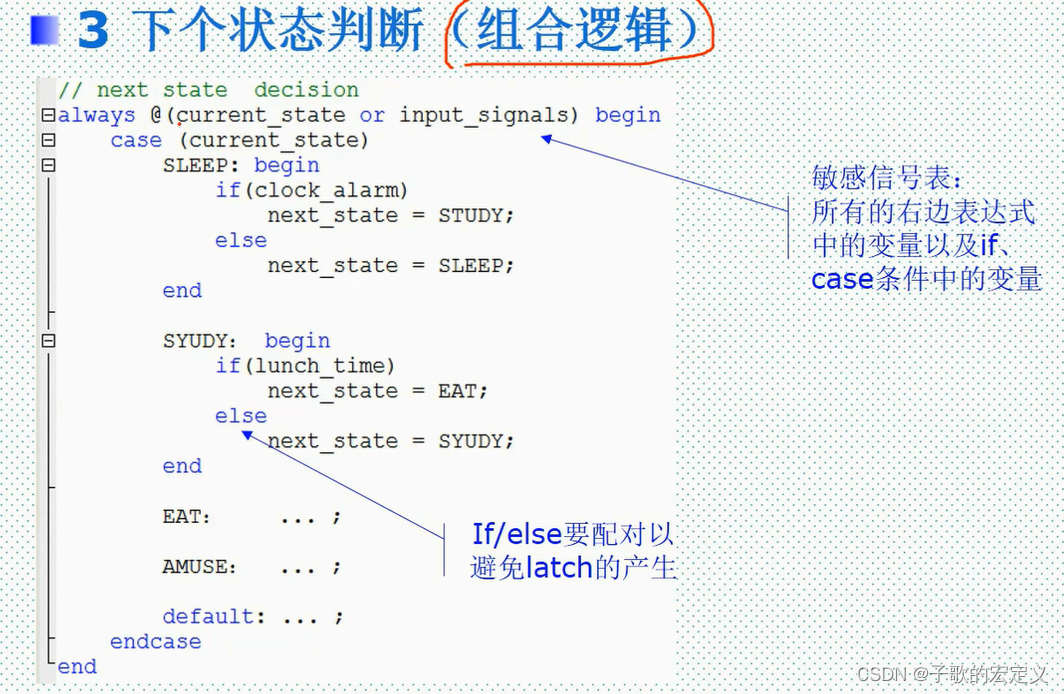

3、下一状态判断

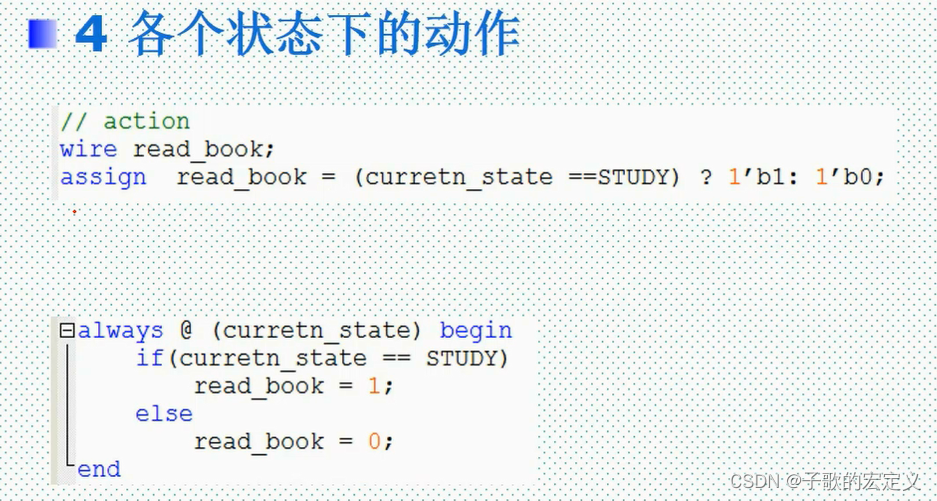

4、各个状态下的动作

总结

并行考虑,组合思维,时序思维很重要

1062

1062

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?