基于FPGA的VGA协议实现

vga

介绍

VGA是一种D型接口,采用非对称分布连接方式,共有15针,分三排,每排5个孔。

●VGA接口管脚表:

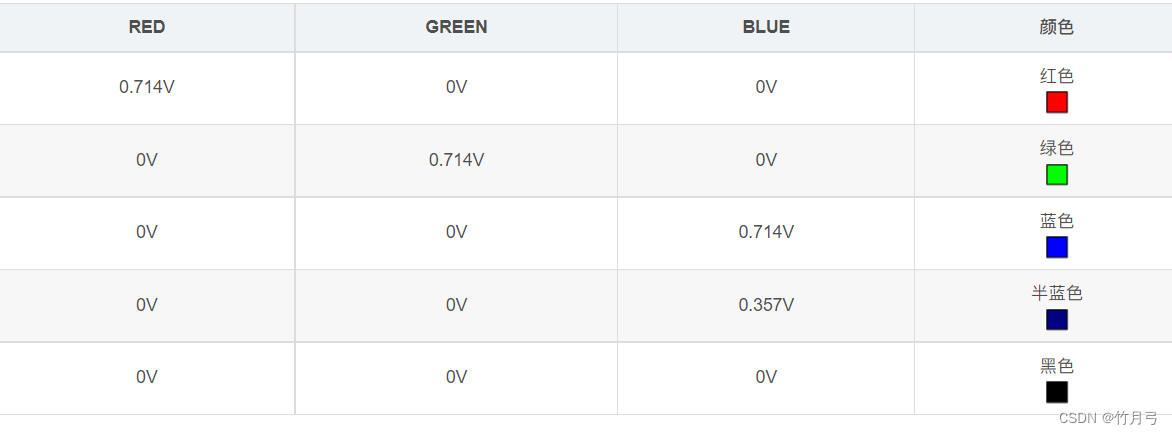

●VGA各种颜色如何实现的

vga通信协议

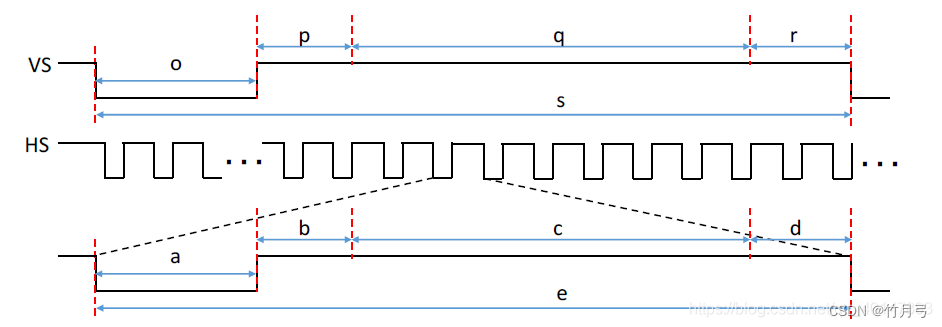

时序

●帧时序:

帧时序的四个部分别是:同步脉冲(Sync o)、显示后沿(Back porch p)、显示时序段(Display interval q)和显示前沿(Front porchr)。其中同步脉冲(Sync o)、显示后沿(Back porch p)和显示前沿(Front porch r)是消隐区,RGB信号无效,屏幕不显示数据。显示时序段(Display interval q)是有效数据区。.

●行时序:

行时序的四个部分分别是:同步脉冲(Sync a)、显示后沿(Back porch b)、显示时序(Display interval c)和显示前沿(Front porchd)。其中同步脉冲(Sync a)、显示后沿(Back porch b)和显示前沿(Front porch d)是消隐区,RGB信号无效,屏幕不显示数据。显示时序段(Display interval c)是有效数据区。

时序解析

显示条纹

各种分辨率的设置

vga_param

`define vga_640_480

`define vga_1920_1080

`ifdef vga_640_480

//执行操作A

`define H_Right_Border 8

`define H_Front_Porch 8

`define H_Sync_Time 96

`define H_Back_Porch 40

`define H_Left_Border 8

`define H_Data_Time 640

`define H_Total_Time 800

`define V_Bottom_Border 8

`define V_Front_Porch 2

`define V_Sync_Time 2

`define V_Back_Porch 25

`define V_Top_Border 8

`define V_Data_Time 480

`define V_Total_Time 525

`elsif vga_1920_1080

//执行操作B

`define H_Right_Border 0

`define H_Front_Porch 88

`define H_Sync_Time 44

`define H_Back_Porch 148

`define H_Left_Border 0

`define H_Data_Time 1920

`define H_Total_Time 2200

`define V_Bottom_Border 0

`define V_Front_Porch 4

`define V_Sync_Time 5

`define V_Back_Porch 36

`define V_Top_Border 0

`define V_Data_Time 1080

`define V_Total_Time 1125

`elsif vga_1024_768

`define H_Right_Border 0

`define H_Front_Porch 24

`define H_Sync_Time 136

`define H_Back_Porch 160

`define H_Left_Border 0

`define H_Data_Time 1024

`define H_Total_Time 1344

`define V_Bottom_Border 0

`define V_Front_Porch 3

`define V_Sync_Time 6

`define V_Back_Porch 29

`define V_Top_Border 0

`define V_Data_Time 768

`define V_Total_Time 806

`else

vga驱动控制

`define vga_1920_1080

`include "vga_param.v"

module vga_ctrl(

input clk ,//时钟信号 //25.2MHZ

input rst_n ,//复位信号

input [23:0] data_disp ,

output reg [10:0] h_addr ,//数据有效显示区域行地址

output reg [10:0] v_addr ,//数据有效显示区域场地址

output reg vsync ,

output reg hsync ,

output reg [7 :0] vga_r ,

output reg [7 :0] vga_b ,

output reg [7 :0] vga_g ,

output wire vga_blk ,

output wire vga_sync ,

output reg vga_clk //25.2MHZ

);

//参数定义

parameter H_SYNC_START = 1,

H_SYNC_STOP = `H_Sync_Time ,

H_DATA_START = `H_Sync_Time + `H_Back_Porch + `H_Left_Border,

H_DATA_STOP = `H_Sync_Time + `H_Back_Porch + `H_Left_Border + `H_Data_Time,

V_SYNC_START = 1,

V_SYNC_STOP = `V_Sync_Time,

V_DATA_START = `V_Sync_Time + `V_Back_Porch + `V_Top_Border,

V_DATA_STOP = `V_Sync_Time + `V_Back_Porch + `V_Top_Border + `V_Data_Time;

//信号定义

reg [11:0] cnt_h_addr ;//行地址计数器

wire add_h_addr ;

wire end_h_addr ;

reg [11:0] cnt_v_addr ;//长地址计数器

wire add_v_addr ;

wire end_v_addr ;

assign vga_sync = 1'b0;

assign vga_blk = ~((cnt_h_addr<`H_Front_Porch + `H_Sync_Time + `H_Back_Porch)||(cnt_v_addr<`V_Front_Porch + `V_Sync_Time + `V_Back_Porch));

always@(posedge vga_clk or negedge rst_n)begin

if(!rst_n)begin

cnt_h_addr <= 12'd0;

end

else if(add_h_addr)begin

if(end_h_addr)begin

cnt_h_addr <= 12'd0;

end

else begin

cnt_h_addr <= cnt_h_addr + 12'd1;

end

end

else begin

cnt_h_addr <= 12'd0;

end

end

assign add_h_addr = 1'b1;

assign end_h_addr = add_h_addr && cnt_h_addr == `H_Total_Ti

vga显示

vga显示

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

457

457

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?