高精度数据采集系统的设计是为了尽量减少来自各种系统组件的误差,如在数据转换器的参考输入上开关瞬态所引入的误差。在逐次逼近寄存器模数转换器(SAR ADC)的情况下,数据转换器内部的电路在整个转换周期内连接和断开不同的容性负载时导致切换瞬态。其他数据转换器,如δ - σ adc和数模转换器(dac),也可以在参考引脚上施加开关瞬态。

图1显示了SAR ADC架构的简化表示。在操作过程中,ADC内部的开关S1和S2控制采集和转换周期。当S1闭合并且S2打开时,由于阻抗变化,输入上会发生瞬态条件。有详细的技术资源讨论如何优化输入电路以最小化输入瞬态的影响,例如TI Design TIPD173的用户指南,该指南展示了用于单端多路复用应用的16位1MSPS数据采集参考设计。但是在本文中,我想重点讨论参考电压输入引脚(VREF)上产生的瞬态及其对系统性能的影响,因为这些瞬态经常被系统级设计忽视。

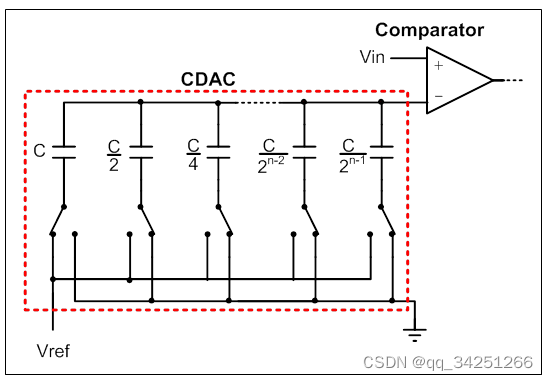

图1:简化的SAR ADC内部架构

SAR ADC的VREF引脚在内部连接到电容DAC (CDAC),在图1中用红色突出显示。图2提供了关于简化CDAC结构的更多细节。CDAC是一个二进制加权电容器阵列,用于确定与参考电压相比最匹配输入电压的数字值。关键是参考输入引脚连接到二进制加权电容器阵列,这可能导致在转换周期中施加到VREF引脚的参考电压发生变化。阵列中的电容器将不处于与参考电压相同的电位,因此当将电容器连接到外部参考电压时,将会有一个大而快速的突刺电流。

图2:内部CDAC架构导致切换电容负载

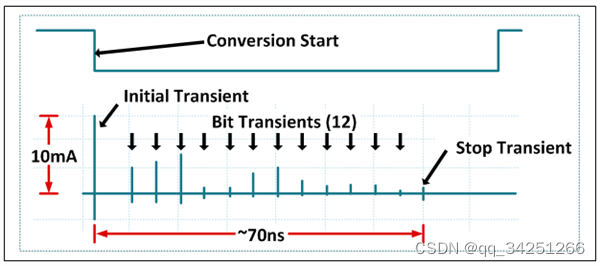

图3显示了在整个转换周期中出现的参考输入电流尖峰,其峰值可达10mA,持续时间非常短(纳秒)。

图3:在SAR ADC的VREF引脚上切换瞬态

为了获得最佳精度,连接到SAR输入端的参考电压需要响应大而快速的电流尖峰。这些快速瞬态开关电流会在电压基准的高输出阻抗处引起电压降。该压降直接影响基准的输出电压,从而影响ADC的VREF引脚的输入电压,导致ADC对输入信号的错误转换。

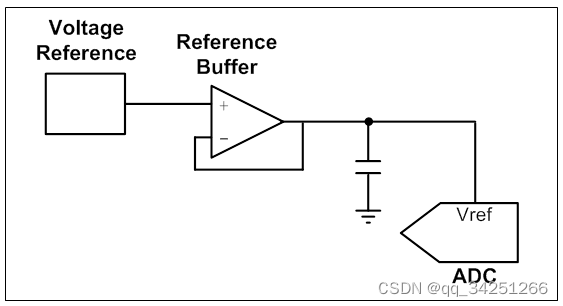

为了使这些开关瞬态引入的误差最小化,参考电压应该在每个电流尖峰之间重新建立到所需的输出电压。考虑到负载非常轻且迟缓,独立电压基准设计用于提供非常准确和稳定的电压。由于这些电流尖峰持续时间很短,幅度很大,因此通常使用高速运算放大器(运放)缓冲基准(见图4)。此外,在引脚处放置电容器可以提供所需的总瞬时电流。

虽然从暂态角度来看,高速运算放大器很好,但它们通常没有针对直流精度进行优化,例如失调电压、线性度和漂移。因此,找到既满足直流精度要求又具有良好瞬态性能的缓冲器可能是一项挑战。在某些情况下,包含两个放大器的放大器拓扑结构将实现这一具有挑战性的目标。我前面提到的数据采集参考设计用户指南更详细地解释了这种拓扑结构,并涵盖了电压基准、缓冲放大器和相关滤波器组件的选择

图4:使用高速放大器的电压基准电路

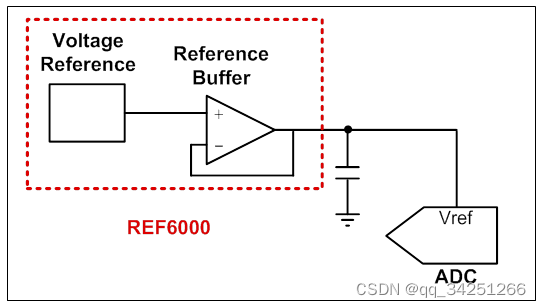

为了简化系统级设计工作,最大限度地减少开关瞬态对参考引脚的影响,TI的REF6000电压基准系列集成了参考缓冲器和参考电压。图5显示了在一个简化的数据采集系统中的这种集成。内部缓冲器经过优化,可以很好地响应数据转换器参考引脚上产生的瞬态类型,并且还针对直流性能进行了优化。此外,这种组合减少了电路板面积,因为它结合了电压基准和基准缓冲器。

图5:使用集成电压基准和基准缓冲器的电压基准电路

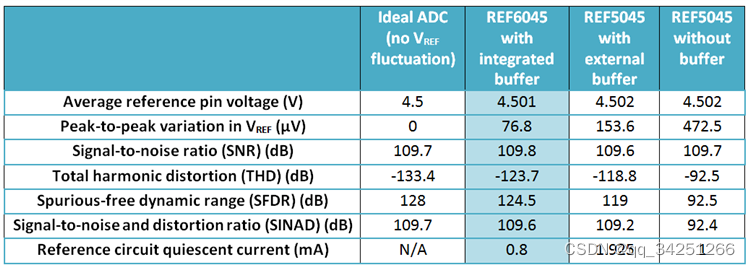

采用这种集成方法,通过为VREF引脚的输入提供高带宽、低输出阻抗、dc优化的解决方案,可以提高ADC的性能。表1比较了理想ADC与具有不同电压基准电路配置的ADC的噪声和失真性能。您可以看到,参考电压没有缓冲驱动会降低性能。将集成参考缓冲与外部缓冲进行比较,具有集成缓冲的参考性能最好。

表1:在1MSPS和10kHz输入频率下,18位ADC采样的各种缓冲配置的ADC性能

在设计高精度数据采集系统时,参考电压电路的设计是很重要的。提高系统整体性能的一种方法是优化处理数据转换器快速开关瞬态的驱动缓冲器,以减少失真和误差。通过将参考缓冲器和参考电压与TI的REF6000系列参考电压集成,我们已经为您解决了这个问题。

译自 https://e2e.ti.com/blogs_/archives/b/precisionhub/posts/why-is-it-so-challenging-to-design-a-voltage-reference-circuit-for-an-adc

文章讨论了在高精度数据采集系统中,SARADC的参考电压输入端(VREF)的瞬态电流如何影响系统性能。通过分析SARADC的内部架构和CDAC的工作原理,强调了参考电压输入需要快速响应大电流尖峰以保持精度。文章提出使用高速运算放大器缓冲基准电压,并介绍了TI的REF6000系列集成电压基准和缓冲器的解决方案,以提高ADC的性能和减少系统设计复杂性。

文章讨论了在高精度数据采集系统中,SARADC的参考电压输入端(VREF)的瞬态电流如何影响系统性能。通过分析SARADC的内部架构和CDAC的工作原理,强调了参考电压输入需要快速响应大电流尖峰以保持精度。文章提出使用高速运算放大器缓冲基准电压,并介绍了TI的REF6000系列集成电压基准和缓冲器的解决方案,以提高ADC的性能和减少系统设计复杂性。

2134

2134

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?