关于FPGA对 DDR4 (MT40A256M16)的读写控制 2

语言 :Verilg HDL

EDA工具:ISE、Vivado、Quartus II

- 关键词: 调用,Verilog HDL,DDR4,MT40A256M16

一、引言

博主将会写一个系列的文章 关于FPGA对DDR4(MT40A256M16)的有效读写控制,最大化FPGA对DDR4的读写控制。首先将对DDR4的技术文档进行研读,注重DDR4的读写操作、刷新时间等。

二、DDR4的简介

DDR4 SDRAM 是一种高速的、基于 CMOS 技术的动态随机存取存储器(DRAM)。它内部配置为具有 16 个存储体的 DRAM,这些存储体被组织成 4 个存储体组,每个组包含 4 个存储体。这种设计允许 DDR4 SDRAM 实现高速操作,因为它采用了 8n-预取架构,结合了接口设计,能够在每个时钟周期的 I/O 引脚处传输两个数据字。

512M×8的DDR4,功能框图如下所示(源文档图片就缺失了一块)

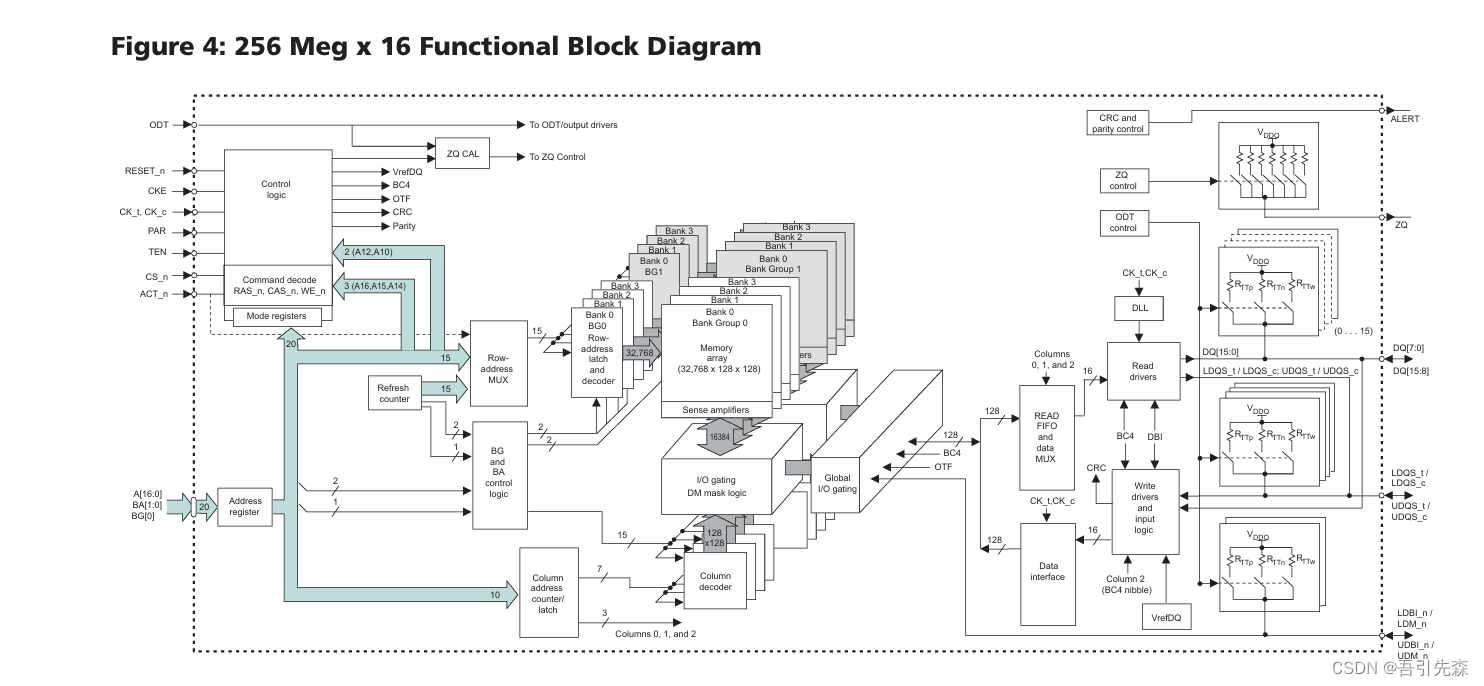

256Mx16的DDR4,功能框图如下所示

256Mx16的DDR4,功能框图如下所示

每片DDR4有四个BG ,每个BG有四个bank,也就是有16个bank,bank可以译为组。

每片DDR4有四个BG ,每个BG有四个bank,也就是有16个bank,bank可以译为组。

加粗样式

加粗样式#### 三、DDR4的管脚及含义

1、VDDQ: DQ 电源供应,为内存模块的数据线提供电源。

2、VPP: DRAM 激活电源供应,用于某些特定的内存操作。

3、VDD: 电源供应,为内存模块的大部分部分提供电源。

4、VSS: 地线,提供参考的零电位。

5、VSSQ: DQ 地线,为数据线提供参考的零电位。

6、VREFCA: 为控制、命令和地址引脚提供参考电压。

7、RESET_n: 复位信号,低电平有效,用于初始化或重置内存模块。

8、CKE: 时钟使能信号,控制内存模块的时钟输入缓冲器和输出驱动器。

9、CS_n: 芯片选择信号,低电平有效,用于选择特定的内存模块。

10、ACT_n: 激活信号,与 CS_n 结合使用,用于激活内存中的特定行。

11、RAS_n/A16 和 CAS_n/A15: 分别用于内存的行地址和列地址的激活和访问。

12、WE_n/A14: 写使能信号,低电平有效,用于控制数据的写入操作。

13、BA[1:0] 和 BG[1:0]: 分别为bank地址和bank组地址输入,用于选择内存中的特定bank或bank组。

14、A[17:0]: 地址输入引脚,提供行地址和列地址,用于访问内存中的特定位置。

15、DQ[15:0]: 数据输入/输出引脚,用于数据的读写操作。

16、DM_n: 数据掩码信号,用于在写操作期间屏蔽数据。

17、ODT: 片上终止信号,用于控制内存模块的输出终止电阻。

18、PAR: 奇偶校验信号,用于命令和地址的奇偶校验。

19、TEN: 测试模式使能信号,用于进入内存的测试模式。

20、ALERT_n: 警告输出信号,用于指示内存模块内部的特定警告或事件。

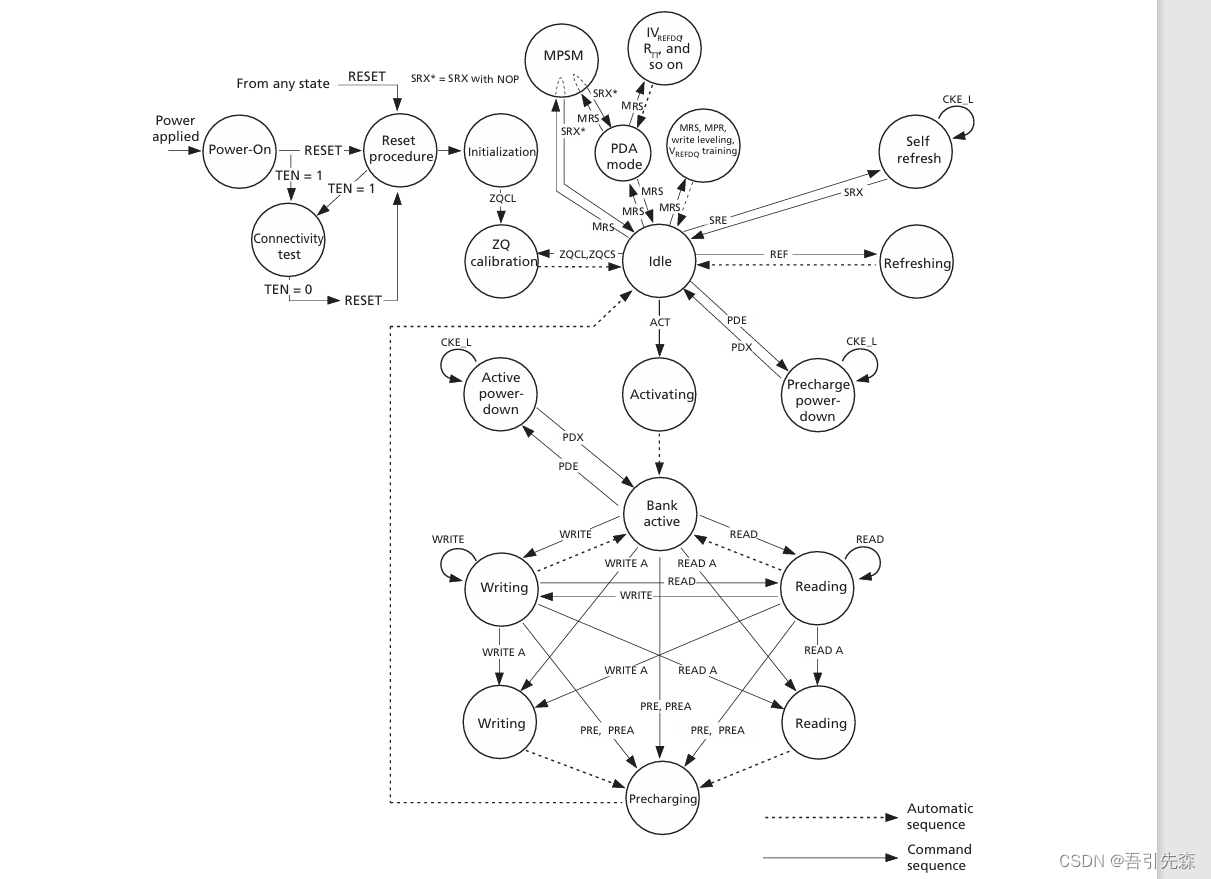

四、DDR4 SDRAM状态框图

描述了 DDR4 SDRAM 可能的状态转换以及控制这些转换的命令。这个状态图是一个高层次的概述,注意不涉及多个存储体(bank)、片上终止(on-die termination)的启用或禁用等。

在 DDR4 SDRAM 的操作中,状态图通常包括以下一些状态和转换:

1、Bank active (存储体激活): 存储体已被激活,准备进行读写操作。

2、Reading (读取): 正在进行数据读取操作。

3、Writing (写入): 正在进行数据写入操作。

4、Activating (激活): 存储体正在被激活,准备访问。

5、Refreshing (刷新): 存储体正在执行刷新操作,以保持数据的完整性。

6、Self refresh (自刷新): 内存模块正在自刷新状态,以节省功耗。

7、Idle (空闲): 内存模块没有进行任何操作,等待命令。

8、Active powerdown (活动功耗降低): 存储体在活动状态下进入功耗降低模式。

9、Precharge powerdown (预充电功耗降低): 存储体在预充电状态下进入功耗降低模式。

10、ZQ calibration (ZQ 校准): 内存模块正在进行 ZQ 校准,以确保信号完整性。

状态转换由各种命令触发,例如:

1、ACT: 激活存储体。

2、READ: 从存储体读取数据。

3、WRITE: 向存储体写入数据。

4、PRE: 预充电,关闭当前激活的存储体。

5、PREA: 预充电所有存储体。

6、REF: 刷新存储体。

7、SRE: 进入自刷新状态。

8、SRX: 退出自刷新状态。

9、ZQCL: 执行 ZQ 校准。

这些状态和命令是 DDR4 SDRAM 正常操作的一部分,确保内存模块可以高效、可靠地执行数据存储和检索任务。状态图帮助设计者和工程师理解内存模块的行为,并在设计系统时考虑到这些行为。

85

85

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?