2.1 programmers model

2.1.1 processor mode and privilege levels for sw exec

as we all kown, cm7 has 2 modes: thread and handler.

reset -> thread --exception-->handler--finished-->thread

privileged can use all instruction and access all sources,but unprivileged not

handler alwawsy privileged and thread use CONTOL register to control level

2.2 stacks

thread use MSP or PSP by use CONTORL register, handler use MSP

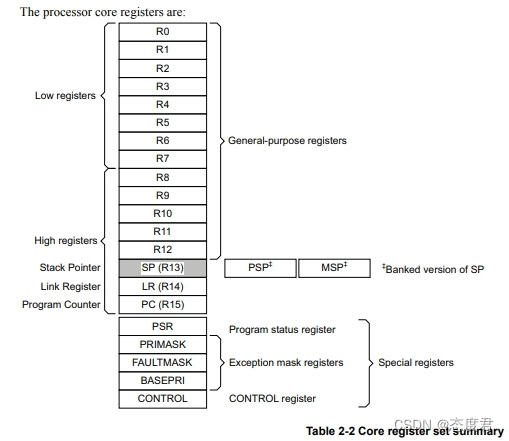

2.1.3 core registers

R0-R12:general_purpose register

SP(R13):msp or psp

LR(R14):link register,stores return information for subroutines,function calls,and exceptions

PC(R15):program counter ,contains the current program address

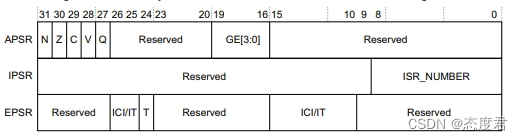

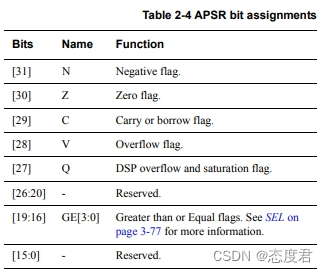

PSR:Program Status Register

2.1.4 Exceptions and interrupts

nvic and exception

2.1.5 data types

instuction memory and private peripheral bus always little-endian

2.1.6 CMSIS

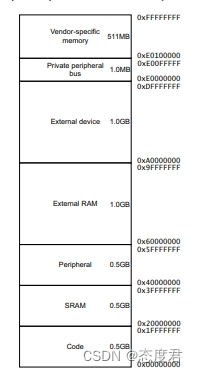

2.2 memory model

for STM32H7 code from 0x08000000 and for RT1052 code from 0x60000000

(external ram)address

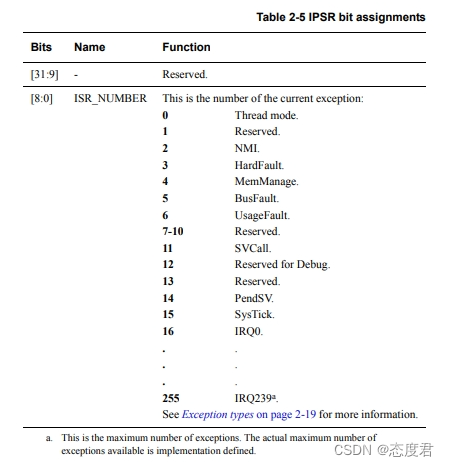

2.3 exception model

2.3.1 exception states

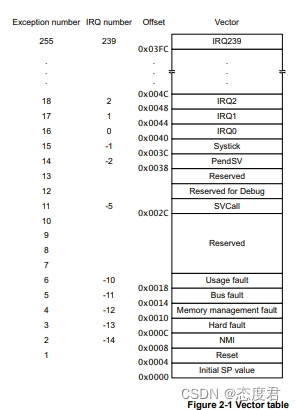

2.3.2 exception types

reset:-3

NMI:-2

HardFault:-1

memmanage :

busfault:

usagefault:

SVCall:

Pendsv:

Systick:

interrupt:

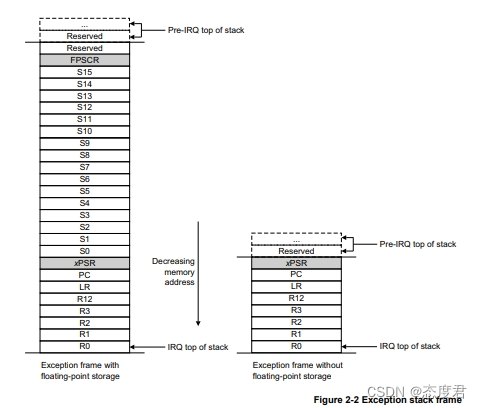

入栈:发生打断时,将会产生压栈动作如上,此时PC保存着程序返回的位置,

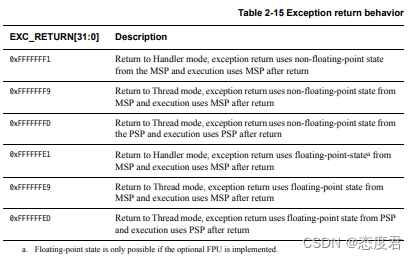

用于退出打断子程序后返回正常处理的app或者说线程函数位置,而LR中写入的是所谓的

“EXC_RETURN”value,从中我们可以看出打断子程序进入前的操作模式(线程或中断)

以及使用的栈帧(MSP还是PSP)。

2.4 faults handling

subset of exceptions:

bus error: instruction fetch or vector table load. data access

internally-detected error such as undfined instrcution

attempt to exec instruction from XN

MPU detect fault

441

441

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?