前言

本文主要记录学习arm的心得体会

MMU( Memory Management Unit)

主要功能:

-

地址转换(

address translation):

虚拟地址->物理地址,用于linux多任务系统,每个应用都是使用独立的地址空间 -

访问权限(

access permission)

对于指令和数据的访问, 可能的结果如下:

• no access

• read-only

• write-only

• read/write. -

内存属性的设置(

memory attribute determination and checking)

地址转换

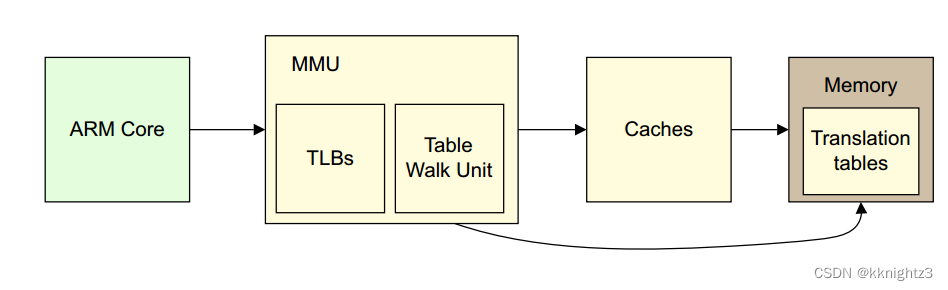

图片1.CPU访问内存过程

Processor 访问内存数据的流程如上图,首先通过MMU将虚拟地址转换为物理地址,然后看是否有cache hit,若是cache miss的话,最后在memory中获取数据。

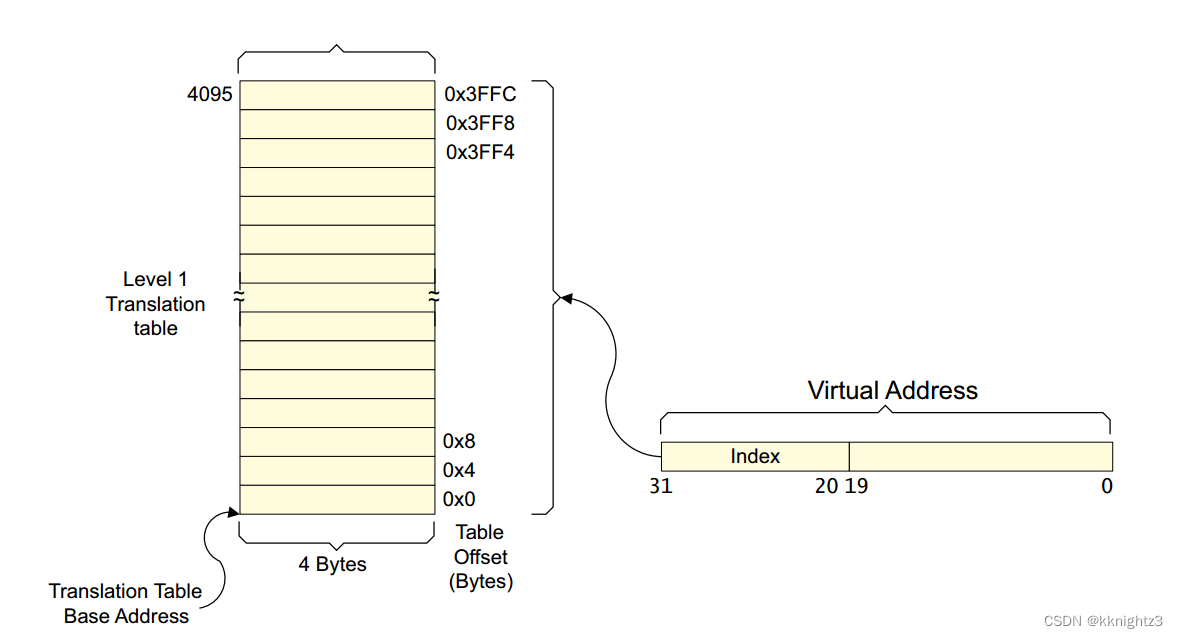

ARM MMU支持具有两个级别的多级翻译表架构,分别是一级(L1)和二级(L2)翻译表。除非实现了大物理地址扩展,否则L1和L2翻译表都使用特点如下的短描述符翻译表格式:

32bit页面描述符。- 最多两级的翻译表。

- 支持32位物理地址。

- 支持以下内存大小:

16MB或1MB的区块。64KB或4KB的页面大小。

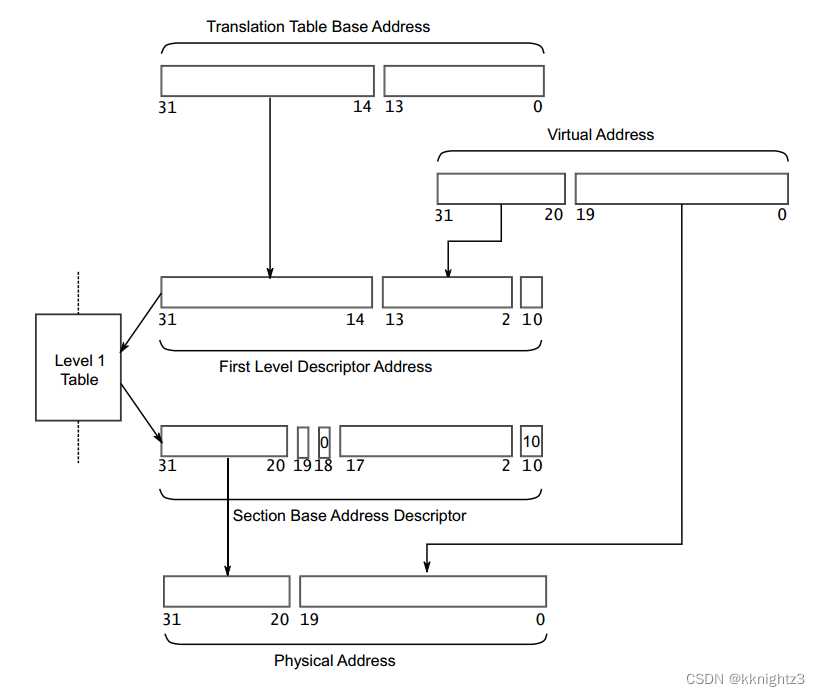

图片2.虚拟地址跟L1 table关系

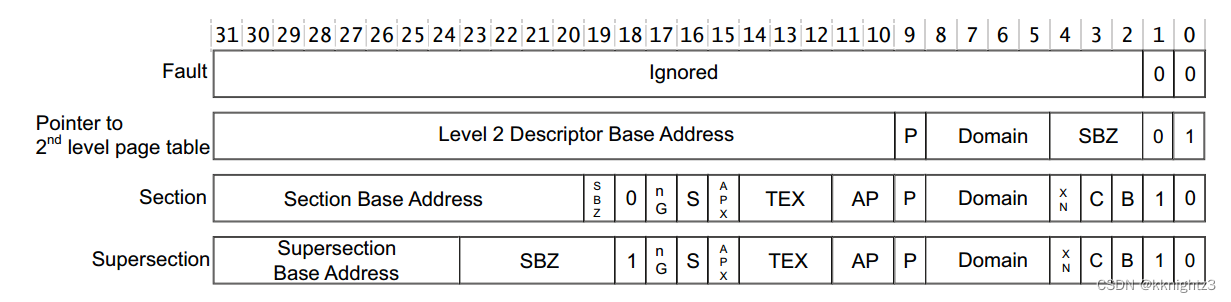

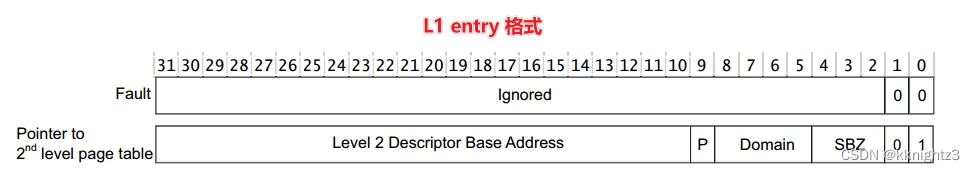

图片3.L1 translation entry格式

其中,L1 translation table entry 可以是以下四种可能的类型之一:

- 一个1MB区块翻译条目,将1MB的区域映射到一个物理地址。

- 一个指向L2翻译表的条目。这使得一个1MB的内存块可以被细分成多个页面。

- 一个16MB的超级区块。这是一种特殊类型的1MB区块条目,它在翻译表中需要16个entry,但可以减少为该区域分配的翻译旁路缓存(TLB)中的条目数量。

- 一个生成中止异常的错误条目。这可以是预取中止或数据中止,取决于访问类型。这实际上指示了未映射的虚拟地址

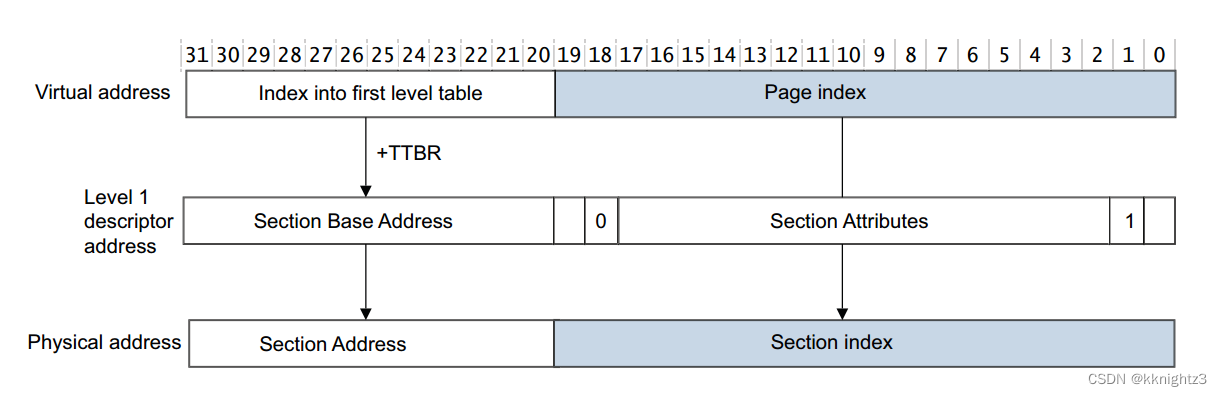

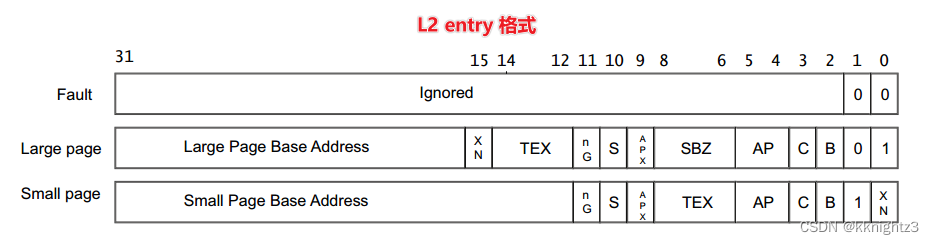

图4.L1 entry为section转换过程

L1 entry为section的地址转换过程如下(如图4所示):

a.假设TLB Base Address在0x12300000

b.CPU要获取 虚拟地址0x00010000位置的数据,此时offset是0x001(虚拟地址高12bit),此时虚拟地址对应的L1 entry在 0x12300000+offset*4=0x12300004

c.根据0x12300004地址的数据,按照TLB L1 entry格式进行解析即可获取实际物理地址

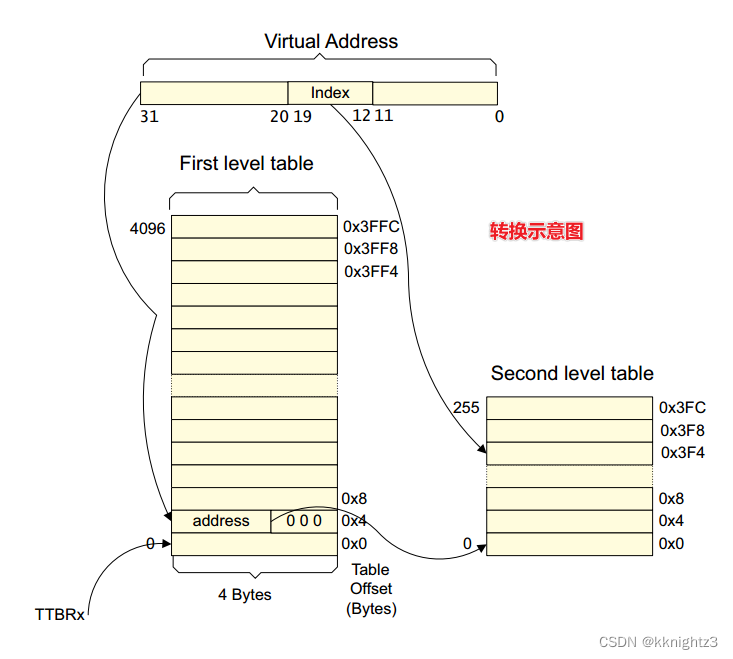

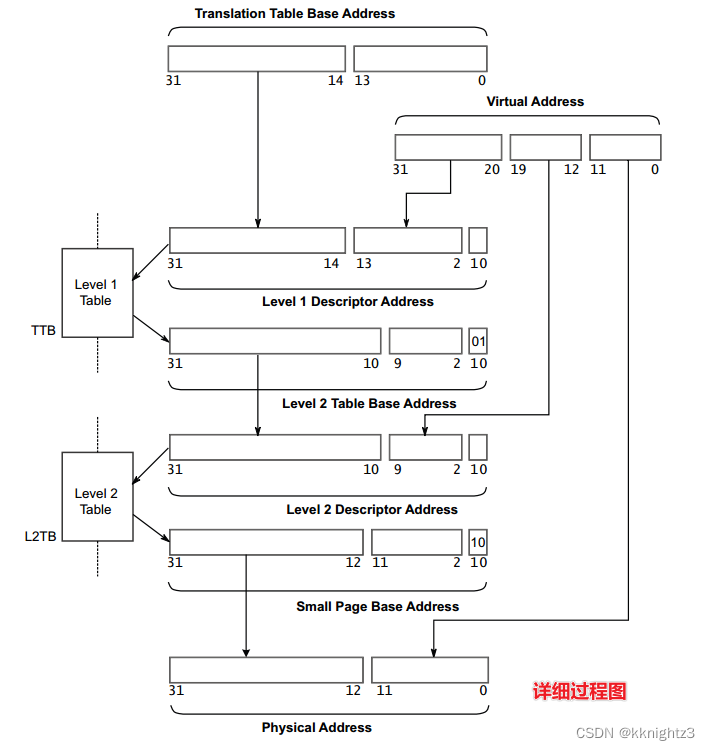

图5.L1 entry为 L2 table转换过程

L1 entry为 L2 table的地址转换过程如下(如图5所示):

a.L1 table base address结合虚拟地址高12bit,生成地址A,通过A即可获取L2 table base address

b.L2 table base address 结合虚拟地址中间8bit,生成地址B

c.通过地址B获取内容的高20bit结合虚拟地址的低12bit,即可获得物理地址

MMU中有Translation Lookaside Buffer,用于缓冲最近使用的page(ps:跟cache不是一个东西,都起到缓冲作用)

MMU被失能时,内存访问会如下被对待:

1.所有数据访问作为Non-cacheable和Strong-orderd

2.指令访问,看SCTLR.I配置,SCTLR.I = 0时,所有指令访问都是Non-cacheable,SCTLR.I = 1时,所有指令访问都是cacheable的

1704

1704

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?