SIGSIM-PADS 2024 Paper CXL论文阅读笔记整理

问题

传统数据中心架构中,内存和计算资源绑定,随着内核数量的增加,当前的内存架构已经接近其容量和带宽扩展极限。此外,由于内存使用和分配的不平衡,面临着内存利用不足的问题[30]。

为此提出了软件内存分解,使用RDMA(远程直接内存访问)在不同服务器之间共享可用内存资源[3,11]。然而,软件分解涉及复杂的调度或负载平衡,需要在服务器之间进行大规模的数据移动[3,19],并且只允许在页粒度上进行远程内存访问,会产生显著的尾延迟。

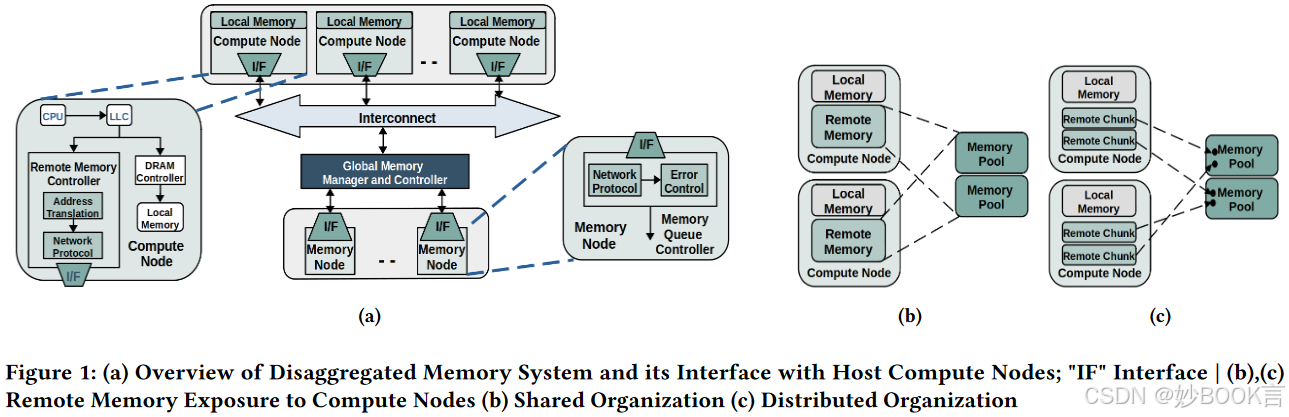

硬件内存分解是一种新兴的方法。它包括多个独立的计算节点和远程内存池,并通过高速缓存一致性互连协议(如CXL)进行连接。计算节点有少量的本地内存,主要依赖远程内存来满足其内存需求。内存池以扁平地址结构组织,在最后一级缓存(LLC)未命中时通过互连协议以缓存行粒度进行访问。

但由于缺少相应的硬件设备,难以搭建真实分离式内存系统(DMS)进行研究,需要通过相应的模拟器。

本文方法

本文介绍了DRackSim,一种用于可扩展分解存储系统的模拟器,主要模拟多个计算节点、内存池、本地/全局内存管理器和用于一致内存访问的网络互连。

-

应用级仿真方法模拟无序x86多核处理器和计算节点处的多级缓存层次结构。

-

基于队列的方法模拟网络接口,以多粒度处理远程内存访问。

-

为内存池中的远程地址空间建模了一个全局内存管理器。

-

通过声明DRAMSim2的多个实例,集成了一个修改后的DRAMSim2来执行本地/远程内存模拟。

开源代码:https://github.com/Amit-P89/-DRackSim/tree/main

根据Gem5和硬件原型严格验证DRackSim子系统。最后,通过对分解内存系统的各种用例场景进行建模来探索设计空间,并评估它们在各种HPC和云基准测试中的性能。

总结

针对分离式内存系统,本文提出了一个模拟器DRackSim,模拟多个计算节点、内存池、本地/全局内存管理和CXL网络互连。(1)使用Intel的PIN工具生成指令,模拟无序执行的多核x86流水线和计算节点的多级缓存结构。(2)基于队列模拟CXL,以缓存行和页面粒度处理远程内存访问。(3)集成DRAMSim2进行本地和远程内存的模拟。(4)引入一个全局内存管理器,负责远程地址空间的分配和管理。

2028

2028

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?