目录

开发环境:

FPGA: cyclone iii

软件:quartus ii13.1+modelsim,matlab2016b

语言:Verilog HDL

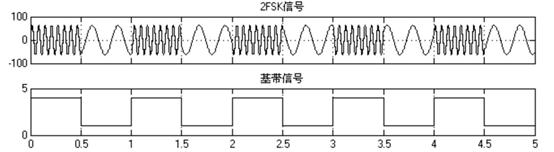

一、2FSK介绍

FSK是信息传输中使用得较早的一种调制方式,它的主要优点是:实现起来较容易,抗噪声与抗衰减的性能较好。国际电信联盟(ITU)建议在传输速率低于1200b/s时采用2FSK体制,其在中低速数据传输中得到了广泛的应用。所谓FSK就是用数字信号去调制载波的频率。

调制方法:2FSK可看作是两个不同载波频率的ASK已调信号之和。

解调方法:相干法和非相干法。

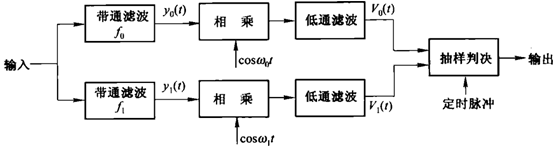

1、相干解调:

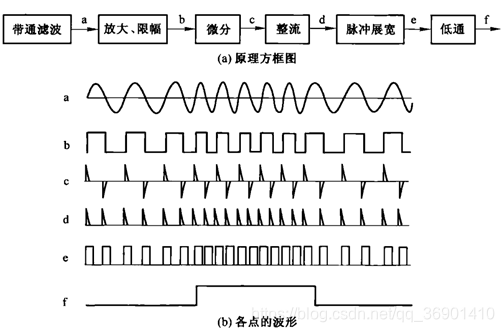

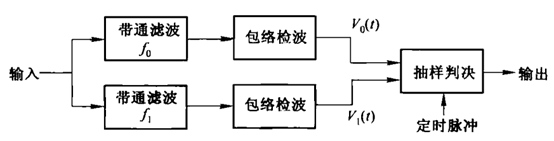

2、非相干解调

二、FPGA生成2FSK方法

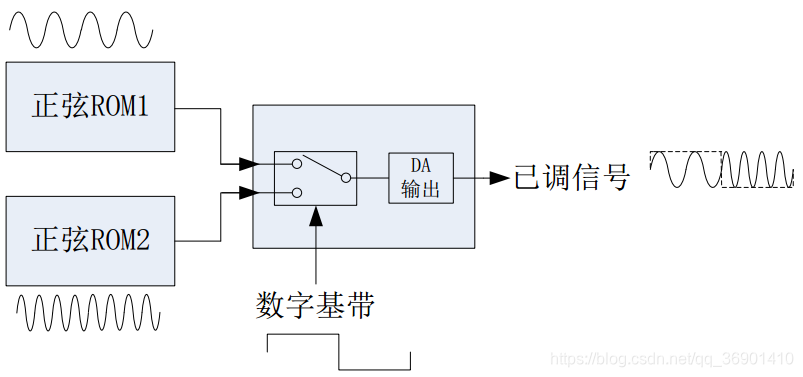

如图所示,2FSK产生的方案,利用基带信号控制DA的ROM表,从而实现FSK调试。

1、正弦ROM表产生

下面详细讲解下如何生成ROM表。

正弦ROM表应该有这样的功能:输入时钟信号,输出幅度值(数字)。然后输出的幅度送给DA让其输出实际对应的模拟电压信号。

想要有这样的功能,首先正弦rom表中要存储正弦数值,以mif的形式导入到创建的rom IP核中;然后创建计数器使其根据时钟信号生成地址,对应为rom表中数据的存储位置。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3201

3201

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?