此系列博客,仅对Xilinx平台PS端(ARM部分)开发做介绍,不对PL(FPGA)做过多介绍。

目录

一.Xilinx Ultra-MPSOC系列芯片

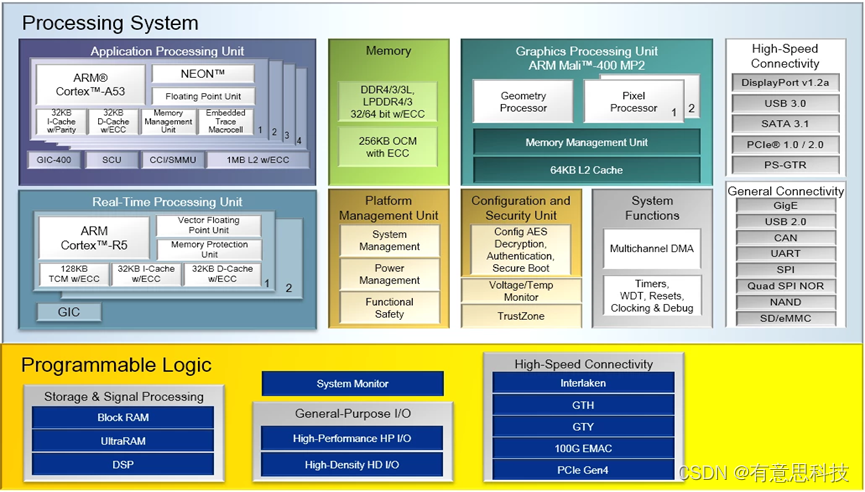

芯片为Xilinx公司的UltraScale+ MPSoC系列SOC。其架构为ARM+FPGA,符合公司现有项目架构。其中ARM采用多核Cotex-A53+Cotex-R5架构,支持每个内核同时运行不同的操作系统。

PMU: platform management unit, 平台管理单元

CSU: configuration security unit, 配置安全性单元

二.开发流程

2.1 PS端开发

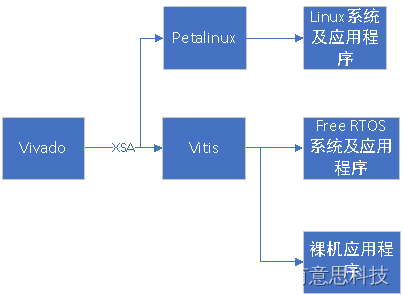

Xilinx公司提供了一整套软件开发工具,可完成包括Linux,FreeRTOS系统的构建,裸机程序的开发,调试等。

1.使用Vivado生成硬件描述(xsa)文件。

2.基于XSA文件,使用Petalinux工具完成Linux系统的U-boot,Linux Kernel,设备树,文件系统等。

3.基于XSA文件,使用Vitis开发工具完成FreeRTOS系统及应用程序,裸机应用程序的开发及调试。

2.2 PL 端开发 - Vitis-HLS

Vitis™ HLS 是一种高层次综合工具,支持将 C、C++ 和 OpenCL™ 函数硬连线到器件逻辑互连结构和 RAM/DSP 块上。Vitis HLS 可在Vitis应用加速开发流程中实现硬件内核,并使用 C/C++ 语言代码在 Vivado® Design Suite 中为赛灵思器件设计开发 RTL IP。

在可编程逻辑中实现和最优化 C/C++ 语言代码以及实现低时延和高吞吐量所需的大部分代码修改操作均可通过 Vitis HLS 工具来自动执行。在应用加速流程中,Vitis HLS 的基本作用是通过推断所需的编译指示来为函数实参生成正确的接口,并对代码内的循环和函数执行流水打拍。Vitis HLS 还支持自定义代码以实现不同接口标准或者实现特定最优化以达成设计目标。

三.启动流程

3.1 预配置阶段(Pre-configuration)

预配置阶段CSU尚未启动,由PMU完全控制,但是执行的是PUM ROM里面代码,ROM里面的代码是固化的,用户无法修改,所以我们无法干预这一阶段的任何行为。

PMU处理所有复位和唤醒过程。上电复位用于复位CSU和PMU,因为它们负责调试,系统和软件复位。。

初次启动期间将执行下列步骤:

• 通过上电复位 (POR) 将 PMU 从复位状态唤醒。

• PMU 执行来自 PMU ROM 的代码。

• PMU 初始化 SYSMON 和启动所需的 PLL、清空低功耗域和全功耗域, 并释放 CSU 复位。

这阶段结束的标志是CSU复位的释放。

3.2 配置阶段(Pre-configuration)

在配置阶段CSU开始工作,BootROM(CSU ROM代码的一部分)解释boot header以配置系统,并将PS的FSBL(first-stage boot loader)代码加载到片内RAM(on-chip RAM, OCM)中(无论是在安全还是非安全启动模式)。系统根据BOOT Header的内容选择在CPU(Cortex-A53)还是RPU(Cortex-R5)上执行。负责初始化必要的时钟、内存和外设,加载Bit文件和用户代码等。

在boot过程中,CSU还将PMU用户固件(PMU Firmware)加载到PMU RAM中,以与PMU ROM一起提供平台管理服务。PMU的Firmware不是必须的,但是大多数基于Xilinx的FSBL和系统软件的系统都存在PMU Firmware。

这个阶段FBSL可以通过PCAP接口从PS配置PL,但是这只是一个可选的操作。因为其实我们也可以在PS端的操作系统启动之后再动态配置PL端。有时,可能只需要 FSBL 在启动过程中加载部分 PL。随后,有必要在系统生命周期里继续对 PL 进行部分重配置。

在 PMU 释放 CSU 后, CSU 将执行以下操作:

• 检查并判定 FSBL 或用户应用是否需要进行身份验证。

• 执行身份验证检查, 并且只有在身份验证检查通过以后才继续执行。然后, 检查镜像是否包含任何已加密的分区。

• 如果 CSU 检测到分区已加密, 那么 CSU 会执行解密并初始化 OCM、判定启动模式设置、执行 FSBL 加载和可选PMU 固件加载操作。

• 执行 CSU ROM 代码后, 它会将控制权交给 FSBL。 FSBL 使用 PCAP 接口来对含比特流的 PL 进行编程。

随后,在后配置阶段 FSBL 会负责对系统进行操作。

3.3 后置阶段(Pre-configuration)

开始执行FSBL之后,CSU ROM代码进入后配置阶段,该阶段负责系统干预响应。 CSU硬件提供持续的硬件支持,以验证文件,通过PCAP配置PL,存储和管理安全密钥以及解密文件。

这个阶段会启动SSBL,就是Linux的bootloader,开始引导启动Linux系统。

四. 官方对环境资源要求

CPU:8核 2G

RAM:8GB

ROM:100G(个人推荐200G以上)

系统:Win10 64位;Ubuntu Linux 18.03.31 LTS; 18.03.32 LTS, 18.03.33 LTS; 18.03.34 LTS; 16.04.5, 16.04.6, 18.04.1, 18.04.2, 18.04.3, 18.04.4,18.04.5, 20.04 18.03.35 LTS; and 20.04 LTS,20.03.31 LTS, 20.03.32 LTS, 20.03.33 LTS (64-bit)

972

972

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?