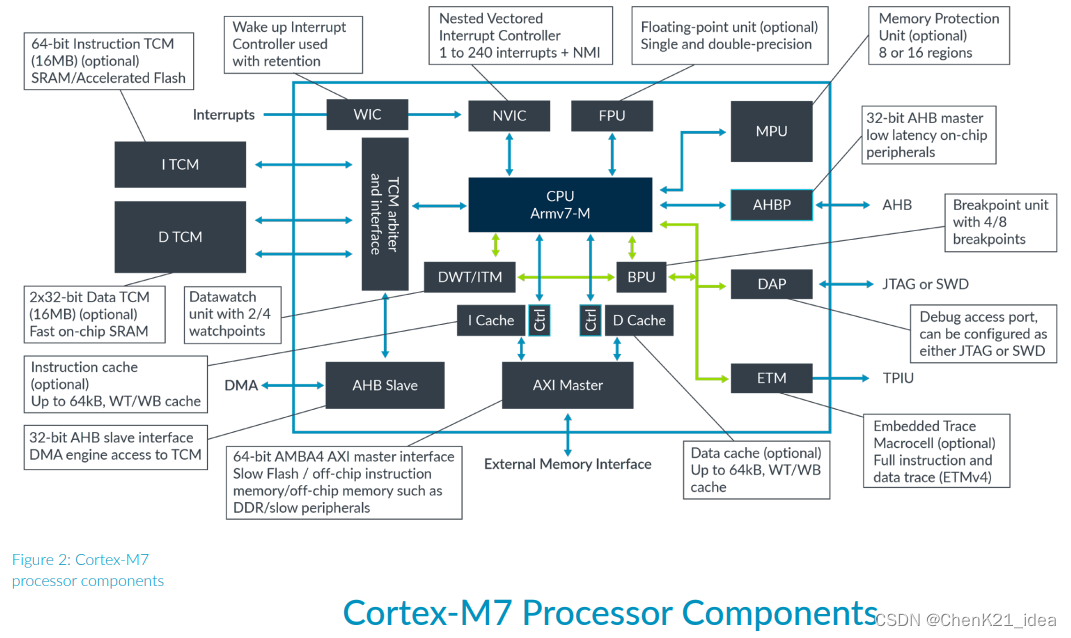

【1】Cortex-M7属于Cortex-M系列,基于ARMv7-M架构,具有32位处理能力。采用了Superscalar技术,可以在一个时钟周期内执行多条指令。

【2】Cortex-M7与Cortex-M4之间的区别:

2.1 Cortex-M7提供了更高的运算性能。它具有六级流水线和双发射超标量架构,可以在一个时钟周期内执行两条指令,而Cortex-M4采用三级流水线,每个时钟周期只能执行一条指令。

2.2 Cortex-M7支持双精度浮点运算,而Cortex-M4只支持单精度浮点运算。

2.3 Cortex-M7有分离的指令和数据缓存,更有效地减少处理器和内存之间的延迟,提高处理器的性能。而Cortex-M4则没有这个功能。

2.4 Cortex-M7支持错误检测和纠正,增强系统的可靠性和鲁棒性,Cortex-M4不支持。

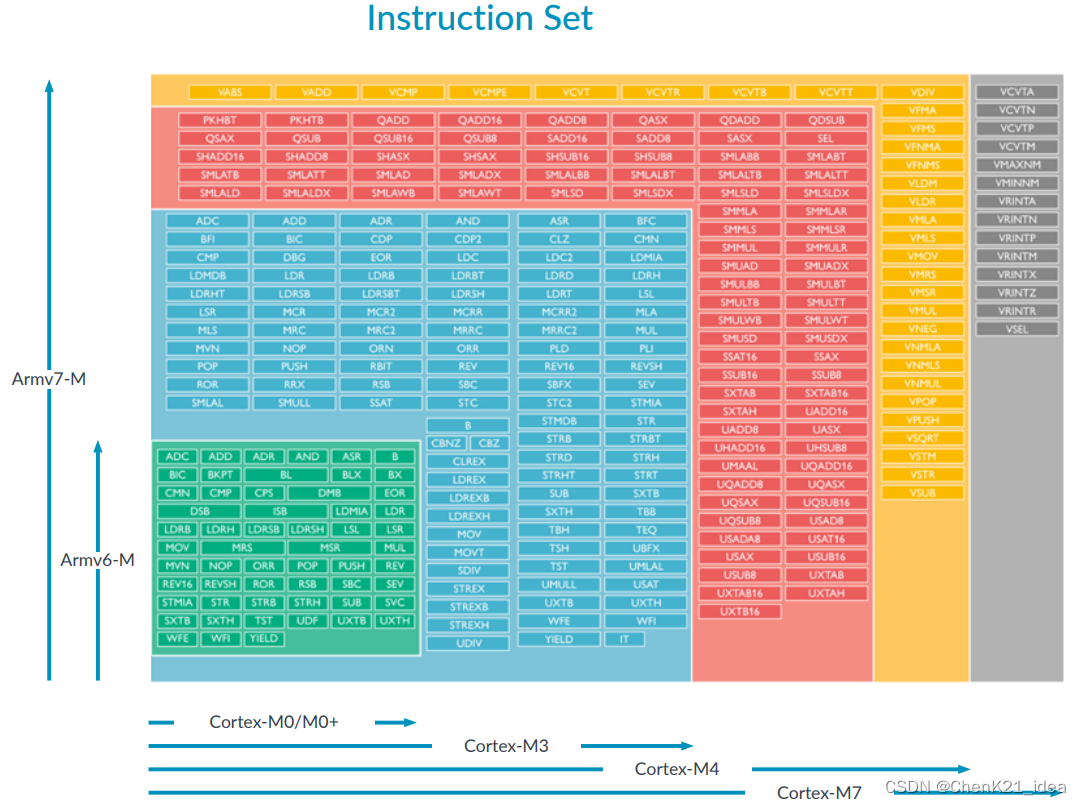

2.5 指令集

【3】Cortex-M7 TCM(Tightly Coupled Memory,紧密耦合内存)

3.1 Cortex-M7具有与两个TCM区域,即TCM代码区(ITCM, Instruction TCM)和TCM数据区(DTCM, Data TCM),TCM是处理器内部的高速存储器,可以用于存放代码与数据,以提高系统性能。

3.2 TCM分为两种,ITCM和DTCM,这两块内存区域一般用于特殊用途,比如某些对时间要求非常严格的代码,存放在ITCM中执行,以此提高运行速度;某些需要频繁存取的数据,可以放在DTCM中,以此节省存取时间。

3.3 TCM与Cache处于平行结构,即在二者均工作期间,若CPU所需的数据或指令在Cache中,则通常不会在TCM中。

3.4 当前RTOS运行在ITCM,DTCM用作栈功能。

【4】Cortex-M7与Cache的区别

4.1 Cache是一种用于存储最近访问的数据的高速缓存,Cache存储器通常是外部存储器的一部分,并且可以存储任意数据,包括代码和数据。

4.2 TCM用于处理器内部的高速存储器,存储最常用代码和数据,以提高系统性能;Cache则用于存储最近访问的数据,以减少对外部存储器的访问次数,提高系统性能。

4.3 TCM是处理器内部的存储器,不需要外部存储器的支持。Cache 则需要外部存储器的支持,并且需要使用一些特殊的硬件逻辑来管理缓存。

【5】Cortex-M7 MPU

该MPU一共支持16个regions(0-15),优先级依次升高,region15配置的优先级最高,可以覆盖前面region的配置属性。每个region的最小size为32bytes,最大支持4G范围配置。

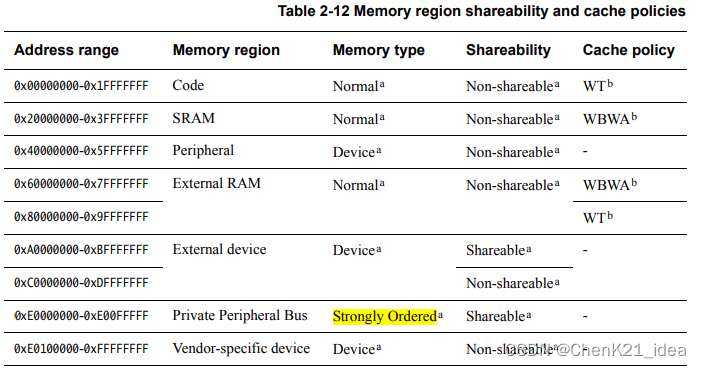

【6】Memory Type

6.1 Device:该memory类型是由连带效应(side-effects)的,即对一个地址的数据的操作可能会影响到另一个地址中的数据值。Device空间要求较高,数据不允许被Cache缓存,否则导致系统功能紊乱。

6.2 Normal:该memory类型是不具有连带效应的,即地址之间的操作互不干扰,Normal空间的数据可以被Cache缓存。

6.3 MPU Region Attribute

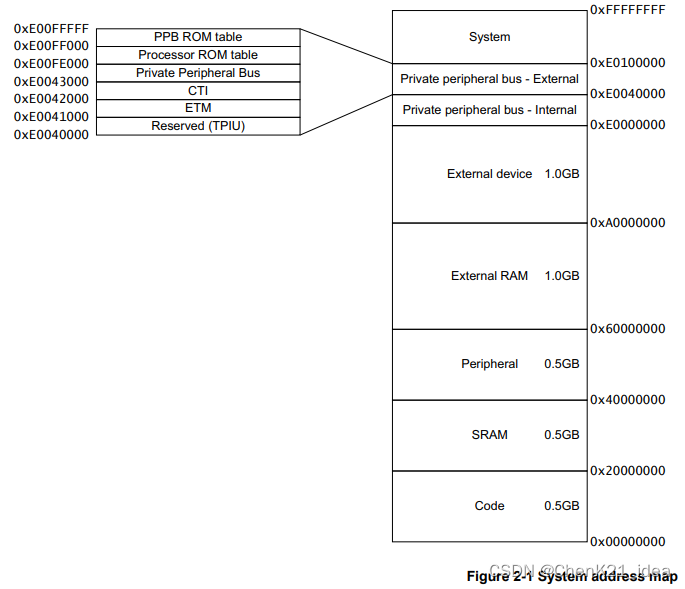

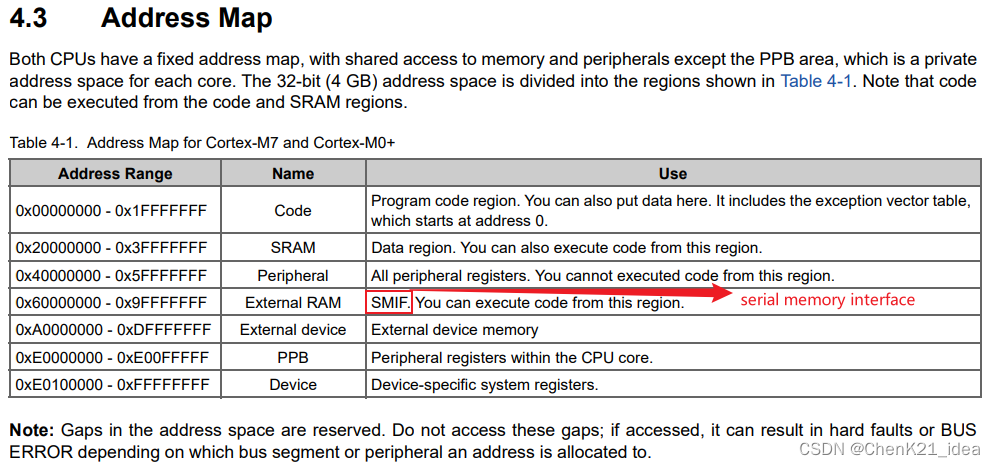

6.4 System address map

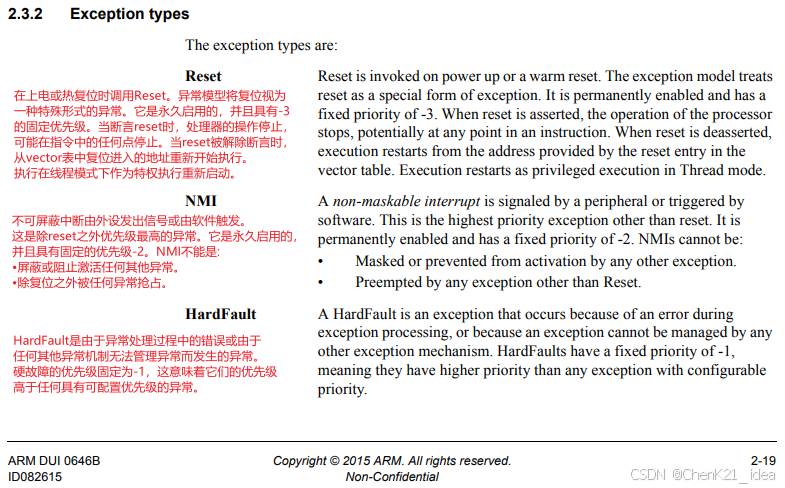

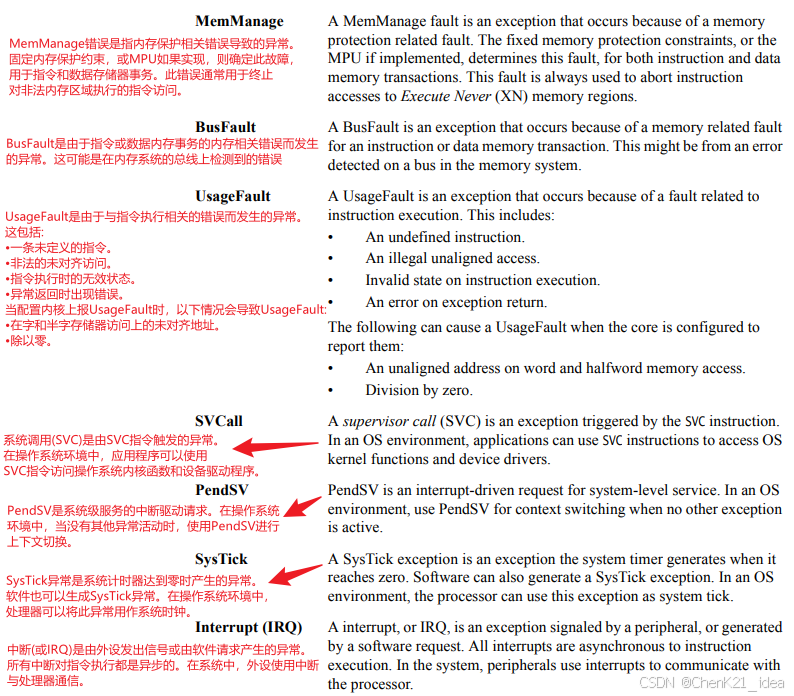

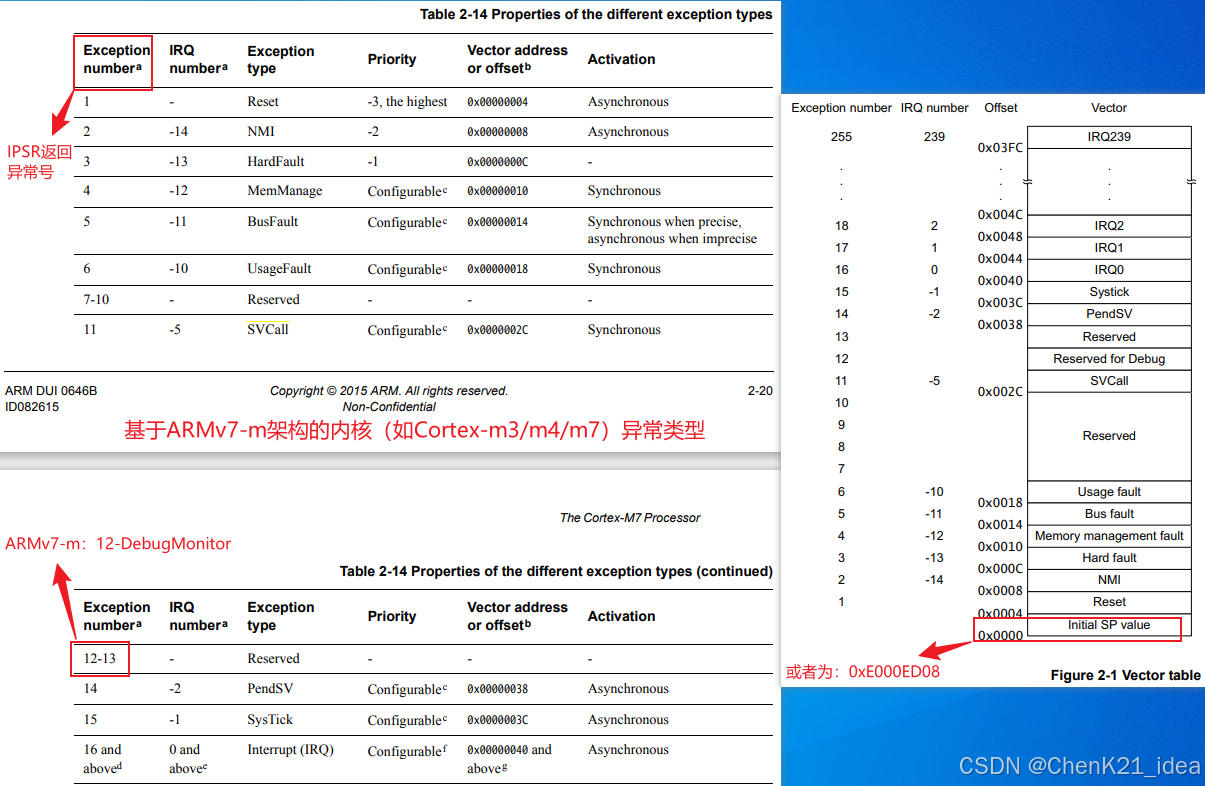

【7】Cortex-M7 System Exception

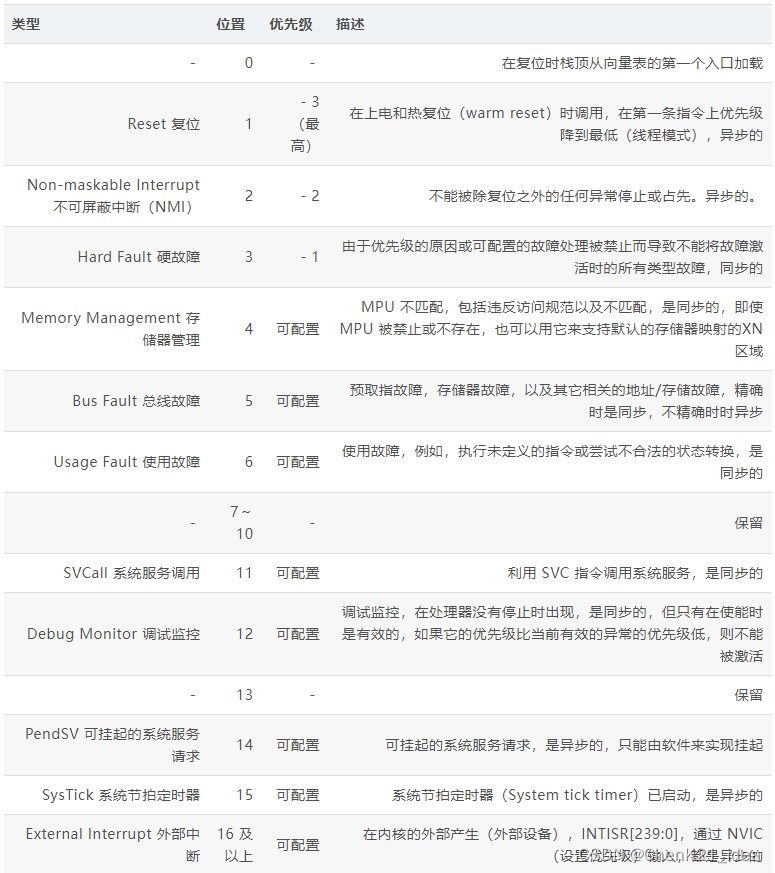

7.1 Cortex-M7处理器一共有255个异常,异常编号(Exception number)为1 ~ 255,其中1 ~ 15属于内核异常,大于15属于外设中断,-14 ~ -1为内核中断(异常)请求编号,大于-1为外设中断请求编号(IRQ number)。

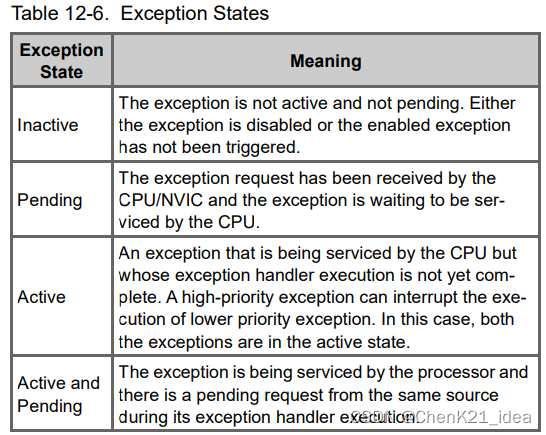

7.2 异常是指打断程序正常执行流的事件。其分为非活跃且非挂起状态,挂起状态,活跃状态,活跃且挂起状态。中断属于异常的子集,异常与中断都是硬件支持的。

7.3 中断控制器属于CPU外设之一,一方面接收其他外设中断信号的输入,另一方面,发出中断信号给CPU,因此通过对中断控制器NVIC编程实现对中断源的优先级、触发方式、打开以及关闭源等设置操作。ARMv7-M NVIC架构支持496个中断,所支持的外部中断可以通过只读寄存器ICTR(0xE000E004)获取。

7.4 NVIC属于Cortex内核器件,不可屏蔽中断NMI和外部中断都由它处理,但SYSTICK不是由NVIC来控制的,它有自己的中断控制寄存器,不是通过NVIC使能。1 ~ 15异常也不是由NVIC来控制的,通过SCB寄存器控制。

7.5 中断延迟指硬件产生中断,到系统进入中断服务子程序ISR并执行第一条指令的时间。

7.6 对于多核CPU中的每个CPU而言,中断控制器逻辑是独立的。

7.7 对于英飞凌TRAVEO™ T2G,低优先级数字代表高优先级。Reset,NMI,HardFault异常均拥有一个固定的优先级(依次为-3,-2,-1),并且该优先级最高。其他异常可以被配置为0-7之间的优先级(Cortex-M7)。

7.8 当CPU收到两个及以上的相同优先级的异常请求时,优先处理异常编号最低的异常。

7.9 即使中断被屏蔽,其挂起请求状态仍可置位,该情况下,如果中断稍后被使能,就可以被触发并得到处理,所以一般要求使能NVIC中断前手动清除挂起状态。

中断挂起是等待执行不是舍去,当高优先级或先发生同等级中断执行完成后,再去执行。(ISPR置1,①对已挂起的中断没有影响;②对被禁用的中断,设置其状态为挂起)

7.10 一个中断源发生中断请求时,中断控制单元首先判断当前是否有中断,它是否比当前服务的中断优先级高,是否有多个待执行的中断:

如果当前没有正在服务的中断,判断是否有其他待处理的高优先级中断。如果没有,执行;否则,挂起,先执行高优先级中断。

如果当前有正在服务的中断,判断新中断是否有更高优先级。如果是,打断上一个中断,启动新中断;否则,挂起。

在一个中断服务完成时,中断控制单元清除该中断标志(如果是这样设计的),判断是否有挂起的中断,选择优先级最高的执行。 实际上,中断控制单元就是在对所有中断源的中断请求信号进行判断和处理。一个中断请求,实际上就是一路信号有效(比如置位 高电平);所谓挂起,可以理解为暂时不理睬它。

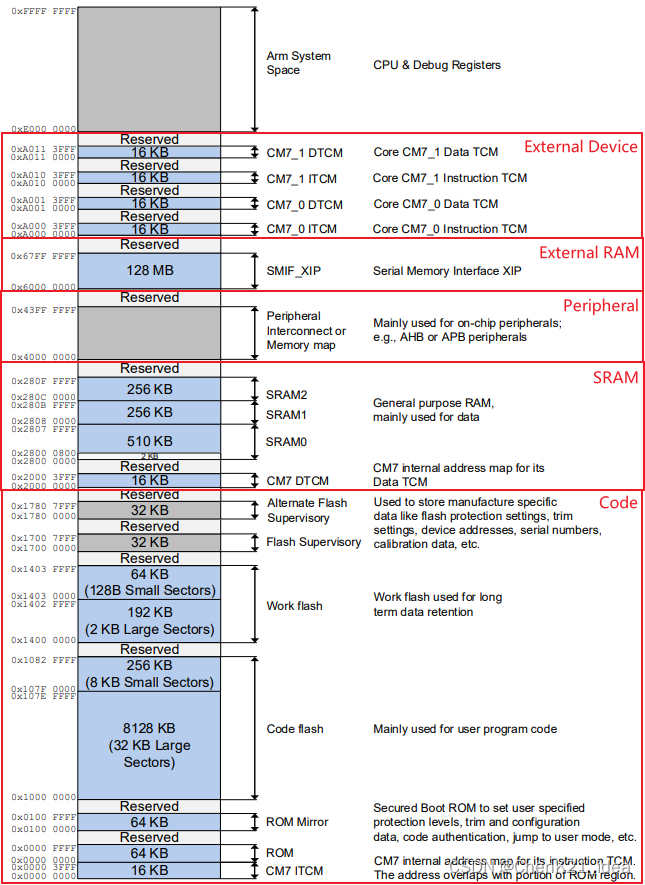

【8】Memory Mapping

8.1 存储器映射(Memory Mapping):存储器映射是对各种存储器的大小和地址分布的规划。存储器映射是为了快速响应中断或者快速完成某个任务,将同一地址段映射到不同速度的两个存储块,然后将低速存储块中的代码段复制到高速存储块中,对低速存储块的访问将被重映射为对高速存储块的访问。

或理解为 输入是地址总线上的地址编码,输出是被寻址单元中(或数据总线)的数据。该函数是一个逻辑概念,计算机系统上电复位后才建立起这种映射,当计算机掉电后,这个函数就不复存在,只剩下计算机系统中实现这个函数的物理基础——电路连接。

8.2 存储器映射是在复位之前由CPU自动完成的,存储器重映射是在复位之后由系统程序完成的。通常的顺序是:上电->存储器映射->复位->存储器重映射->系统初始化->启动OS。

8.3 同一类型的存储器称为一个存储块(Memory Block)或者存储区域(Memory Area, Memory Region)。

8.4 目前很多嵌入式系统中的Flash分为Code Flash和Data Flash。Code Flash存放可以运行的程序代码,Data Flash存放应用数据。Code Flash通常被映射到0地址,系统上电复位后就从0地址开始执行。通常中断向量表就位于0地址的起始位置,系统上电复位后执行的第一条指令就是复位中断的跳转指令。

由于中断向量表位于Code Flash中,Code Flash的读取速度比RAM慢,为了快速响应中断,就将RAM重映射到0地址,然后将中断向量表复制到RAM的起始位置。再发生中断时,访问Code Flash中的中断向量表,将被重映射为访问RAM中的中断向量表。

8.5 CYT4BF address map

【杂记】

- 用户需要进行特权级操作用以访问硬件或修改寄存器的值,因此调用系统服务函数,进入异常处理函数中,从而获得特权级权限,更改相关寄存器的数值。

- 系统管理任务的数据结构称为任务控制块(TCB)。

- 在双栈模式下(主堆栈指针MSP和进程堆栈指针PSP),进入异常时的自动压栈使用的是进程栈PSP,进入异常后会自动改为MSP,退出异常时切换回PSP,并从PSP上弹出数据。

- 操作系统的入口是中断。Cortex-M系列中Systick是OS的心跳时钟,是调度器的核心。系统在Systick中进行上下文切换。

- 内核中断管理:中断一般由硬件引起,是微处理器外部发送,通过中断通道送入处理器内部;而异常通常是微处理器内部发生的,大多是由软件引起的,比如特权调用异常,除法出错异常等。

861

861

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?