用verilog做一个可以将整数的每一个位分离的模块

比如一个两位数分成个位和十位

我用了两种方法

1.除法取余

assign q=shuzi/1000;

assign b=shuzi/100%10;

assign s=shuzi/10%10;

assign g=shuzi%10;

2.除法减法乘法

assign q=shuzi/1000;

assign b=shuzi/100-q*10;

assign s=shuzi/10-q*100-b*10;

assign g=shuzi-q*1000-b*100-s*10;

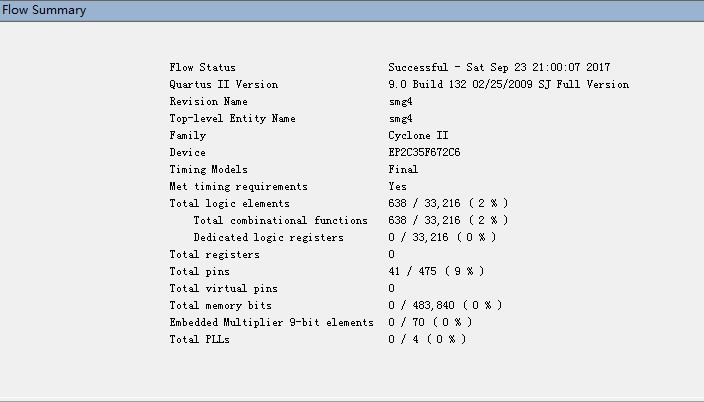

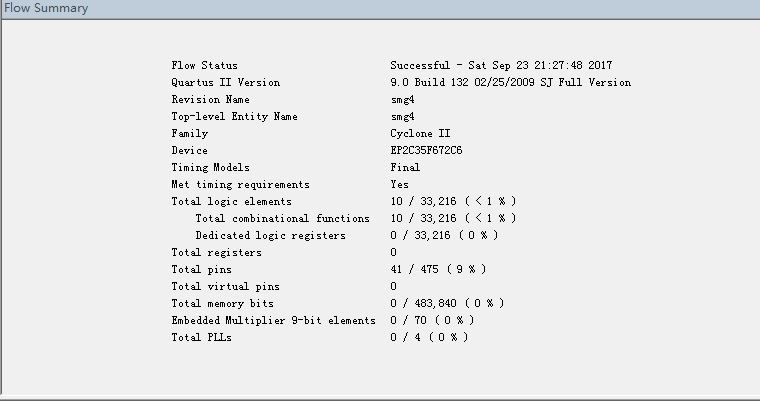

整个工程综合出来发现取余会占用很多资源 把除法去掉(但是没有实现位分离的功能)

除法和取余真的很占资源

感觉还是用一个算法比较好 二进制转换成BCD码 加三移位法

本文介绍使用Verilog实现整数位分离的方法,包括除法取余及除法减法乘法两种方式,并讨论了资源占用问题。

本文介绍使用Verilog实现整数位分离的方法,包括除法取余及除法减法乘法两种方式,并讨论了资源占用问题。

1470

1470

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?