1、EDA

即电子设计自动化,以大规模可编程逻辑器件为设计载体,以硬件描述语言HDL为系统逻辑描述的主要表达方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具,自动地完成用软件方式描述的电子系统到硬件系统的逻辑编译、化简、分割、综合、布局布线以及逻辑优化和仿真测试,直至实现既定的电子线路系统功能。

2、EDA技术应用对象

超大规模可编程逻辑器件、半定制或全定制ASIC、混合ASIC。

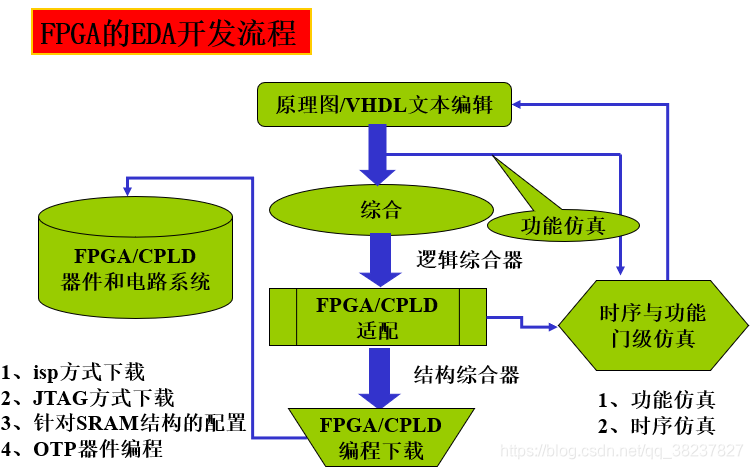

3、开发流程

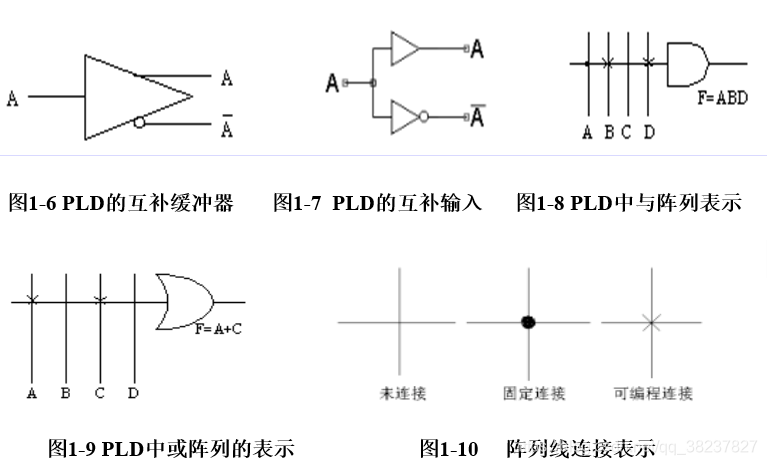

4、常用的描述PLD内部结构的专用电路符号

5、宏单元

(1)由三个功能块组成

◆逻辑阵列 : 实现组合逻辑,提供5个乘积项。

◆乘积项选择矩阵 : (1)分配乘积项作为到“或”门和“异或”门的主要逻辑输入,实现组合逻辑函数。(2)把乘积项作为宏单元中寄存器的辅助输入。

◆可编程寄存器 :可被单独设置成带可编程时钟控制的D、T、RS、JK触发器工作方式。也可将寄存器旁路掉,实现组合功能。

(2)每个寄存器可按3种时钟输入模式工作:

◆全局时钟信号。全局时钟输入直接连向每个寄存器的CLK端,能实现最快时钟到输出功能。

◆全局时钟信号由高电平有效的时钟信号使能 。输出速度较快。

◆用乘积项实现一个阵列时钟。由于时钟来自宏单元,其速度稍慢。

(3)每个寄存器也支持异步清零和异步置位功能。

6、扩展乘积项

复杂的逻辑函数需要附加乘积项,可利用其他宏单元以提供逻辑资源,称为扩展乘积项(共享和并联)

7、I/O控制块

★允许每个I/O引脚单独配置为:输入、输出和双向工作方式。

★所有I/O引脚都有一个三态缓冲器,控制信号来自多路选择器,可以选择用信号、GND和VCC控制。

★三态缓冲器控制端接地:I/O引脚为专门输入引脚。三态缓冲器控制端接VCC:I/O引脚为普通输出引脚。

8、CycloneⅢ系列器件的结构原理

Cyclone系列器件,即Cyclone、CycloneⅡ、CycloneⅢ,是Altera公司高性价比的产品,是典型的FPGA器件。CycloneⅢ主要由五部分组成,包括逻辑阵列块(LAB)、嵌入式存储器块、嵌入式硬件乘法器、I/O单元和嵌入式PLL。其中逻辑阵列块(LAB)由多个逻辑宏单元(LE)组成。

3098

3098

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?