题目描述

求两个数之间的最大公约数。

第一次编码

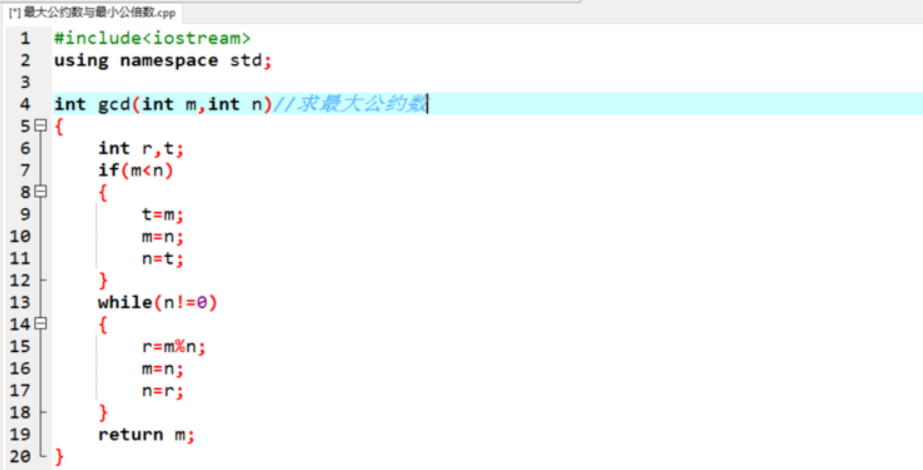

求最大公约数的算法是简单的,直接用辗转相除法,它的基本算法来自于下面这段c代码:

下面展示了第一次写出的代码,这段代码有一个致命缺陷。

module find_gcd

(

input [7 : 0] data_a,

input [7 : 0] data_b,

input clk,

input rst_n,

output reg gcd_valid,

output reg [7 : 0] gcd,

//------------<temporary output>-----------------

output current_state,

output buffer_a,

output buffer_b

);

localparam IDLE = 2'b00,

COMP = 2'b01,

CALC = 2'b10,

RESU = 2'b11;

reg [7 : 0] r, t,

buffer_a, buffer_b;

reg [1 : 0] current_state, next_state;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

current_state <= IDLE;

else

current_state <= next_state;

end

always@(*)

begin

case(current_state)

IDLE: begin

gcd_valid = 0;

gcd = 0;

buffer_a

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6441

6441

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?