一、DS18B20

DS18B20 是 Dallas Semiconductor(现为 Maxim Integrated)生产的一款数字温度传感器。它的核心特点如下:

-

数字输出:直接输出数字温度值,无需外部ADC,抗干扰能力强。

-

单总线接口:仅需一根数据线(加上电源和地)即可与微控制器通信,极大地节省了微控制器的I/O口。

-

高精度:典型精度为 ±0.5°C(在 -10°C 至 +85°C 范围内)。

-

宽电压范围:3.0V 至 5.5V。

-

测温范围:-55°C 至 +125°C。

-

可编程分辨率:用户可配置 9 至 12 位的分辨率,分辨率越高,转换时间越长。

-

独特64位序列号:每个DS18B20都有一个独一无二的激光ROM编码,允许在一条总线上挂载多个器件,并通过地址进行区分。

-

供电灵活:支持标准外部供电和“寄生电源”模式

二、单总线通讯协议(One-Wire)

定义:主机和从机通过1根线进行通信,在一条总线上可挂接的从器件数量几乎不受限制。

特点:这是由达拉斯半导体公司推出的一项通信技术。它采用单根信号线,既可传输时钟,又能传输数据,而且数据传输是双向的。

优点:单总线技术具有线路简单,硬件开销少,成本低廉,便于总线扩展和维护等。

三、通讯过程

(1) 初始化

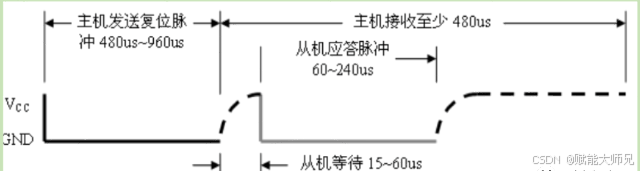

基于单总线上的所有传输过程都是以初始化开始的,初始化过程由主机发出的复位脉冲和从机响应的应答脉冲组成。应答脉冲使主机知道,总线上有从机设备,且准备就绪。黑色实线代表系统主机拉低总线,灰色实线代表从机拉低总线,而黑色的虚线则代表上拉电阻将总线拉高。

初始化代码:

static void DS18B20_Rst(void) {

DS_GPIO_Set_OUT_Mode();

DS_PIN_CLR();

/* 主机至少产生480us的低电平复位信号 */

Delay_us(750);

/* 主机在产生复位信号后,需将总线拉高 */

DS_PIN_SET();

/*从机接收到主机的复位信号后,会在15~60us后给主机发一个存在脉冲*/

Delay_us(15);

}

初始化后监测从机发送的存在脉冲,判断当前是否存在单总线设备,示例以DS18B20为例:

static uint8_t DS18B20_Presence(void) {

uint8_t pulse_time = 0;

DS_GPIO_Set_IN_Mode();

while( DS_PIN_READ() && pulse_time < 100 ) {

pulse_time++;

Delay_us(1);

}

if( pulse_time >=100 )

return 1; else pulse_time = 0;

while( !DS_PIN_READ() && pulse_time < 240 ) {

pulse_time++;

Delay_us(1);

}

if( pulse_time >=240 ) return 1; else return 0;

}

static uint8_t DS18B20_Presence(void) {

uint8_t pulse_time = 0;

/* 主机设置为输入 */

DS_GPIO_Set_IN_Mode();

while( DS_PIN_READ() && pulse_time < 100 ) {

pulse_time++;

Delay_us(1);

}

/* 经过100us后,存在脉冲都还没有到来*/

if( pulse_time >=100 ) return 1; else pulse_time = 0;

/* 存在脉冲到来,且存在的时间不能超过240us */

while( !DS_PIN_READ() && pulse_time < 240 ) {

pulse_time++;

Delay_us(1);

}

if( pulse_time >=240 ) return 1; else return 0;

}

(2) 写时序

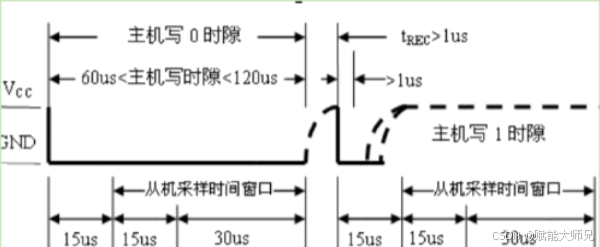

存在两种写时隙:"写1" 和"写0"。主机采用写 1 时隙向从机写入 1,而采用写 0 时隙向从机写入 0。所有写时隙至少需要 60 us,且在两次独立的写时隙之间至少需要 1u s 的恢复时间。两种写时隙均起始于主机拉低总线(图5 所示)。产生写 1 时隙的方式:主机在拉低总线后,接着必须在 15u s 之内释放总线,由5k 上拉电阻将总线拉至高电平;而产生写0 时隙的方式:在主机拉低总线后,只需在整个时隙期间保持低电平即可( 至少60 us)。在写时隙起始后 15-60 us 期间,单总线器件采样总线电平状态。如果在此期间采样为高电平,则逻辑1 被写入该器件;如果为0 ,则写入逻辑0。时序图代码如下:

/*DS18B20写bit函数*/

static void DS_Write_Bit(ds_pin_level level) {

if(level == HIGH) //写一 {

DS_PIN_CLR();

Delay_us(5);

DS_PIN_SET();

//释放总线

Delay_us(50);

} else //写0 {

DS_PIN_CLR();

Delay_us(60);

DS_PIN_SET(); //释放总线

Delay_us(2); //协议时间要求:1 < t < 无穷大,此处时间为10us

}

}

/*DS18B20写一个字节函数*/

static void DS_Write_Byte(uint8_t byte) {

uint8_t i = 0;

DS_GPIO_Set_OUT_Mode();

//配置为输出模式

for (i = 0; i < 8; i++) {

if(byte & 0x01) //先发送低位低 {

DS_Write_Bit(HIGH);

} else {

DS_Write_Bit(LOW);

}

byte >>= 1;

Delay_us(2);

}

}

(3) 读时序

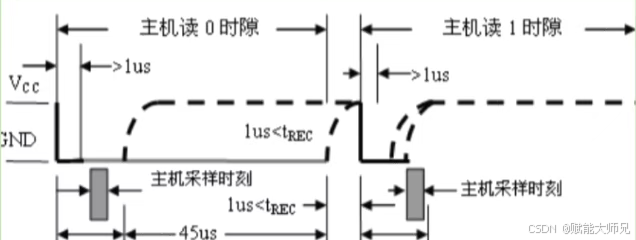

单总线器件仅在主机发出读时隙时,才向主机传输数, 所以, 在主机发出读数据命令后,必须马上产生读时隙,以便从机能够传输数据。所有读时隙至少需要 60us, 且在两次独立的读时隙之间至少需要 1us的恢复时间,每个读时隙都由主机发起,至少拉低总线 1us (图5 所示)。在主机发起读时隙之后,单总线器件才开始在总线上发送 0 或1。若从机发送1,则保持总线为高电平;若发送 0, 则拉低总线 。当发送 0 时,从机在该时隙结束后释放总线 。由上拉电阻将总线拉回至空闲高电平状态。从机发出的数据在起始时隙之后,保持有效时间 15us ,因而,主机在读时隙期间必须释放总线 ,并且在时隙起始后的 15 us 之内采样总线状态。时序图代码如下:

/*DS18B20读bit函数*/

static ds_pin_level DS_Read_Bit(void) {

ds_pin_level temp;

DS_GPIO_Set_OUT_Mode();

DS_PIN_CLR();

Delay_us(10);

//协议时间要求:1 < t < 无穷大,此处时间为5us

DS_GPIO_Set_IN_Mode();

//配置DS18B20数据脚为输入模式

if(DS_PIN_READ() == GPIO_PIN_SET) //读 1 {

temp = HIGH;

} else //读0 {

temp = LOW;

}

Delay_us(45);

//协议时间要求为45us

return temp;

}

static uint8_t DS18B20_Read_Byte(void) {

uint8_t i = 0;

uint8_t level = 0;

uint8_t dat = 0;

for (i = 0; i < 8; i++) {

level = DS_Read_Bit();

dat = (dat) | (level << i);

}

return dat;

}

(4) 搜索ROM

ROM搜索过程只是一个简单的三步循环程序:读一位、读该位的补码 、写入一个期望的数据位。总线主机在 ROM的每一位上都重复这样的三步循环程序。当完成某个器件后,主机就能够知晓该器件的ROM信息。剩下的设备数量及其 ROM代码通过相同的过即可获得。

下面的ROM搜索过程实例假设四个不同的器件被连接至同一条总线上,它们的 ROM代码如下所示:

ROM1 00110101…

ROM2 10101010…

ROM3 11110101…

ROM4 00010001…

具体搜索过程如下:

a: 主机发出复位脉冲,启动初始化序列。从机设备发出响应的应答脉冲;

b: 接着主机在总线上发出ROM搜索命令 ;

c: 主机从总线上准备读入一个数据位,这时,每个响应设备分别将 ROM代码的第一位输出到单总线上。ROM1 和ROM4 输出 0 至总线,而ROM2 和ROM3 输出 1 至总线。线上的输出结果将是所有器件的逻辑”与“ ,所以,主机从总线上读到的将是0 。接着, 主机开始读另一位,即每个器件分别输出 ROM代码中第一位的补码,此时,ROM1 ROM4 输出 1至总线,而ROM2和ROM3 输出 0 至总线 。这样,主机读到的该位补码还是 0 。主机由此判定,总线上有些器件的ROM代码第一位为0, 有些则为1。

1272

1272

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?