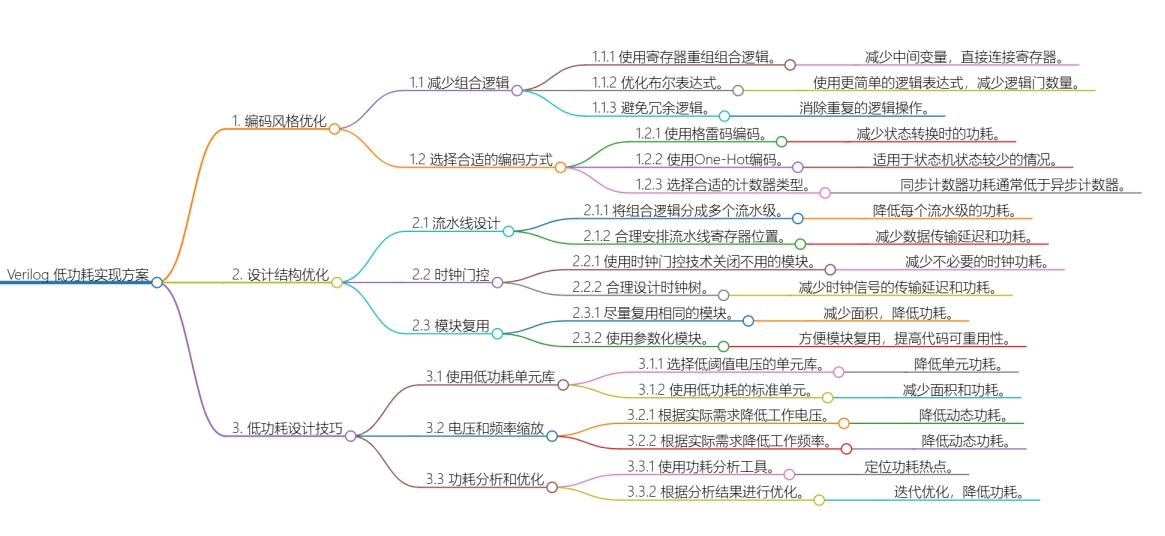

以下为Verilog低功耗设计的核心实现方案及典型代码示例,结合RTL级优化策略与系统级设计思路。

一、动态功耗优化方案

1、门控时钟技术原理

(1)功耗构成与影响

动态功耗:占芯片总功耗40%-60%,主要由时钟网络和寄存器翻转产生,公式为

,其中α为活动因子,C为负载电容。

静态功耗:由漏电流引起,与工艺制程强相关,门控时钟主要通过降低动态功耗实现优化。

(2)门控时钟核心机制

基本原理:通过逻辑门控制时钟信号的通断,关闭空闲模块的时钟树翻转,消除无意义寄存器操作。

典型结构:

// 带锁存器的安全门控时钟实现

always @(clk or clk_en) begin

if (~clk) clk_gated = clk & clk_en_latch; // 低电平锁存使能信号

end

通过锁存器确保使能信号仅在时钟低电平切换,避免毛刺

(3)门控时钟实现方案

RTL级实现策略

基本门控单元:

modu

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?