文章目录

概要

Verilog 是一种硬件描述语言(HDL),用于设计、模拟和实现数字电路。它对硬件设计者提出了高效、准确的编码要求。以下是 Verilog 编码实现中的关键技巧和注意事项,涵盖代码优化、低功耗设计、模块化编程和调试技巧等方面,并附有示例来说明。

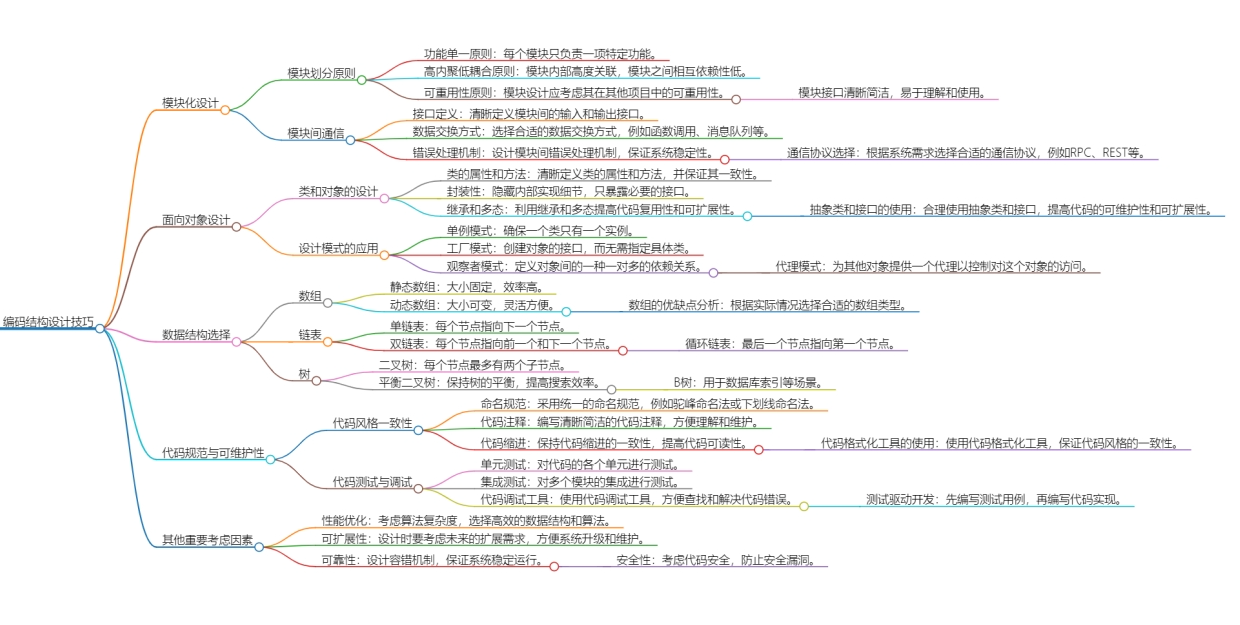

一、编码结构设计技巧

1、层次化设计

- 将设计分解为多个子模块,每个模块完成特定功能。

- 使用模块参数化提高复用性。

示例:层次化设计

// 子模块:加法器

module adder (

input wire [3:0] a,

input wire [3:0] b,

output wire [3:0] sum,

output wire carry_out

);

assign {carry_out, sum} = a + b;

endmodule

// 顶层模块

module top_module (

input wire [3:0] a,

input wire [3:0] b,

output wire [3:0] sum,

output wire carry_out

);

adder u1 (

.a(a),

.b(b),

.sum(sum),

.carry_out(carry_out)

);

endmodule2、参数化设计

通过参数定义模块的宽度和功能,增强模块的灵活性。

示例:可参数化的计数器

module param_counter #(

parameter WIDTH = 8 // 参数定义计数器位宽

)(

input wire clk,

input wire rst_n,

input w

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1008

1008

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?