作者及发刊详情

@ARTICLE{10500752,

author={Perotti, Matteo and Cavalcante, Matheus and Andri, Renzo and Cavigelli, Lukas and Benini, Luca},

journal={IEEE Transactions on Computers},

title={Ara2: Exploring Single- and Multi-Core Vector Processing With an Efficient RVV 1.0 Compliant Open-Source Processor},

year={2024},

volume={73},

number={7},

pages={1822-1836},

keywords={Vectors;Registers;Computer architecture;Vector processors;Multicore processing;Microarchitecture;Kernel;RISC-V;vector;ISA;RVV;processor;efficiency;multi-core},

doi={10.1109/TC.2024.3388896}}

摘要

正文

主要贡献

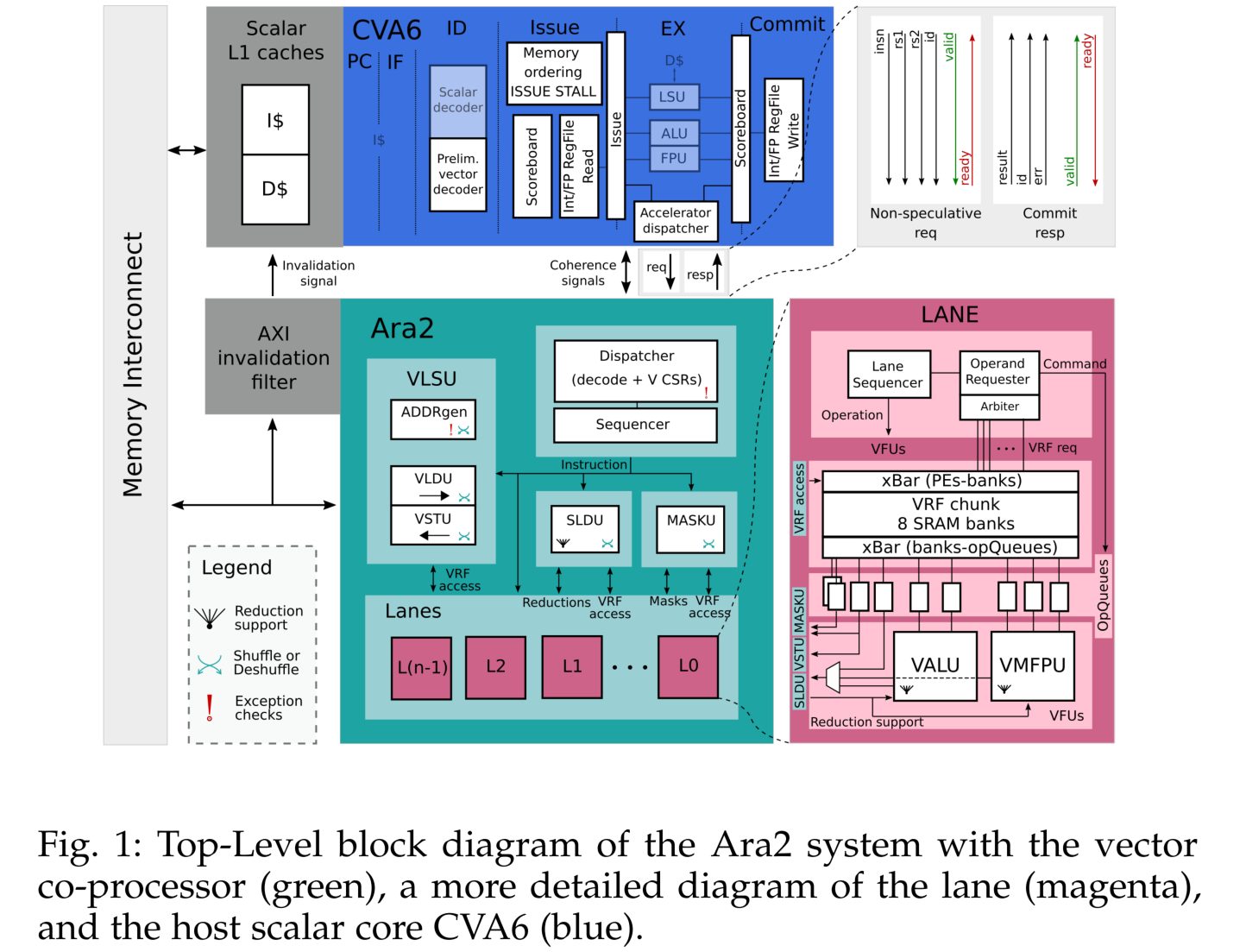

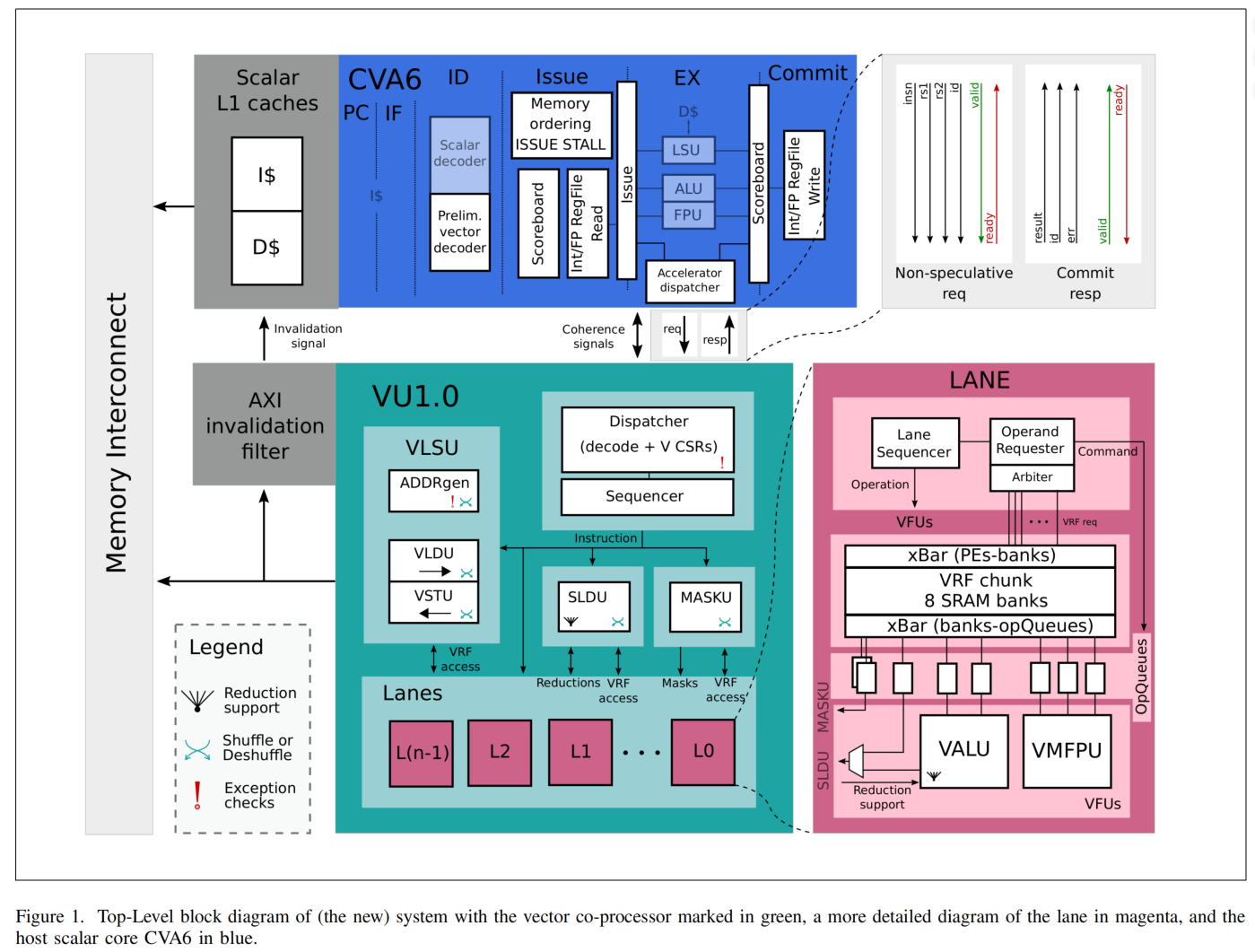

介绍了当前一款支持RVV1.0的开源处理器Ara2的设计及其微架构

讨论了RVV指令集手册的变化,及其对系统微架构的影响

根据不同应用领域的benchmark测试需要大的向量长度深入分析了性能

根据最关键路径SLDU的微架构优化对向量架构可扩展性的影响,在22nm的FD-SOI的工艺下实现了2到16lane的PPA分析

在不同的硬件配置上进行了性能/效率的权衡研究,证明了一个多核向量架构如何缓解标量core的发射(issue)率限制的问题

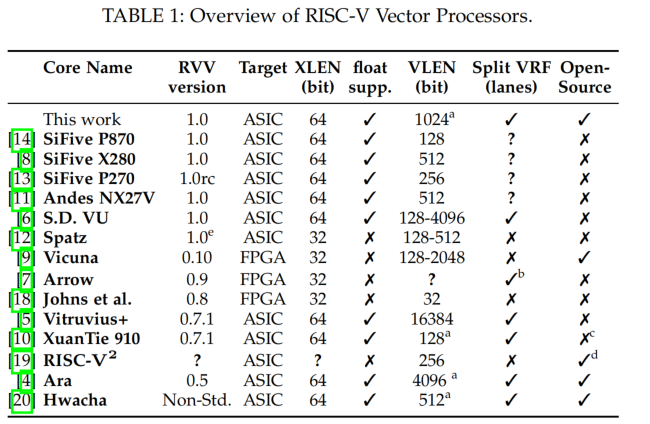

Related works

硬件架构

SLDU

Slide Unit,重排序单元

参考文献

评

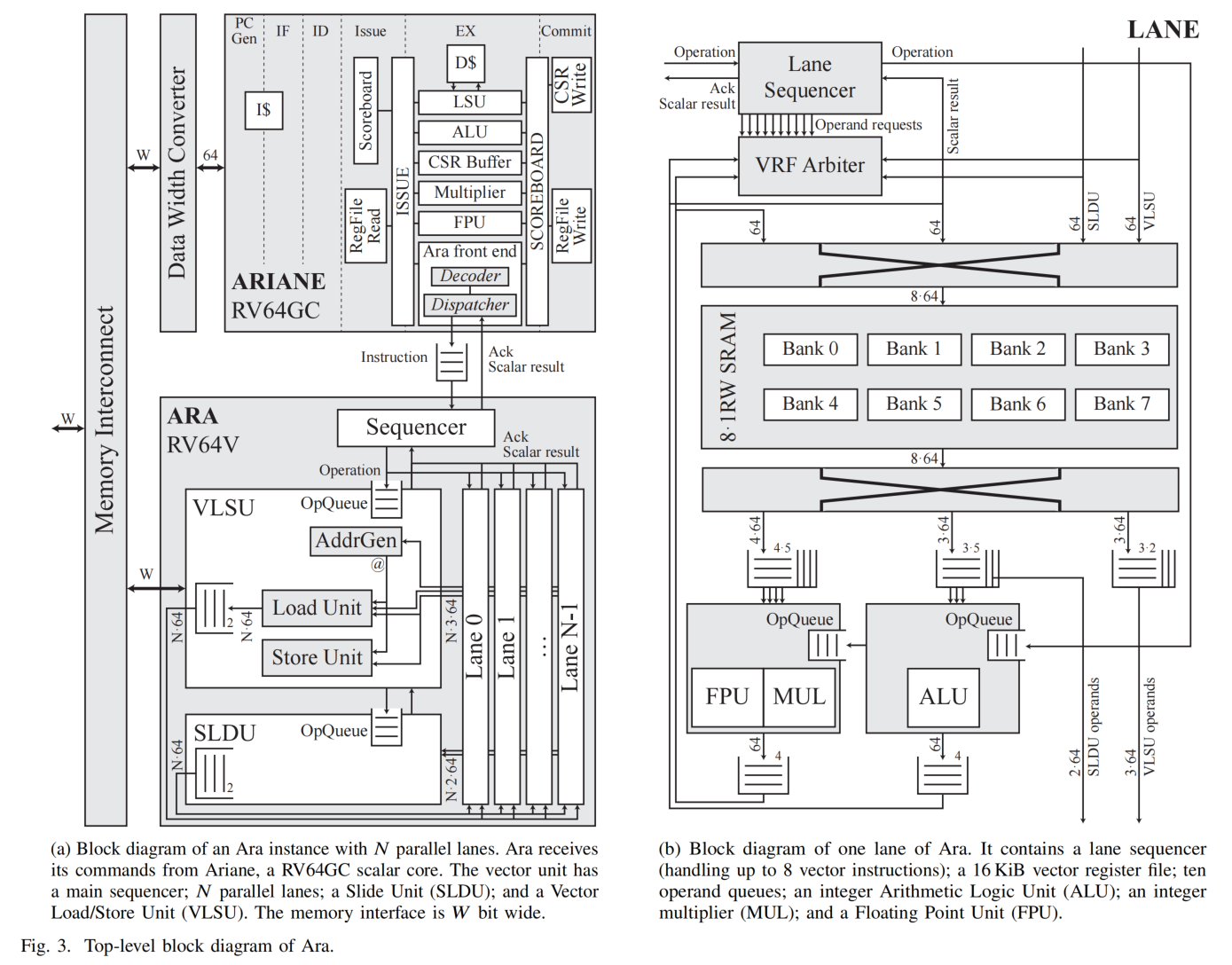

架构

历经多次迭代,以论文发表为节点分为:

2019年支持rvv0.5

Ara: A 1 GHz+ Scalable and Energy-Efficient RISC-V Vector Processor with Multi-Precision Floating Point Support in 22 nm FD-SOI

2022年支持rvv1.0

A ‘‘New Ara’’ for Vector Computing: An Open Source Highly Efficient RISC-V V 1.0 Vector Processor Design

支持rvv1.0的大部分指令,除了: fixed-point arithmetic, floating-point reductions 以及较为特殊的指令 (包括round towards odd, reciprocal, square root reciprocal), segment memory operations (non-mandatory since RVV 1.0), gather, compress, scalar moves 以及一些特殊的 mask instructions

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?