仿真得到的region含义

0 截止区

1 线性区(三极管区)

2 饱和区

3 亚阈值区

4 break down

1.Vgs为3.3,扫描Vd

MOS管的源端和漏端分别接Vg和Vd,可设置Vg为3.3V,Vd为变量,设置变量Vd值为3.3V,dc仿真并对design variable ——Vd进行扫描,扫描范围选择0-3.3V,扫描方式选择线性,【automatic方式不准确,尽量避免使用】,step size可选择0.01,这样仿真设置就完成了。

接下来设置仿真完成后的输出,ADE→output→to be saved→select OP Parameters,在电路图中选择需要观测的MOS管,然后ADE的右下角会出现Save Operating Points窗口,选择输出OP参数有两种方式,

1.在Operating Parameters下边的框中输入vds vdsat vgs vth vgt region【仿真结果证明vgt=vgs-vth,所以也可以只输入vgt而省略vgs和vth啦】,中间用空格隔开,都是小写字母,【发现了遇到过的cadence中隔开两个变量的都是空格,比如给线打label时也是用空格隔开】

2.也可以点Operating Parameters下边的框的三个点点···,点击get information,选择需要输出的参数即可。

输出OP参数选择完成之后,选上Plot,使其仿真完成后自动plot。

然后选择Outputs→to be plotted→select on design,选择Vd。这样输出也设置好了,

下面开始仿真吧!

仿真完成,得到关于直流工作点的图啦!

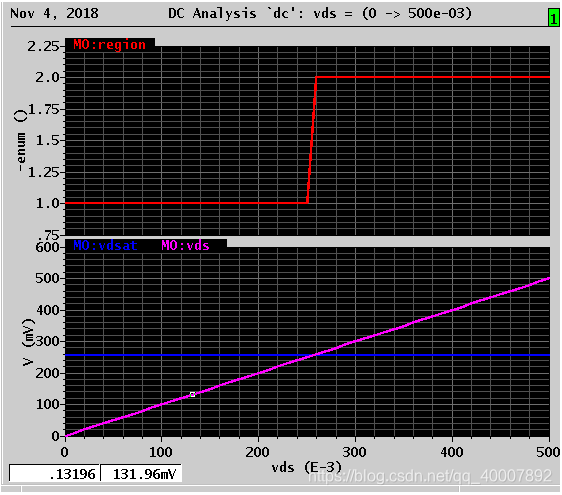

tsmc.18工艺中,最小尺寸的NMOS,vd>vdsat时,region由1变为2。(Vgs=3.3V)

为了保证PVT下,管子处于饱和区,vd需要比vdsat大某个经验值。

vov=vgs-vth=vgt,从plot得到的图中可以看到在vds达到vgt之前,就已经进入了饱和区(region=2),这是由于短沟道器件中的速度饱和效应导致的。

贴张eetopregion判别MOS管工作区;以及vdsat、vds、vgs-vth之间的关系 - Analog/RF IC 设计讨论 - EETOP 创芯网论坛 (原名:电子顶级开发网) -上的图

2.Vd为3.3,扫描Vgs

除了扫描变量设置不同,vd=3.3V,对vg进行扫描,其他就和上述步骤一样~\(≧▽≦)/~

然后发现对于tsmc.18,nmos3v_mac最小尺寸W=2u,L=350n的管子,随着Vg的增加,vgt也以同样斜率增加,NMOS依次进入截止区、亚阈值区、饱和区,当-261mV<vgt<0V时,NMOS处于亚阈值区,当vgt>0时,进入饱和区。

为了实现低功耗,通常使放大器输入对管工作在亚阈值区,可以在使vgt在上述亚阈值范围内取值。

也可以在OP参数里加上id,看看MOS管工作在亚阈值区和截止区的电流情况,可以发现,随着vgt的增加,id一直是增加的趋势,在截止区和亚阈值区增加较缓,在饱和区增加较快:

在截止区内在随着vgt增加,id从46.88f增加到31.85n,在亚阈值区,id增加到约5u,在饱和区,当vg为3.3V时,id增加到最大,约1.15m。

当尺寸变大时,电流也会随之变大。

2162

2162

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?