m1 drawing上覆盖m1 pin,label打在m1 pin上(tsmc.18)或打在m1 text上(gsmc.55)

按e,修改snap spacing为0.005【查看版图设计规则,搜索grid,找到design geometry restriction】并save to cellview或tech library,右下角有Dimming,使非选中区域动态变暗。左上角有Nets,飞线

金属及poly线宽能够承受的电流,【查看版图设计规则,搜索mA/um,找到Electromigration Rule】

p,然后按F3,选择线宽

shift p画多边形

r画矩形

s拉伸

o添加过孔。mode选择stack可以直接创建多层通孔

l 添加标签

ctrl + D –> 取消选择,用鼠标点击空白区域也可实现

F2 –> 保存

F3 –> 打开基础操作的扩展选项,标尺下F3可以调整标尺的大小

画线(自动分线)

<key>P leHiCreateWire()→画线时右键→auto Tap wire

自动打孔

按O→Auto→Min Number of Cuts:2→Hide

Net飞线关系

Connectivity→Nets→Show/Hide All Incomplete Nets

加线名

Connectivity→Nets→Assign→F3

Shift+O旋转

tab –> 以点击位置为画面中心

g –> 切换鼠标是否自动吸附近元素(层次不多的时候比较方便,复杂的时候反而有副作用),gravity引力,options-Editor-Gravity controls可以开关引力吸附、和距离,是否为只选中的对象。

Shift + g 或create MPP–> 添加 Guard Ring

Multipart Path——用于画guard ring或衬底

| 设置能在进入下一个图层的时候直接显示所有layer,按e 找到display levels ,start 0 stop 31 |

x –> 在当前界面编辑所选定的layout子模块(左键双击也可以实现该功能)

Shift + x –> 以新的界面编辑所选定的layout子模块

Shift + b –> 返回上一层的layout

IC61自动打孔

按O→Auto→Min Number of Cuts:2→Hide

IC61画线(自动分线)

<key>P leHiCreateWire()→画线时右键→auto Tap wire

取消Calibre高亮

Calibre→Clear Highlights

金属走线画斜线,按p,再按F3,snap mode选择diagonal,画完线之后选中画好的线,按 shift M,可以合并图层;第二种方法,shift p,然后按n

画path时可以从一层切换到另一层,并且自动打上对应的接触孔,这个功能叫path stitching,操作是按p画线之后,鼠标右键选择切换到哪一层。

Ctrl+y: 当多个图形叠在一起时(点击左键默认是两个图形间切换),可以轮流选择重叠的图形。

定义链接关系,connectivity-define device correspondence,使得schematic线路和版图layout中的器件对应起来。,

更改版图的参考线路schematic,connectivity-update-connectivity reference

根据原理图连接关系显示版图中未连接的飞线,connectivity-incomplete nets

shift M 合并重叠的单元层

shift C 切割选择的单元层

Floorplan-reinitialize floorplan 设置边界,且可以在版图画好之后重新设置边界(在initialize options中进行选择)

Tools-->Technology File Manager-->Attach更换库的参考model

DRD Notify on打开版图设计规则提示

DRD enforce on强制性版图规则提示,比如不能将两根相同的m1放置在间距小于版图规则的距离之内。按1可以暂时取消这个强制性规则,两根m1的间距可以小于最小间距,再按1恢复。

使用MPP制作guard ring具体操作见下面网页

schematic中的off grids问题,edit-snap-snap to grids,缺点是可能使得连线断开,需要手动连一下。

layout中的offgrid的问题

法1:如果有grid off。首先建立一个新的库,用于放stram后的文件。最终的原始版图文件在启动窗口export-> stream out它的gds文件并保存到一个位置。然后,启动窗口import-> stream in,show Options-> Geometry 点击Snap to Grid 并选择那个gds文件到新的库中。(注意:一定要建新的库,不然会把原始电路覆盖)。导入后的电路图里的文件仅仅包含Layout文件,需要从原来的库中copy过来。打开layout DRC LVS会有错误,因为金属会有位移,拉伸等等问题,修改以后就行了。https://bbs.eetop.cn/thread-765183-1-1.html

(出处: EETOP 创芯网论坛 (原名:电子顶级开发网))

法2:也可以在侧边栏中打开Grids-placement Grids和Routing Grids,依据grids和最小的snap space通过s和a手动移动版图中的器件和线。 此时也可不画尺子,之间按g打开引力吸附,更方便吸附到格点上,通过s拉伸和a快速对齐进行操作。

enable DRD grid checking来验证版图是否off grids,操作方法options-DRD options-interactive -enable;DRD options-Filters-选中Grids

B和Sub不是一个东西,特别是对PMOS。B的全称是Bulk,也叫Backgate,PMOS的B是N-Well的引出端,而衬底通常是P型的。实际应用的时候,PMOS的S/B通常接Vcc,而Sub通常接GND。

对于非隔离的NMOS,其P-Well的引出端和Sub连在一起,所以把B端叫Sub没问题。但对隔离型NMOS,其B端与Sub之间有N型隔离阱,存在寄生结构,此时B与Sub不能混为一谈。

B端也不总是与S短接,有些应用中会利用B与S的电压差来获得可调节的Vth,这也是B端也被叫做Backgate的原因。

这种是软连接即softconnect的问题。正常来说你的nmos器件都放在p衬底上,衬底应该接同样的电位。但是你现在接了不同的电位,就出错了。解决方法有两个:1、将其中一个电位的器件放在DNWELL里,或者将两个电位的器件分别放在不同的dnwell里,这是最彻底的解决方法。这个方法的思路就是讲这两部分器件分别放在不同的衬底上。2、如果你的vss 和gnd最终在封装时都是接在一起,并且在你当前的模块中没有防止衬底互相干扰的要求,只是为了解决验证问题,你也可以将其中一个衬底的器件用类似于psub2这样区别衬底的标识层圈起来,这样验证也能通过。

取消器件自动合并:Layout Editor Options里面的Abut Server取消勾选就行了,默认快捷键shift+E打开Layout Editor Options

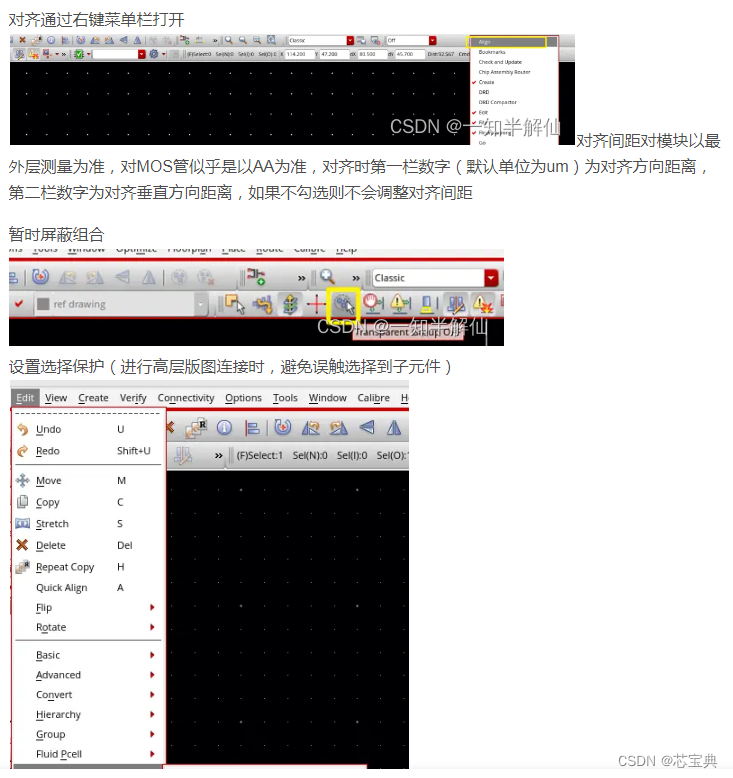

Align对齐

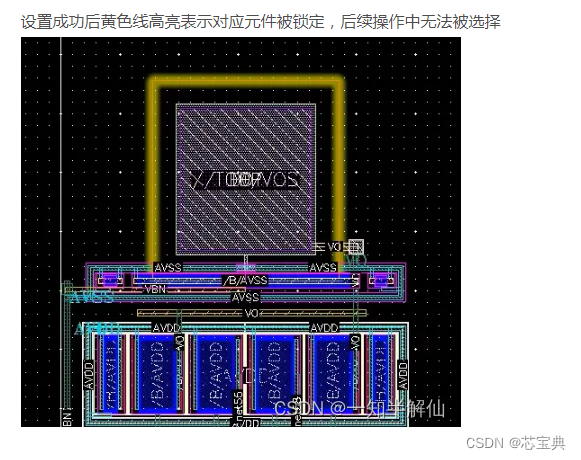

屏蔽子模块功能

来自以下链接Cadence Virtuoso Layout 版图绘制的使用技巧及其相关快捷键_一知半解仙的博客-CSDN博客_virtuoso版图快捷键

| 版图中Metal 线宽选择 https://bbs.eetop.cn/thread-577895-1-1.html 一 金属线是为了传输电流,因此主要需要从解决和减小它的(寄生)电阻、(寄 生)电容方面多做考虑。(寄生)电感一般忽略,高频电路除外。这主要从两个 方面分析解决: 1.电路方面 A、如果所用金属线,主要是流过电流(如电流镜MOS 管的漏极连线、功率MOS 管的漏极等)。在这种情况下金属连线的寄生电阻越小越好,此时需要金属导线 尽可能的宽,以减少寄生电阻,降低导线压降IR。 B、如果所用金属线,是用于高频信号,如clock 等,金属连线不能太宽,否则 寄生电容过大,影响频率。此时信号还应加shield 信号线。 C、其他低频控制信号,如enable 、able 等信号,这些信号通常接MOS 管的栅 极,流过的电流很小,这些金属连线宽窄(寄生电容、寄生电阻)不是很重要, 不需要过多考虑。 2. 版图方面(在考虑金属线周围环境的前提下) A、对于走大电流的信号线,从电路方面越宽越好,但从版图方面很宽的金属线 由于受到工艺、物理条件等的制约会受到限制。过宽的金属线,由于高温、应力 等影响,会翘起变形甚至折断。所以很宽的金属线需要打slot,slot 的尺寸因各 个工艺厂的工艺不同而有区别。 另外,由于趋肤效应,电流走金属表面和边缘,金属线太宽也不好,这样金 属的线上电流分布不均匀。电流很大时应采取两种方式排布金属线:同层金属线 并联(类似很宽金属线打了slot);不同金属线并联,过孔要尽可能多打,节省 面积。 B、不同层金属导线的连接,要尽可能打更多的通孔via,以减少寄生电阻。过孔 尺寸和个数最少的情况因电路和工艺而定。 C、越靠近AA(有源区)的金属例如M0,尽量不要从上面经过MOS 管、敏感 电阻等器件。因为在金属线的工艺后期处理中(高温溅射、刻蚀、退火等)会影 响这些器件的性能。尽可能换用更高层的金属线。 另外:有些电路中专门需要用金属线做电阻的,宽度和长度需要单独考虑。 二 Metal 太大太宽,会导致电流密度不好,会导致电迁移、趋肤效应等现象, 会降低可靠性和影响良率。 1.我们为什么要走很宽的金属Metal 呢? 原因无非是电路要求电流的承载能力要达到很大。常见的地方如:电源线、 功率开关管上连线、芯片的地线等,这种线会走的很宽。如果我们直接用很宽的 Metal 线,后果是,随着温度的升高,大块的金属中间会拱起来(热胀冷缩),这 样会破坏绝缘层,损坏芯片。久而久之,即使运气好,芯片没有被损坏,运气不 好的,这根金属很大可能会断掉,断掉的后果大家都懂的——直接断路。 2.如何解决宽金属的问题呢?想必这是大家最为关心的事情。 大家都知道要打slot(槽,有slot rule,品字形,顺着电流开),slot 打了之后, 即便是金属断掉了,也不会全断。一种方法,是把金属重叠着走,这个当然需要 足够的金属层,就是采取不同金属层的并联。另一种方法,如果是只用一层金属 的话,可以直接将宽金属线拆分成多条细金属并排(最细的金属线要满足design rule),类似于金属并联,其实也可以理解成Metal Bus(总线)。 3.注意金属密度问题。 还有一点,有人提到很宽的金属会造成金属密度过大,影响金属覆盖率。金 属的覆盖比例Metal ratio:30%-55%之间为最佳(根据所用工艺而言),比例偏 离的话,铝腐蚀就不好,不干净或过腐蚀。不知道大家在交GDS 的时候有没有 修改这个DRC 错误,这个会直接影响产品良率,我们都是修改OK 之后交的, 所以应该注意这个问题。 三 金属宽度首先要满足电流条件,一般规则上都有明确说明,比如静态电流经 验值大概1.5mA/um(有的是1mA/um,根据具体工艺而言),但高温、大电流、 台阶等情况下会有所下降,大概1mA/um(有的是0.6-0.8mA/um,根据具体工艺 而言)。这里指的是通常情况。静态电流密度的大小主要受电迁移、趋肤效应、 金属材质等问题的影响。 而动态电流大小对应的宽度一般规则上也会写明,通常会以能量、峰峰值、 均值等来衡量,动态电流密度的大小也主要受电迁移、趋肤效应、金属材质等问 题的影响。 对应不同的情况需要满足不同的约束。在满足电流的约束条件后,就需要考 虑信号频率的因素了,频率越高的信号走线适当要细,因为寄生电容影响较大。 如果需要流过很大电流,则需要很宽的金属,一般工艺规则都会规定最小与最大 的金属宽度,最大的金属宽度是要防止电流不均匀导致电迁移、趋肤效应以及发 热不均匀的问题,当然还有热胀冷缩的问题。 此外,过宽的金属会使得中间部分略有下沉导致平坦化的问题,所以需要在 过宽金属上打slot。注意,工艺规定的最大线宽不会直接写出来,而是通过slot 的规则隐含其中。比如规定很宽的金属在里面超过多少间距要打slot,这里规定 的间距其实就是最大的金属线宽,另外有些工艺规则会规定不同层的金属有不同 的最大宽度。 |

文章详细介绍了集成电路版图设计过程中的关键步骤和注意事项,包括金属线宽的选择、电流承载能力、寄生电阻和电容的考虑、电迁移和趋肤效应、版图规则检查以及如何处理宽金属线问题。同时,提到了CadenceVirtuoso工具在版图绘制中的快捷键和使用技巧。

文章详细介绍了集成电路版图设计过程中的关键步骤和注意事项,包括金属线宽的选择、电流承载能力、寄生电阻和电容的考虑、电迁移和趋肤效应、版图规则检查以及如何处理宽金属线问题。同时,提到了CadenceVirtuoso工具在版图绘制中的快捷键和使用技巧。

4611

4611

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?