74HC165:

74HC165是8位并行读取或串行输入移位寄存器,可在末级得到互补的串行输出(Q7和!Q7),当异步并行读取引脚(!PL)输入为低时,从D0到D7口输入的并行数据将被读取进寄存器内。而当异步并行读取引脚为高时,数据将在每个时钟脉冲的上升沿从DS引脚串行进入寄存器并将现有数据右移一位。利用这种特性,只要把Q7输出绑定到下一级的DS输入,即可实现移位寄存器位数的扩展。

具体电路如图所示:

注:该电路将CE#(输出使能)接地,即输出一直有效,并采用三级级联的方式共有24个输入端口。

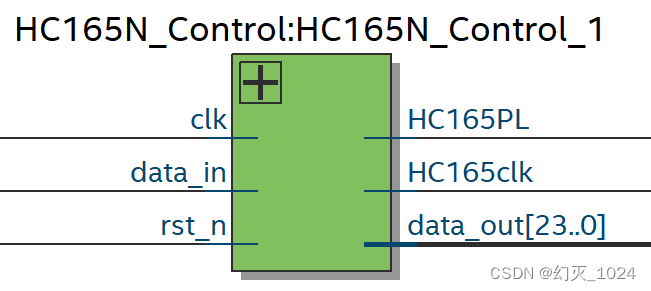

RTL设计:

//基于Verilog的HC165N控制模块

module HC165N_Control #(

parameter clock_freq = 50_000_000

)(

input wire clk ,

input wire rst_n ,

input wire data_in ,

output reg HC165clk,

output reg [23:0] data_out,

output reg HC165PL

);

parameter fps = 50_000; //刷新速度

reg [23:0] data_tmp; //数据缓冲

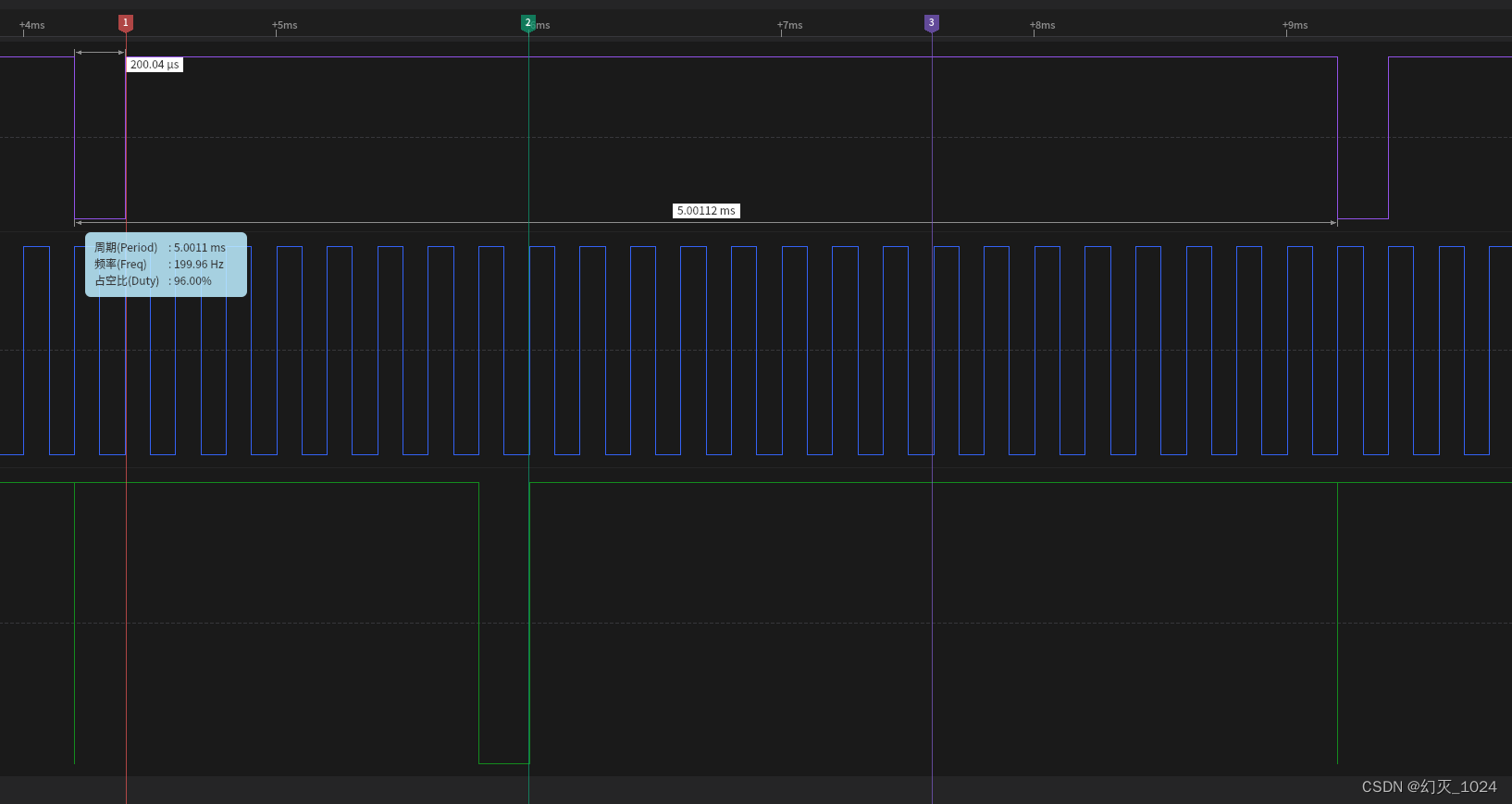

//分频器(二分频)为165提供时钟信号

reg [22:0] clk_div_cnt;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n) begin

clk_div_cnt <= 0;

HC165clk <= 0;

end

else

if(clk_div_cnt == fps) begin

clk_div_cnt <= 0;

HC165clk <= !HC165clk;

end

else begin

clk_div_cnt <= clk_div_cnt + 1;

HC165clk <= HC165clk;

end

end

//读取HC165N数据

reg [4:0] HC165N_cnt;

always @(posedge HC165clk or negedge rst_n) begin

if(!rst_n) begin

HC165N_cnt <= 0;

end

else if(HC165N_cnt >= 25) begin

HC165N_cnt <= 0;

end

else begin

HC165N_cnt <= HC165N_cnt + 1;

end

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

HC165PL <= 1;

data_out <= 0;

end

else begin

case (HC165N_cnt)

0: begin

HC165PL <= 0;

end

1: begin

HC165PL <= 1;

data_tmp[0] <= data_in;

end

2: begin

data_tmp[1] <= data_in;

end

3: begin

data_tmp[2] <= data_in;

end

4: begin

data_tmp[3] <= data_in;

end

5: begin

data_tmp[4] <= data_in;

end

6: begin

data_tmp[5] <= data_in;

end

7: begin

data_tmp[6] <= data_in;

end

8: begin

data_tmp[7] <= data_in;

end

9: begin

data_tmp[8] <= data_in;

end

10: begin

data_tmp[9] <= data_in;

end

11: begin

data_tmp[10] <= data_in;

end

12: begin

data_tmp[11] <= data_in;

end

13: begin

data_tmp[12] <= data_in;

end

14: begin

data_tmp[13] <= data_in;

end

15: begin

data_tmp[14] <= data_in;

end

16: begin

data_tmp[15] <= data_in;

end

17: begin

data_tmp[16] <= data_in;

end

18: begin

data_tmp[17] <= data_in;

end

19: begin

data_tmp[18] <= data_in;

end

20: begin

data_tmp[19] <= data_in;

end

21: begin

data_tmp[20] <= data_in;

end

22: begin

data_tmp[21] <= data_in;

end

23: begin

data_tmp[22] <= data_in;

end

24: begin

data_tmp[23] <= data_in;

end

25: begin

data_out <= data_tmp;

end

default: begin

data_out <= data_out;

end

endcase

end

end

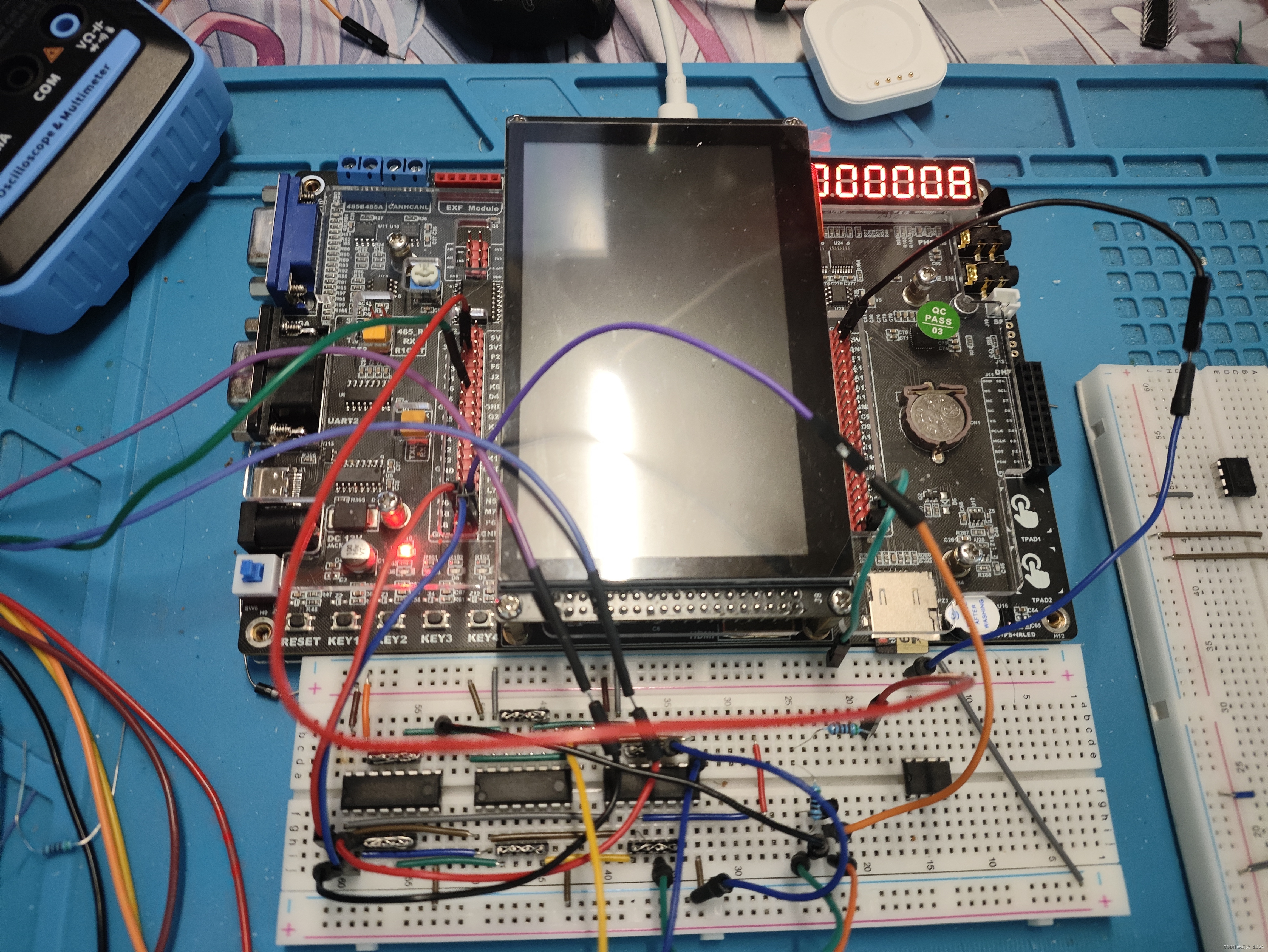

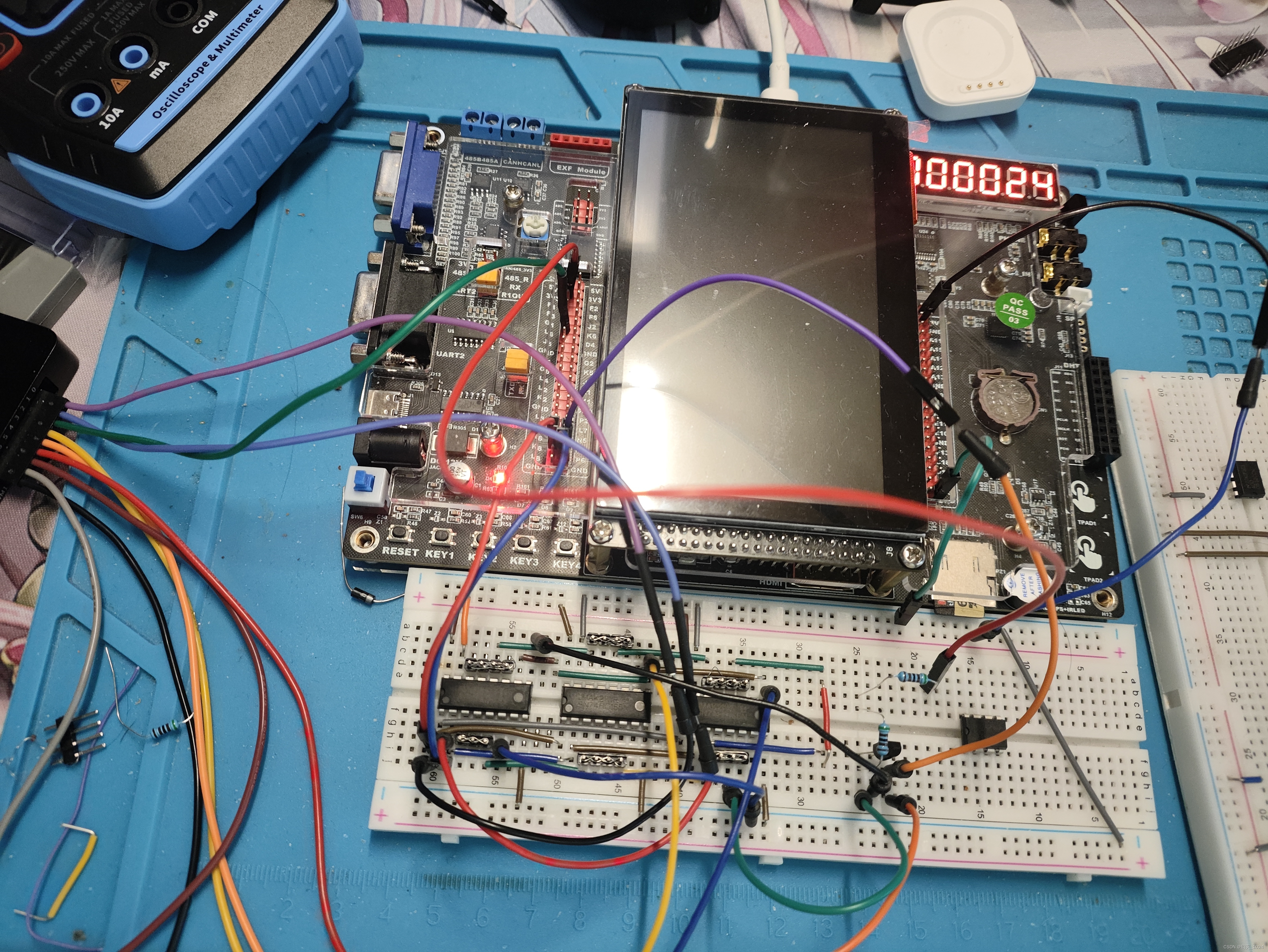

endmodule实际测试:

599

599

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?