verilator——牛刀小试

安装verilator可见:https://blog.csdn.net/qq_40676869/article/details/132648522?spm=1001.2014.3001.5501

正文开始

编写一个异或的电路模块如下:

top.v

module top(

input a,

input b,

output f

);

assign f = a ^ b;

endmodule

编写C++测试文件

tb_top.cpp

#include <stdio.h>

#include <stdlib.h>

#include <assert.h>

#include "verilated.h"

#include "verilated_vcd_c.h"

#include "Vtop.h"

#define MAX_SIM_TIME 200

vluint64_t sim_time = 0;

int main(int argc, char** argv) {

Vtop *dut = new Vtop;

Verilated::traceEverOn(true);

VerilatedVcdC* m_trace = new VerilatedVcdC;

dut->trace(m_trace, 5);

m_trace->open("waveform.vcd");

while (sim_time < MAX_SIM_TIME) {

int a = rand() & 1;

int b = rand() & 1;

dut->a = a;

dut->b = b;

dut->eval();

printf("a = %d, b = %d, f = %d\n", a, b, dut->f);

m_trace->dump(sim_time);

sim_time++;

assert(dut->f == (a ^ b));

}

m_trace->close();

delete dut;

return 0;

}

编译并运行

verilator --cc --trace --exe --build -Wall tb_top.cpp top.v

–cc 将.v文件翻译成c++

–exe 创建可执行文件

–build verilator自动进行make

–trace 记录波形

查看波形

sudo apt install gtkwave

gtkwave waveform.vcd

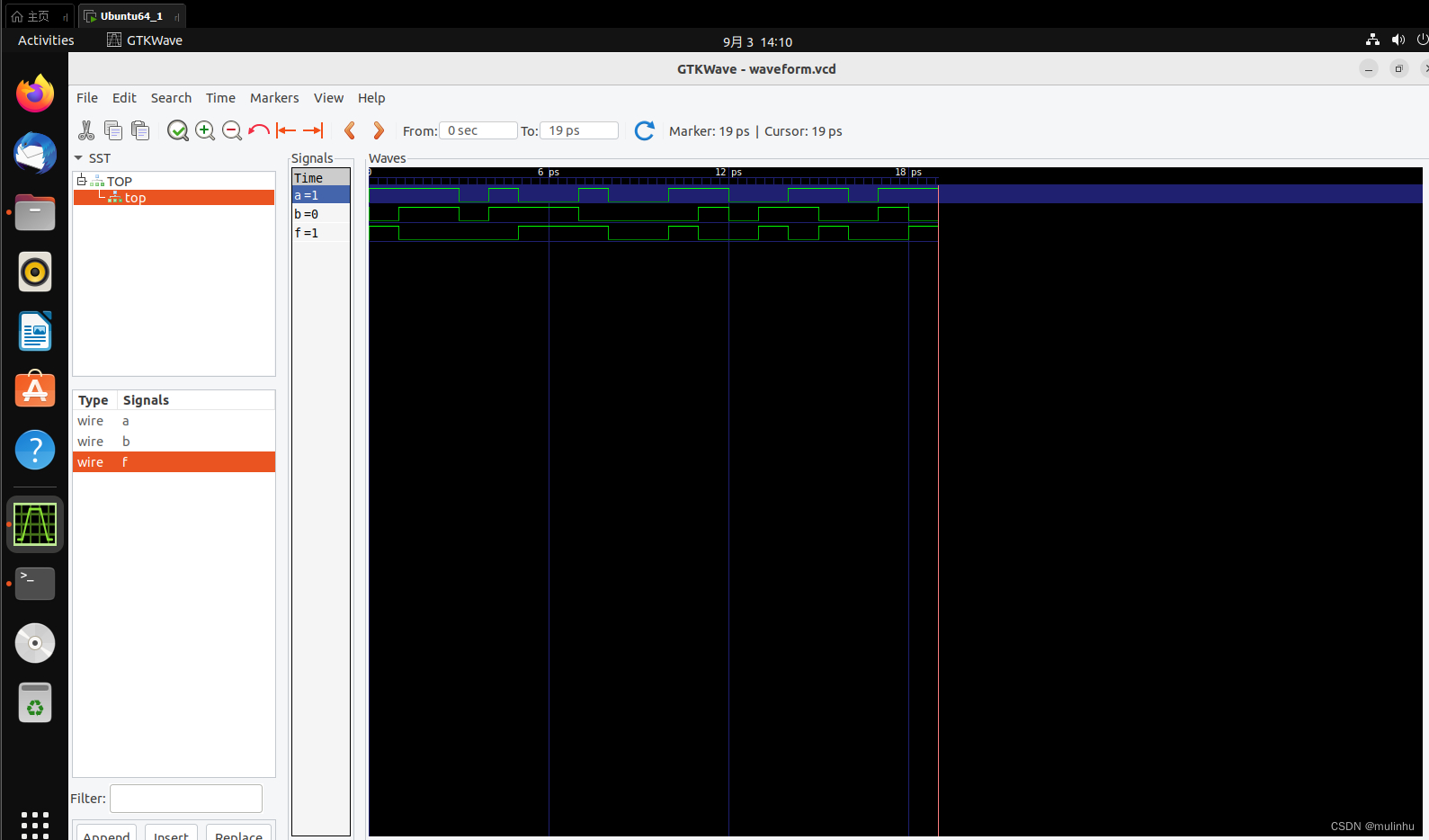

波形如下:

github链接:https://github.com/mulinhu/CPPer/tree/main/verilog/demo1

980

980

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?