首先说明(叠个甲),这里的笔记是课程中的试学课,如果觉得侵权请联系删帖。

目录

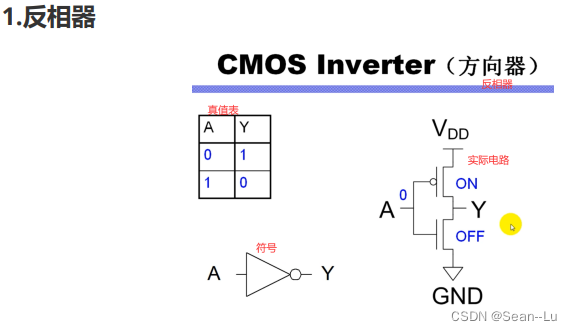

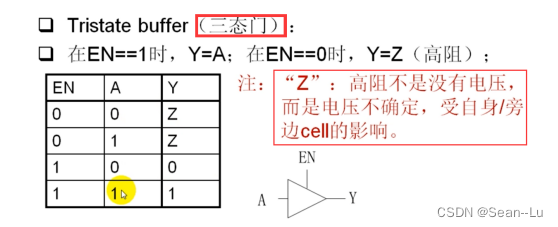

1.基本组合电路单元

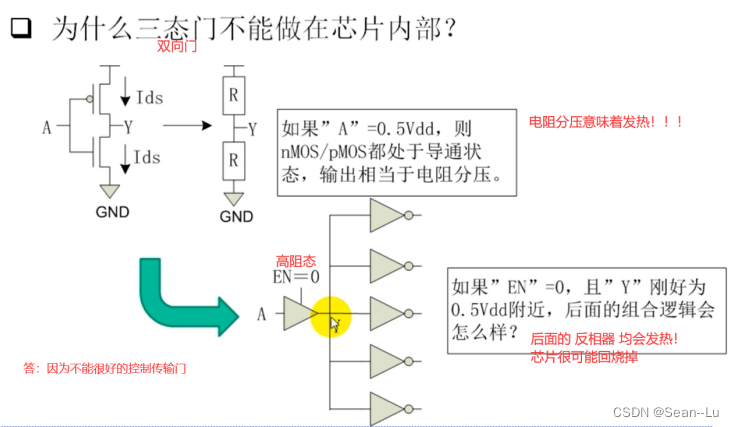

为什么三态门不能做在芯片内部?

答:因为不能很好的控制传输门位于高阻态的情况下,三态门输出连接驱动的组合逻辑的状态,其有很 大概率会处于一个全导通的状态,导致电路功耗上升,可能损毁。

那为什么又可以作为I/O?

答:如I2C,会要求在板子上对应处添加一个上拉电阻,此时芯片内部Y处于高阻态时,会被板子上的上 拉电阻稳定一个电平,固定一个状态。

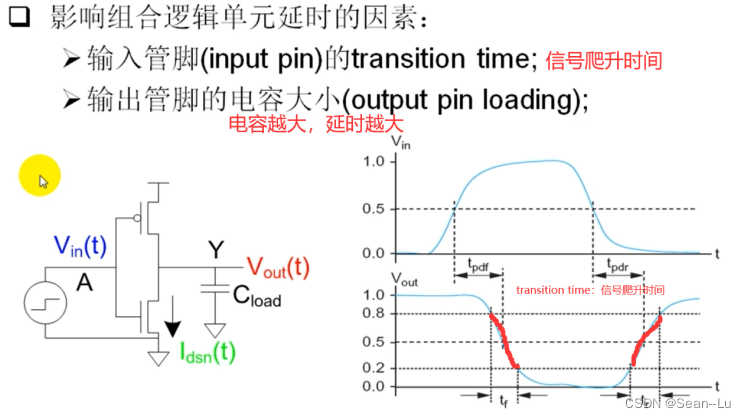

2.组合逻辑延时因素

1.组合逻辑延时

2.组合逻辑与时序逻辑定义/区别

一个直观的理解 组合逻辑:

输入改变,输出在经过一个delay后马上改变,输入输出是一个很直接的对应关系。

时序逻辑:有一定的存储功能。输入改变时,输出有可能维持之前的状态。

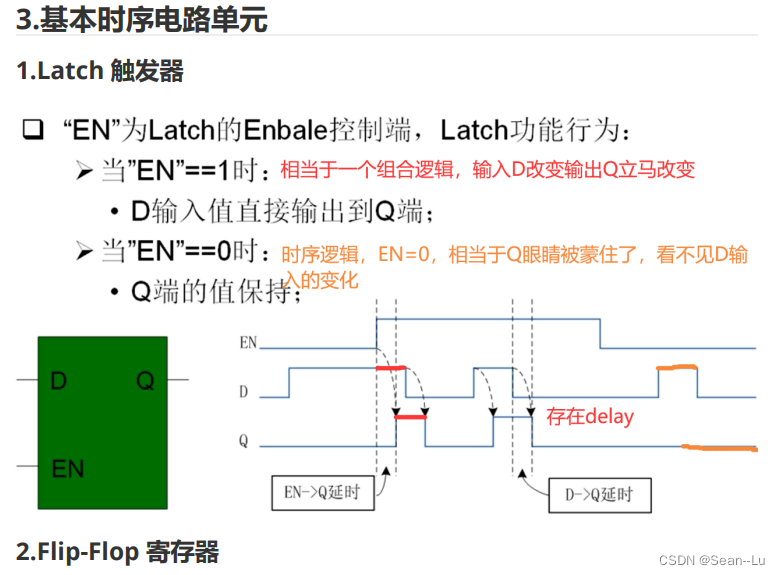

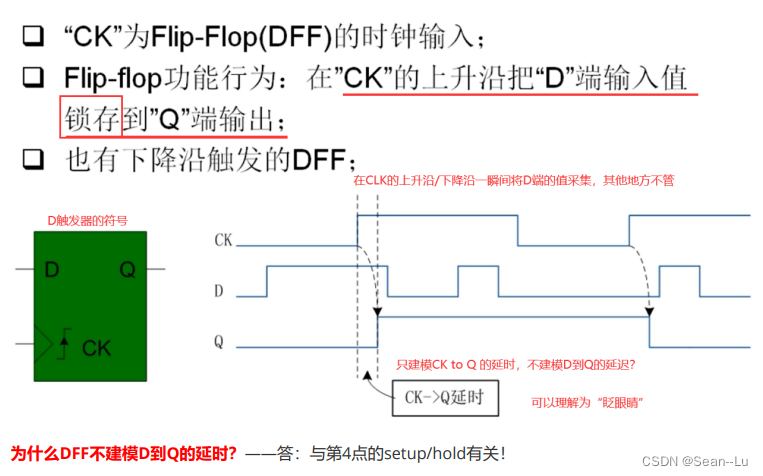

3.基本时序电路单元

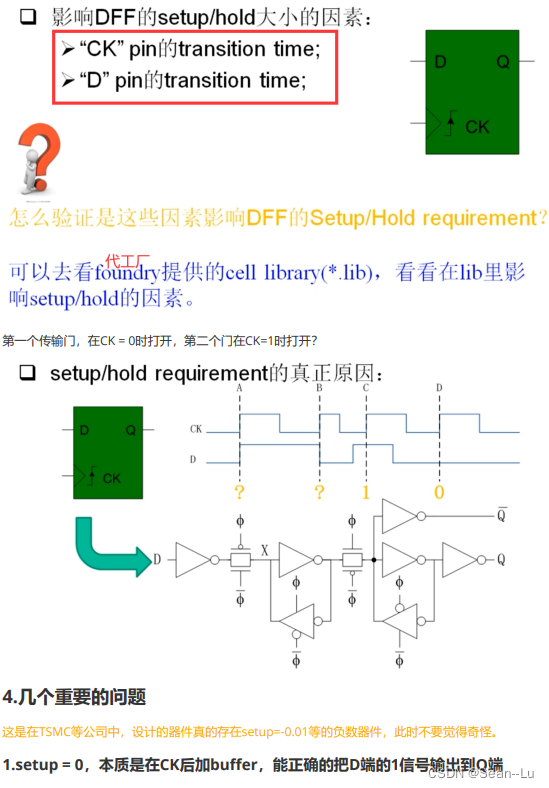

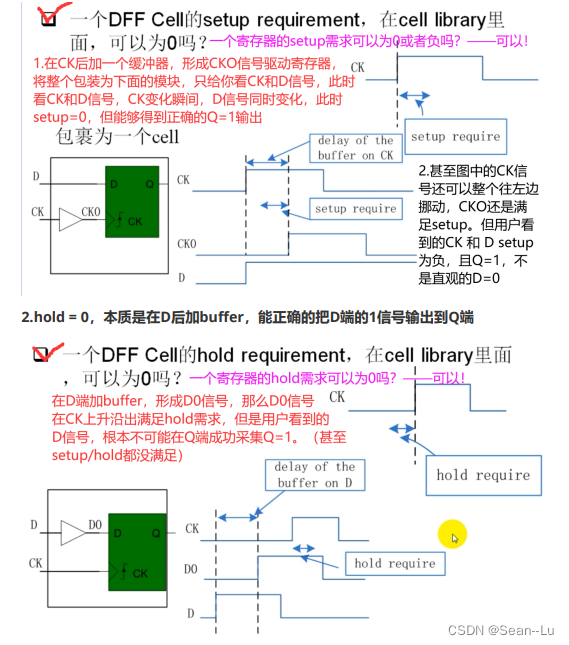

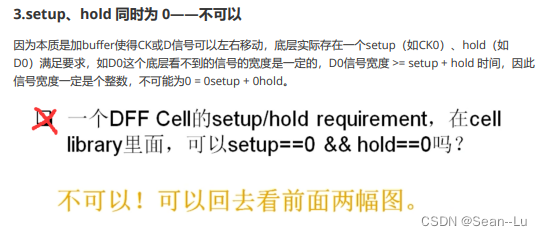

4.寄存器(DFF)setup/hold

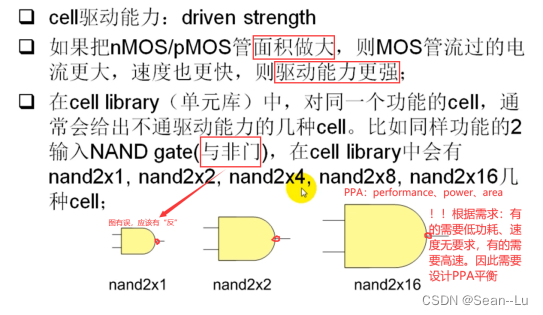

5.驱动能力

893

893

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?