数字IC设计工具教程——VCS(lab1)

参考:Synopsys VCS lab1

注:VCS(Verilog Compile Simulator)

文章目录

Getting Started

本实验使用以下8bit进位选择加法器:

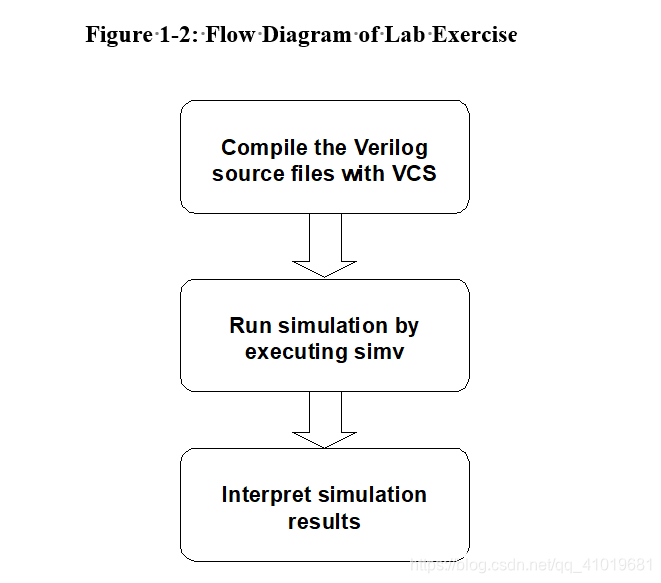

我们的目标是使用这个简单的设计来了解两步VCS仿真过程的基础。 本实验分为三个部分。 每个部分都有其自己的关联任务。 这是将要做的事情的预览:

- 编译加法器Verilog源文件以生成仿真可执行文件。

- 通过执行仿真可执行文件来仿真8位加法器。

- 解释控制台上显示的仿真结果,以确定8位加法器是否正常工作。

- 在A部分中,8位加法器的所有Verilog源文件都位于工作目录中。

- 在B部分中,一些8位加法器的Verilog源文件在工作目录中,其余的在库目录中。 您将对其进行编译,然后使用编译时文件来简化VCS编译命令行键入。

Part A: 两步仿真流程

Task 1: 编译生成仿真可执行文件

在lab1的A部分中,所有8位进位选择加法器的Verilog源文件都位于lab1工作目录中。登录到工作站后,进入lab1 Part A目录。

1. shell> cd VCS_labs/lab1/parta

应该看到4个文件:fa.v,add4.v,add8.v和addertb.v

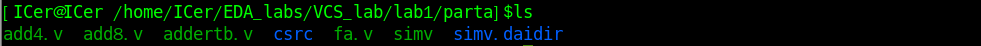

2. shell> ls

fa.v,add4.v和add8.v是图1-1中块的Verilog源文件,addertb.v是用来检验加法器功能的testbench。

编译Verilog文件并生成simv仿真二进制可执行文件。

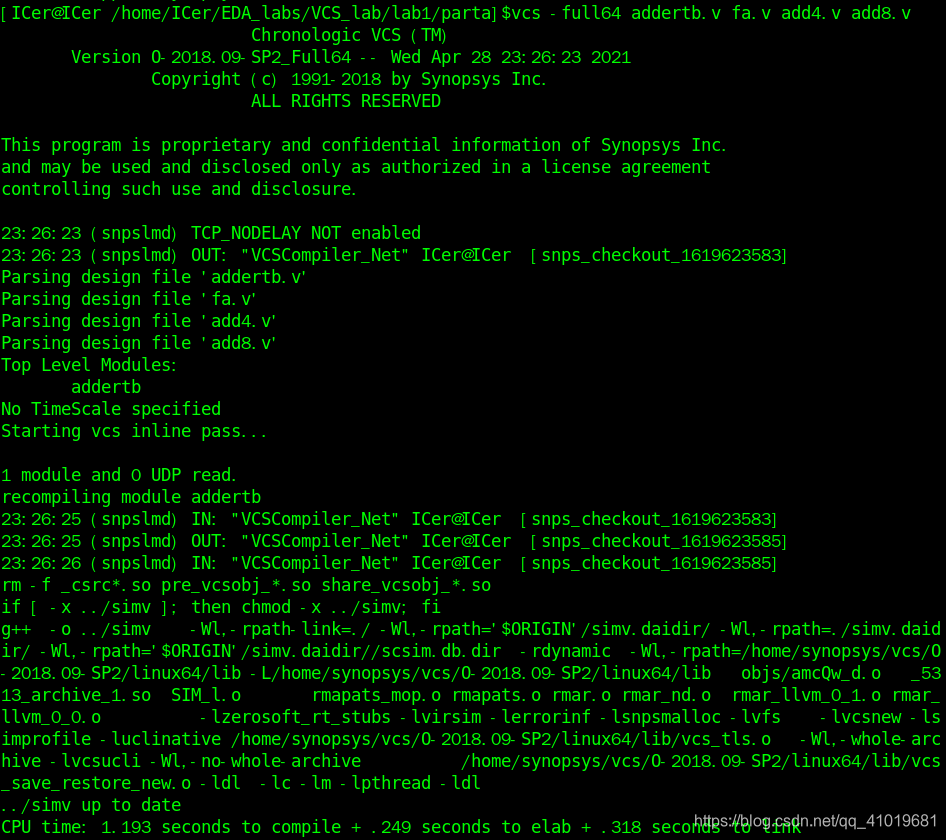

3. shell> vcs -full64 addertb.v fa.v add4.v add8.v

当编译完成,将会看到下面信息:

当编译完成后,所在的目录文件中会产生csrc、simv、simv.daidir三个文件,其中simv是编译后的仿真可执行文件。

Task 2: 运行仿真

运行testbench并通过执行simv来仿真设计。

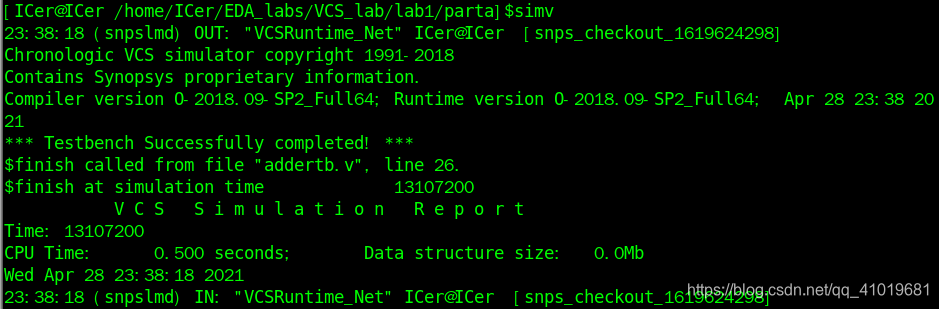

1. shell> simv

当仿真结束,将看到下面信息:

表明仿真已经结束,仿真时的CPU用时与存储占用空间情况也会被报告。

Task 3: 检查仿真结果

通过嵌入在testbench中的Verilog系统任务调用,上面的报告中将会看到下面的打印输出。

*** Testbench Successfully completed!***

这验证了执行是成功的!在lab2中我们将看到如何生成信息来帮助我们debug代码错误。

Task 4: 用不同的名称创建仿真可执行文件

VCS默认的仿真可执行文件名是simv。我们可以使用–o开关引导VCS生成不同的可执行文件名称。

编译Verilog文件并生成addertest仿真二进制可执行文件。

shell> vcs -full64 addertb.v fa.v add4.v add8.v -o addertest

Part B: 使用库目录

Task 1: 用设计的库目录编译&仿真

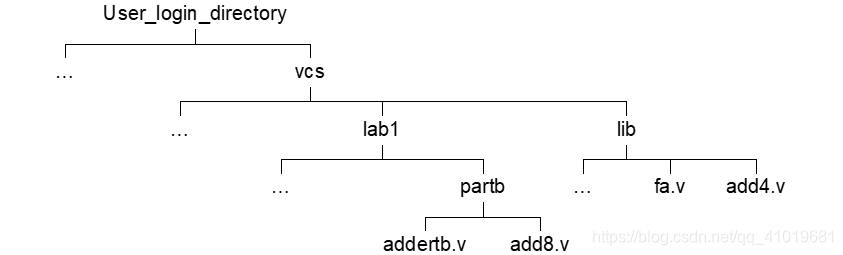

在lab1的Part B,我们把fa.v和add4.v移动到库目录(lib)。新的文件目录结构如下所示。

切换到lab1 Part B工作目录。只有两个文件add8.v和addertb.v。再一次编译设计,这次,我们需要参考库目录(lib)文件。

可以将–R开关作为速记,在编译后立即执行仿真。

shell> vcs -full64 addertb.v add8.v –y ../../lib +libext+.v -R

注意,由于我们的库文件具有.v扩展,因此需要+libext开关才能让vcs搜索.v扩展文件。

源文件内容没有改变,只有文件的物理位置发生了变化,应该看到与Part A相同的仿真结果。

Task 2: 用"-f File"开关编译

使用–f编译时间开关简化命令行输入。 首先创建一个包含设计的所有源文件或库名称的文件。 在编译设计时,用–f开关参考该文件。

使用gvim创建文件"adder.f"包含下列文件。

addertb.v

add8.v

-y ../../lib +libext+.v

用-f开关编译并仿真设计,如下所示。

shell> vcs -full64 -f adder.f -R

编译仿真结果和之前的一样。

540

540

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?