参加完电子设计竞赛不知不觉快过去两个月了,今天小刚写一下当时我们这道题的方案。

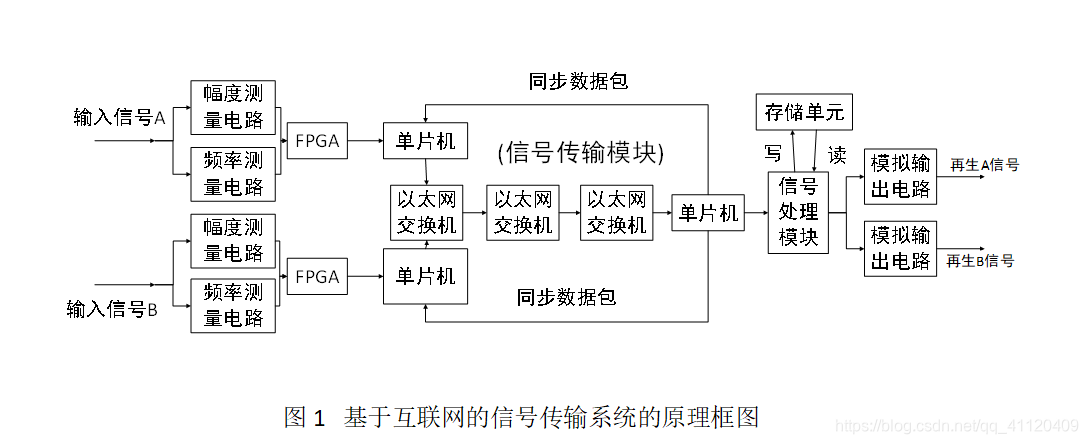

本系统基于互联网的信号传输系统采用STM32F407ZGT6和FPGA Cyclone IV作为主控芯片,对信号进行采样和处理。系统由幅度测量电路、频率测量电路、信号传输电路、信号处理电路、模拟输出电路等部分组成。FPGA采得一点的相位和幅度信息后,通过STM32和以太网交换机传输给模拟输出电路,模拟输出电路把点信息写入寄存器并循环读寄存器产生信号,可通过按键切换选择恢复一路或者两路的信号。相位同步通过发送端和接收端互传含时间戳的数据包实现,由接收端快速收发同步数据求出延时补偿。

本系统由幅度测量电路、频率测量电路、信号传输模块、信号处理模块、模拟输出电路五部分组成。幅度测量电路和频率测量电路从信号中提取出相位、幅度和频率等信息,传输给单片机。A、B端的单片机与C端单片机进行网络通信,构成信号传输模块。网络延时等于C端发送给A、B端同步数据包再立即返回所需时间的一半,求出延时补偿后对数据包中的时间戳进行修正。C端的信号处理模块以大容量的Xilinx ARTIX-7 FPGA为核心,以寄存器为储存单元,存储已经压缩成500个点以内的信号数据,模拟输出电路循环读取储存单元即可输出信号。按键可以切换再生A和B信号。

1.互联网传输策略

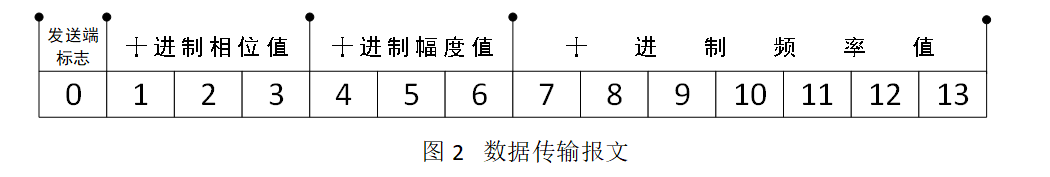

互联网传输以探索者STM32F4开发板为核心,使用UDP协议。发送端A、B端传至接收端C端的报文如下:1位发送端标志“A”或“B”+3位十进制相位+3位十进制幅度值+7位十进制信号频率。数据传输报文如图2所示。

2.网络时间延迟测量及补偿

网络延迟数据包每秒发送一次,用于求得网络延迟。方法是由C端发送一个只含一个字符“T”的数据包,同时开启计时器计数。A和B端接收后立马返回一个同样的数据包,C端接收到后停止计时器,网络延迟等于计时器计时的一半。

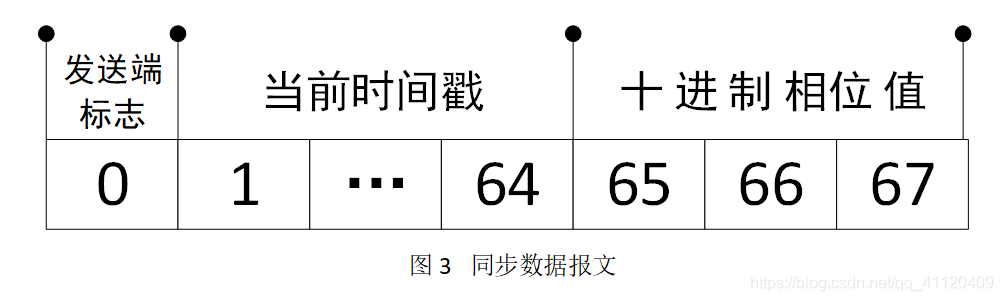

另外,A和B端会不停地向C端发送同步数据包,报文如下:1位发送端标志“A”或“B”+63位当前时间戳+3位十进制幅度值。这个同步数据包的意义是:发送端在指定的时间戳,信号运行到了指定的相位,将这个目标相位和当前相位比较,再小幅度增大或减小输出信号的周期以接近目标相位,这样就能够同步信号。同步数据报文如图3所示。

硬件电路设计

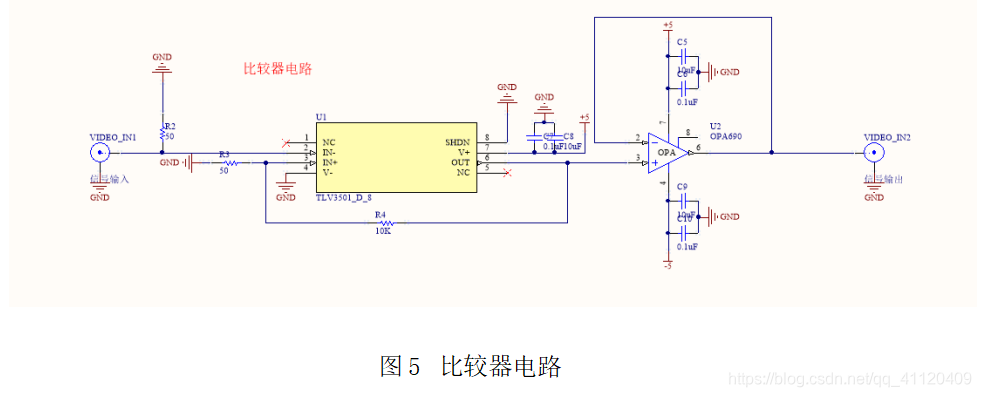

输入信号为周期信号,由于要采集输入信号的周期,所以要将输入信号通过比较器TLV3501将其转为周期性的矩形波信号给FPGA进行处理,测量其周期大小。由于输入幅值可变,所以通过迟滞比较器,将门限电压设置在零点附近,后级采用电压更随器实现信号隔离和阻抗匹配。比较器电路如图5所示。

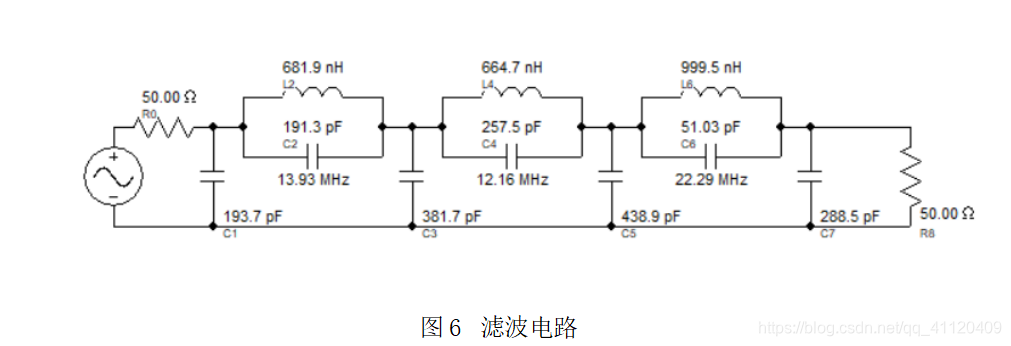

3)滤波电路

由于最后一级的输出信号是通过DAC产生电所以要加一级低通平滑滤波器,滤波器采用7阶椭圆滤波器,将截止频率设置在10MHz。采用filter-solutio软件设计参数,滤波器电路参数如图6所示。

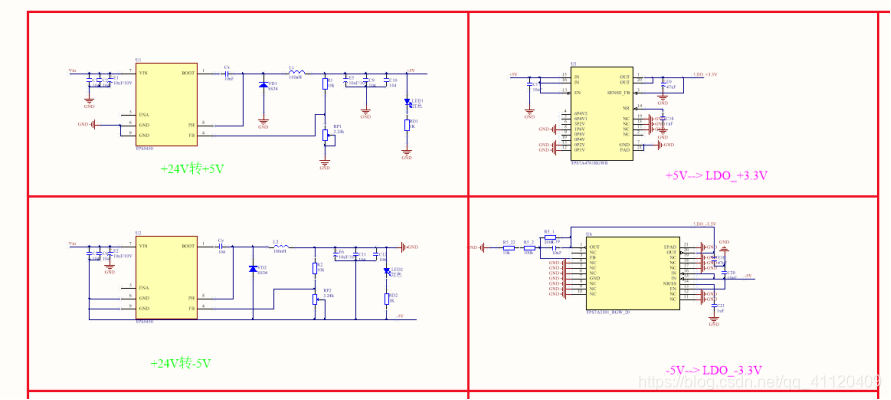

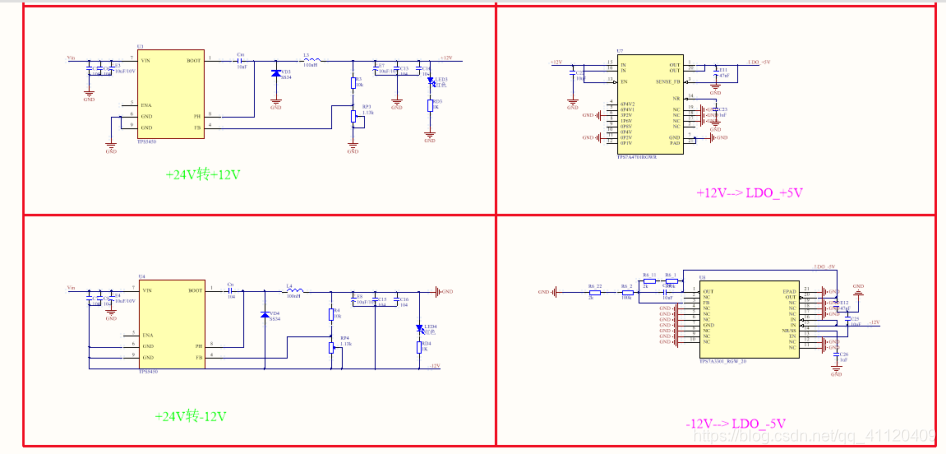

电源原理图:

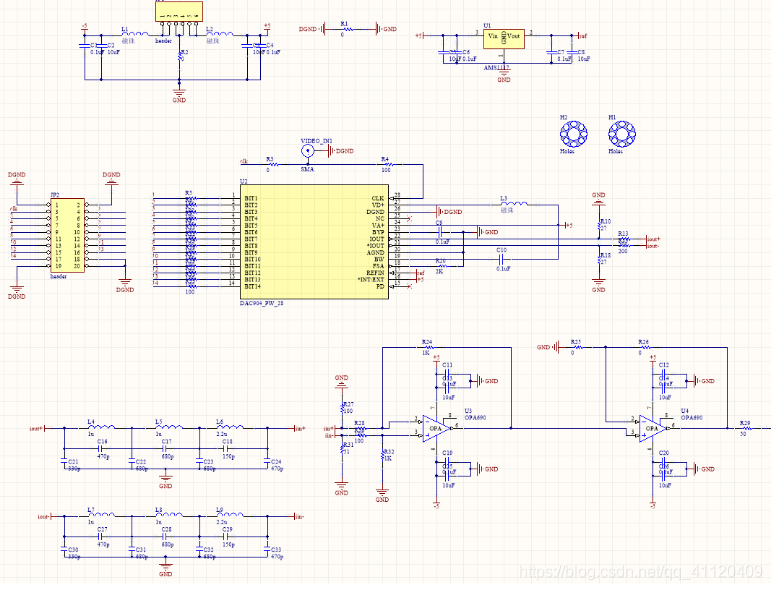

ADC采用的是ADC10065:

DAC为DAC904:

这道题做下来感觉平时硬件的训练都没有用武之地,这道题关键在软件,软件也调的心累,主要是相位同步吧。

四天三夜基本靠软件,不过数据传输过程中会在信道里引入干扰,最后滤波器比较重要。那几天真的是心有余而力不足,虽然最后结果还算满意但是还有一丝丝不甘心——审题不仔细漏掉好几个得分点。

接下来要多学学软件,学学算法。

保持初心,保持进步吧!

本文介绍了一种基于STM32F407ZGT6和FPGACycloneIV的互联网信号传输系统设计方案,该系统能对信号进行采样、处理,并通过网络传输。系统包含幅度测量、频率测量、信号传输、信号处理和模拟输出电路,利用相位同步和延时补偿技术实现信号的精确传输。

本文介绍了一种基于STM32F407ZGT6和FPGACycloneIV的互联网信号传输系统设计方案,该系统能对信号进行采样、处理,并通过网络传输。系统包含幅度测量、频率测量、信号传输、信号处理和模拟输出电路,利用相位同步和延时补偿技术实现信号的精确传输。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?