时序分析总结

本文为小梅哥和西南交大邸老师时序约束课程笔记,仅供个人学习。

1. 基本知识

1.1 时序约束的作用

告知EDA软件时序指标,EDA软件会根据尽力优化布局布线,以达到该 时序指标,使得从D触发器的输出到目的触发器的输入之间的延迟要小于一个 时钟周期。同时产生相应的时序报告。

1.2 建立时间和保持时间的关系

1.2.1 Latch edge 的关系

Setup check: latch edge是launch edge的后一个沿

Hold check: latch edge是l和launch edge是同一个沿,hold check和时钟周期没有关系

》》》Hold check latch edge = setup check latch edge – 1(前一个周期)

1.2.2 slack 的关系

slack(setup) = data_require time - data_arrival time

slack(hold) = data_arrival time - data_require time

1.3 pcb走线延时

走线延迟计算公式:5555mil/ns

100mil = 2.54mm ==> 5555mil = 0.0254*5555 = 141.097mm

T(ns) = mm/141.097

2. 典型模型的时序分析

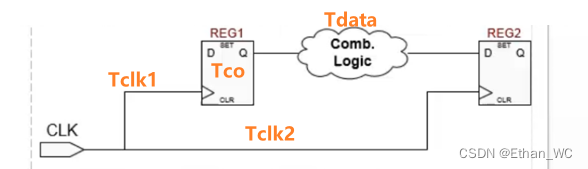

2.1 Reg2Reg模型

2.1.1 建立时间

data_arrival time = Tclk1 + Tco + Tdata

data_require time = Tclk + Tclk2 - Tsu

slack(setup) = require - arrival time

建立时间的存在,要求数据在源寄存器和目的寄存器之间的传输时间不能太短,否则建立时间违例。

2.1.1 保持时间

data_arrival time = Tclk1 + Tco + Tdata

data_require time = Tclk2 + Th

slack(hold) = data_arrival time – data_require time(注意,建立时间的刚好相反)

注意:保持时间的launch edge和latch edge是同一个edge(注意,建立时间的刚好差一个时钟周期)

在FPGA内部,时钟往往走的专门的时钟网络,一般情况下都是比数据快的。所以在FPGA内部更常见的是建立时间的报错,而非保持时间。FPGA内部不用理会保持时间报错。保持时间的报错往往出现在源同步IO约束那里。

2.2 IO 约束

IO约束就是通过告知EDA软件一些IO传输路径上的已经知道的时间参数,来让EDA软件编译并控制FPGA内部的各个路径传输延迟,使得总的路径能够满足建立时间为正的目的。

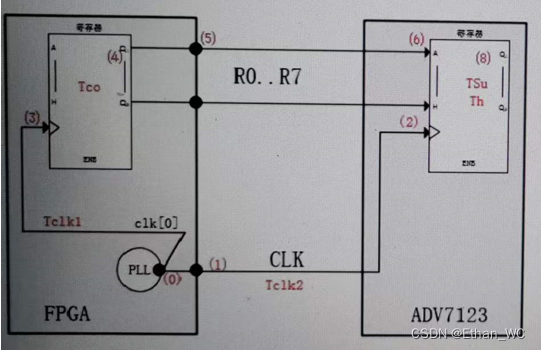

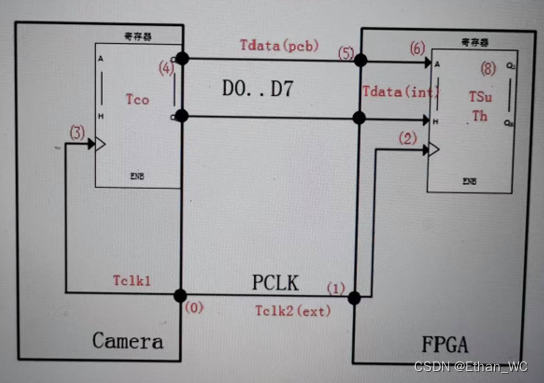

2.2.1 源同步ouput IO 约束

建立时间

data arrival time = launch edge + Tclk1 + Tco + Tdata(in) + Tdata(pcb)

data require time = latch edge + Tclk2(in) + Tclk2(ext) – Tsu

Slack(su) = data require time – data arrival time >= 0

<将已知量放在一侧,未知量放在另外一侧>

(Latch edge – Launch edge) + Tclk2(ext) – Tdata(pcb) – Tsu >= -Tclk2(in) + Tclk1 + Tco + Tdata(in)

最大输出延迟:output delay max : Tdata(pcb) - Tclk2(ext) + Tsu

通过让编译器综合出最优的布线(尽量FPGA内部到输出延迟最小),使得数据经过最大的外部传输延迟到达目的寄存器时依旧满足目的寄存器的建立时间

保持时间

data arrival time = launch edge + Tclk1 + Tco + Tdata(in) + Tdata(pcb)

data require time = latch edge + Tclk2(in) + Tclk2(ext) + Th

slack(hold) = data arrival time – data require time

launch edge – latch edge + Tdata(pcb) - Tclk2(ext) - Th >= -Tclk1 -Tco -Tdata(in) + Tclk(in)

最小输出延迟:Output delay min : Tdata(pcb) - Tclk2(ext) – Th

为什么是最小?数据非常快的到达目的寄存器的D端口,而此时万一时钟比较慢,导致保持时间不满足。

数据经过最短的外部延迟时间到达目的寄存器依旧满足目的寄存器的保持时间

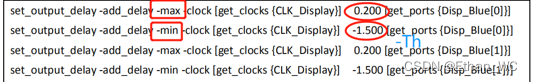

等长处理

若外部pcb做工对数据和时钟走线作等长处理,那么Tdata(pcb) = Tclk2(ext) (数据和时钟走线等长处理的重要性)

等长处理后,时钟走线和时钟走线延迟一样。

即:

output delay max: Tsu

Output delay min: -Th

注意output delay min 是负值

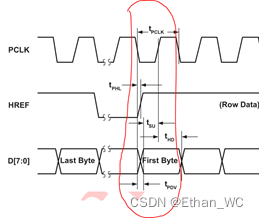

2.2.2 源同步input IO 约束

建立时间

data arrival time = launch edge + Tclk1 + Tco + Tdata(pcb) + Tdata(in)

data require time = latch edge + Tclk2(ext) + Tclk2(in) – Tsu

slack(su) = data require time – data arrival time = launch edge – latch edge + Tclk2(ext) – Tclk1 – Tco -Tdata(pcb) >= -Tclk2(in) + Tsu + Tdata(in)

注意:Tclk1 + Tco在前级手册中会给出,一般命名就是Tco

最大输入延迟 Input delay max = Tdata(pcb)- Tclk2(ext) + Tco

Input delay max: 数据经过最大的外部传输路径延迟,到达FPGA的寄存器时,还能满足该寄存器的建立时间。

理论上,Input delay max = Tdata(pcb)(max) - Tclk2(ext)(min) + Tco(max)

保持时间

data arrival time = launch edge + Tclk1 + Tco + Tdata(pcb) + Tdata(in)

data require time = latch edge + Tclk2(ext) + Tclk2(in) + Th

slack(hold) = data arrival time – data require time = latch edge – launch edge + Tclk1 + Tco + Tdata(pcb) – Tclk(ext) >= -Tdata(in) + Tclk2(in) + Th

最小输入延迟 Input delay min = Tdata(pcb) – Tclk2(ext) + Tco

Input delay min:数据经过最小的外部传输路径延迟,到达FPGA的寄存器时,还能不破坏该寄存器接受前一个时钟沿外部器件发射的数据。要能够满足改寄存器的保持时间。

理论上,Input delay min = Tdata(pcb)(min) - Tclk2(ext)(max) + Tco(min)

等长处理

在同一个模型下,不可能时钟按快的传,数据按慢的传。所以在同一个模型下,如果做了等长处理,Tdata(pcb)和Tclk2(ext)抵销。

即:

Input delay max = Tco(max)

Input delay min = Tco(min)

====

对于OV7670 Tpdv就是我们所说的camera的Tco

Tco max = 5ns

Tco min = 0ns

Tpdv 即为Tco

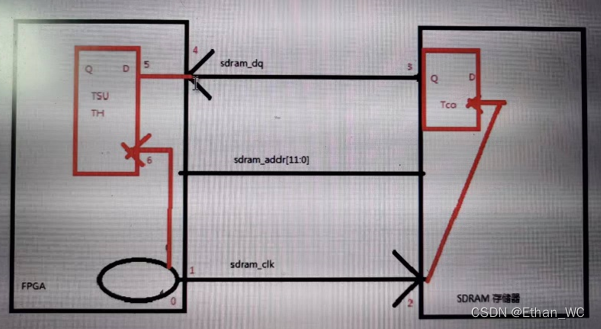

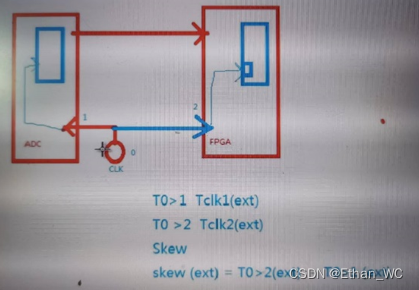

2.2.3 时钟和数据反向的IO 约束

2.2.3.1 FPGA出时钟收数据。

这里fpga的触发器是接收端,数据是由sdram发出的,而时钟是由fpga发出的,与典型的源同步模型不同。

2.2.3.1.1 建立时间

data arrival time = launch edge + Tclk1(in) + Tclk1(ext) + Tco + Tdata(pcb) + Tdata(in)

data require time = latch edge + Tclk2(in) – Tsu

slack(tsu) = data require time – data arrival time = latch edge – launch edge – Tclk1(ext) – Tco – Tdata(pcb) >= -Tclk2(in) + Tsu + Tclk1(in) + Tdata(in)

最大传输延迟Input delay max = Tclk1(ext) + Tdata(pcb) + Tco

2.2.3.1.2 保持时间

data arrival time = launch edge + Tclk1(in) + Tclk1(ext) + Tco + Tdata(pcb) + Tdata(in)

data require time = latch edge + Tclk1(in) + Th

slack(hold) = data arrival time – data require time = launch edge – latch edge + Tclk1(ext) + Tco + Tdata(pcb) >= -Tclk1(in) – Tdata(in) + Tclk1(in) + Th

最小传输延迟Input delay min = Tclk1(ext) + Tco + Tdata(pcb)

2.2.4 IO约束总结

2.2.4.1 初步小结

- input delay 时钟和数据方向相同的情况下

Input delay max = Tdata(pcb) - Tclk2(ext) + Tco

Input delay min = Tdata(pcb) - Tclk2(ext) + Tco - input delay 时钟和数据方向相反的情况下

Input delay max = Tdata(pcb) + Tclk1(ext) + Tco

Input delay min = Tdata(pcb) + Tclk1(ext) + Tco - output delay 时钟和数据方向相同的情况下

Output delay max = Tdata(pcb) - Tclk2(ext) + Tsu

Output delay min =Tdata(pcb) - Tclk2(ext) – Th - output delay 时钟和数据方向相反的情况下

Output delay max = Tdata(pcb) + Tsu

Output delay min = Tdata(pcb) – Th

2.2.4.2 一般归纳

归纳:一般的

Tskew(ext) = Tclk2(ext) – Tclk1(ext)

Input delay max = Tdata(pcb) – Tkew(ext) + Tco(max)

Input delay min = Tdata(pcb) – Tkew(ext) + Tco(min)

用一个公式表示,不管时钟和数据方向怎么样。

在方向相同的时候,Tclk1(ext)为0;方向相反时,Tclk2(ext)为0

即使时钟在电路板上发的,即不在fpga中也不在adc中。也可以用这个公式。

注意以上方向都是 fpga接受数据的情况下来讨论数据和时钟的不同方向而总结出来的公式。

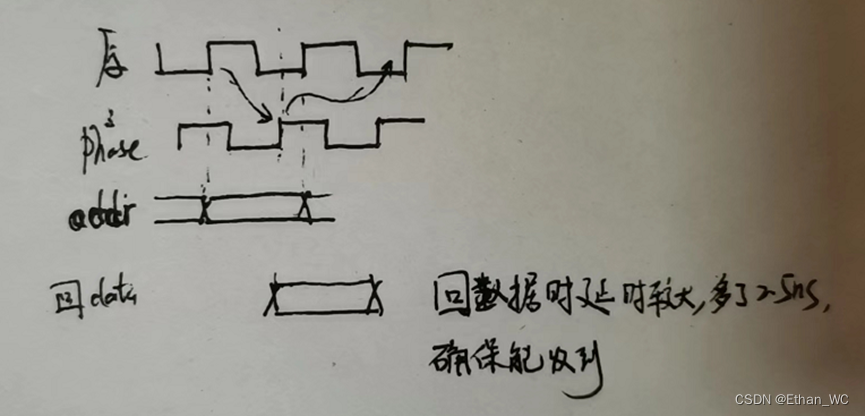

回数据的时候需要根据路径(pcb)计算延时!!!

通过走线计算延迟:5555mil/ns

100mil = 2.54mm ==> 5555mil = 0.0254*5555 = 141.097mm

T = mm/141.097

3 其他

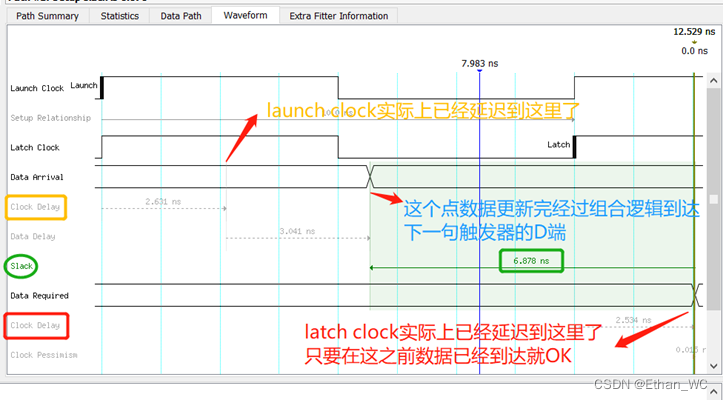

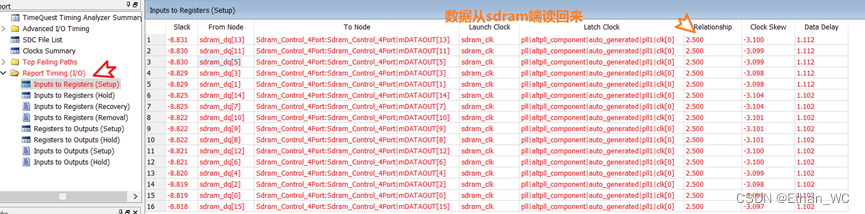

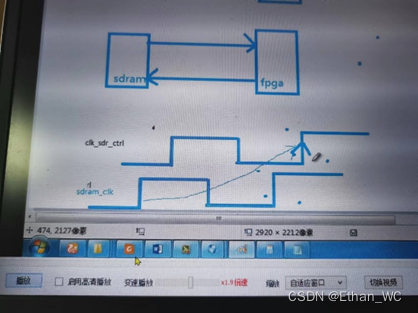

3.1 相位有偏移,则多周期约束

时序约束中 遇到时钟相位有偏移(如PLL移相90°等等)的情况要特别注意

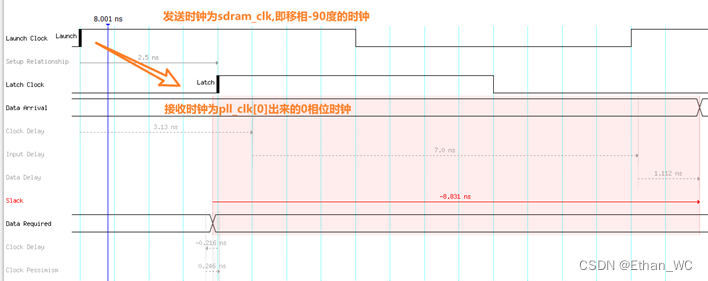

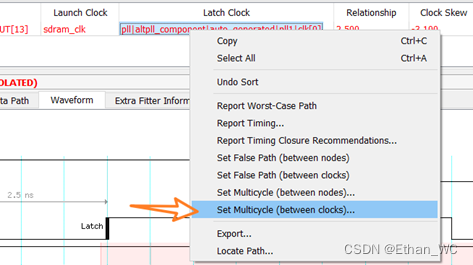

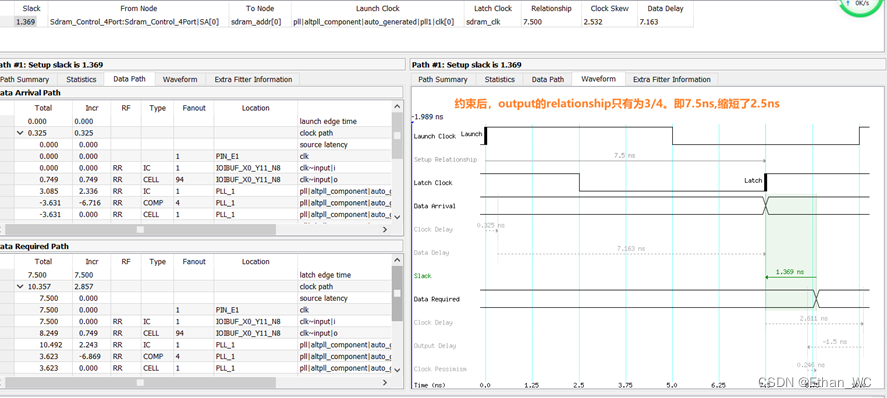

软件在计算launch edge和latch edge的时候,会傻乎乎的认为只要出现launch edge后面出现的最近的沿就是latch edge,就会导致下面的情况,看relationship竟然是2.5ns,不到一个时钟周期,而2.5ns对应400M,我们的时钟只有100M.

但其实这个最近的沿也是launch edge,只不过被PLL延迟了90°的相位。

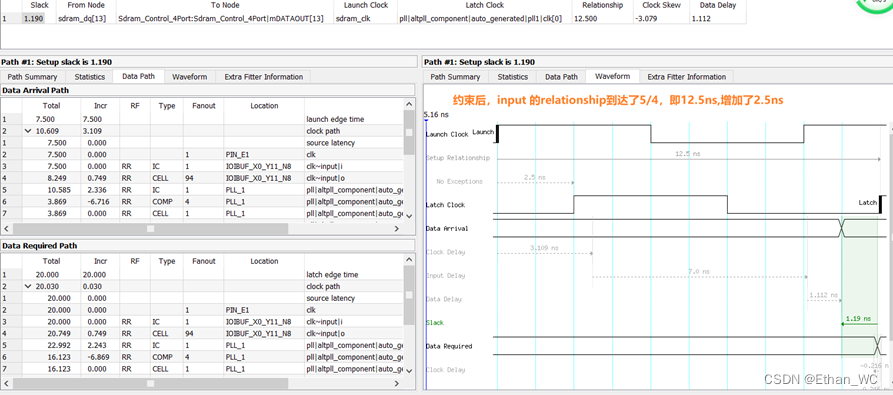

可以看到,因为这个延迟补充了2.5ns,给数据传输带来更大的余量。Relationship 应该为10ns + 2.5ns = 12.5ns

==》》》 做多周期约束

为什么sdram_clk是﹣90度的时钟?(提前90°)

因为output是同源的,比较好布局布线,而input的走线延迟比较长(是pcb上的clk和data相加)。通过牺牲output的relationship来加大input的relationship

所以有的sdram控制器的sdram_clk之前的移动相位180,分的有点大了,发送才5ns(1/2),读数据是绰绰有余的,是15ns(3/2)。

3.2 一些问题

问:如果两个芯片连,前级芯片做了output delay约束后,后级的芯片还需要做input delay嘛?

需要的,因为单看前级芯片,它是不知道后级的延迟是多少的,这时候需要人为告知,它才能尽可能的编译出一个比较好的布线结果。

对于后级芯片,也是一样的,它也不知道前级的延时是多少,也需要知道前级的延时才好去编译出好的布线结果。

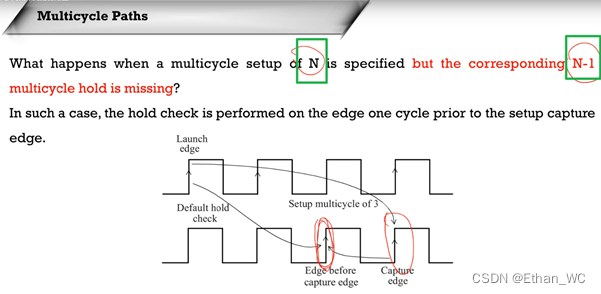

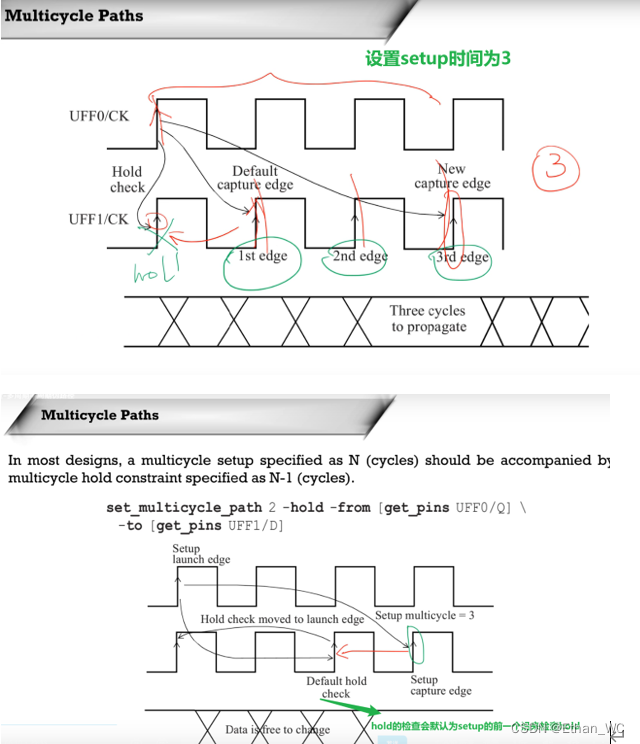

3.3 多周期半周期相关

3.3.1 多周期(组合逻辑超过一个时钟周期)

Setup 设为n

Hold 设为n-1

Hold检查会默认在setup的前一个沿来检查hold.

组合逻辑太慢,在最慢的时候检查setup,建立时间设为3

在最快的时候有可能第一拍刚发出去就算完了,若按照默认的hold沿来检查hold,那么就要要求数据要保持2个时钟周期。为了避免这一不正常的、过于严苛的做法,hold检查沿还需要在default基础上往前移动2个时钟周期。即set_multicycle_path 2 -hold -from xxxx

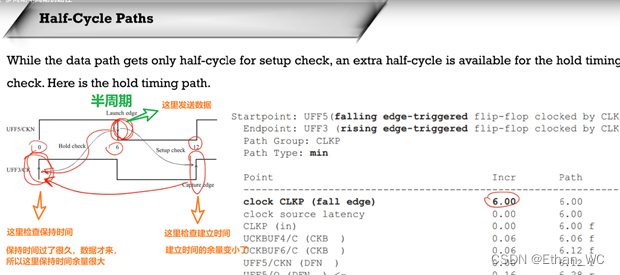

3.3.2 半周期

在A电路打一些数据给B电路时候,通常使用半周期。

半周期的优点是建立时间非常紧,因为它只有半个周期。而保持时间非常充裕。

因为建立时间违例比较好修复,但是hold time违例没有好的办法去修复。使用半周期可以优先让hold time满足。

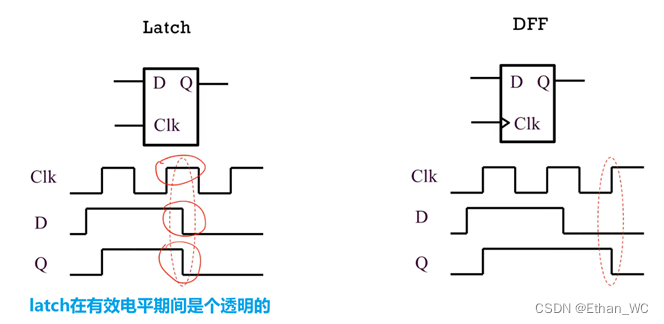

3.4 锁存器(latch)都有害嘛?

3.4.1 Time Borrowing

锁存器在有效电平期间是透明的,在无效电平期间锁存。所以在高电平期间类似于组合逻辑,对毛刺敏感。

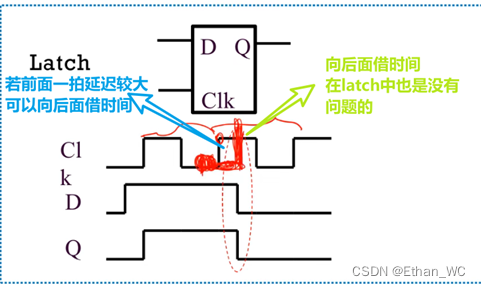

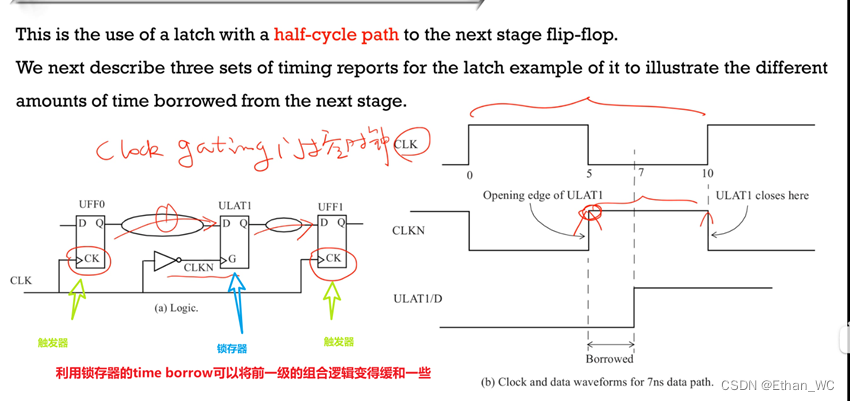

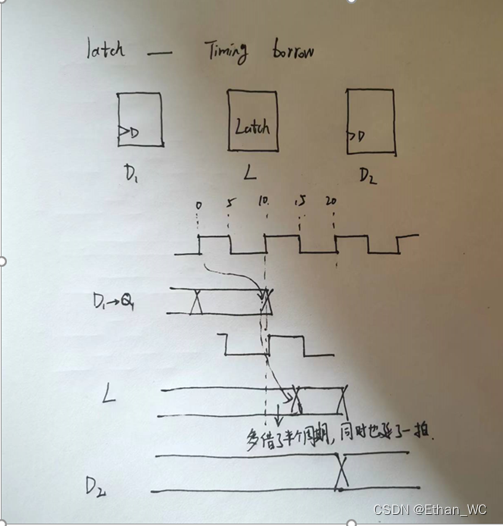

在latch中有个特点是,如果前一拍的延迟较大,可以向后面借时间,后一拍只要在有效电平内到来就ok.这个就是所谓的time borrowing

利用latch的time borrow可以将前一级的组合逻辑变得缓和一些。可以向后一级多借半个周期,但是也需要多延迟一拍。

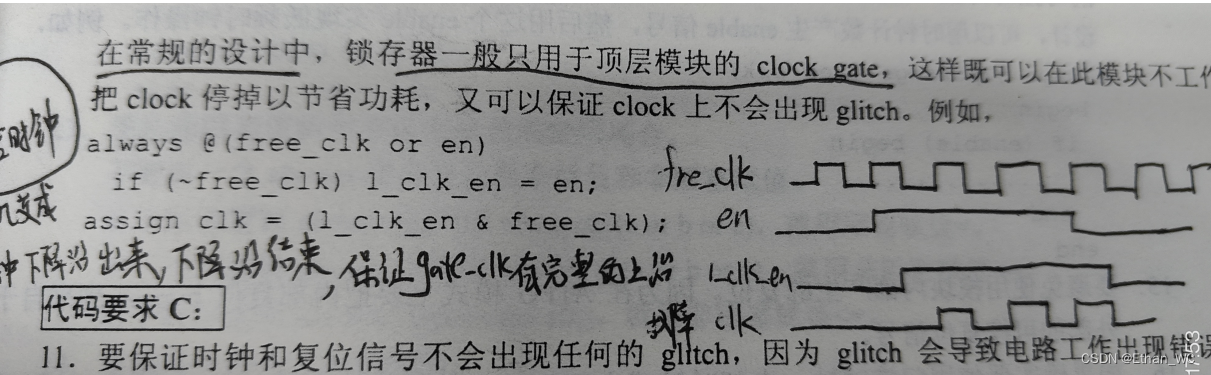

3.4.2 门控时钟利用锁存器消除毛刺

问题:门控时钟容易产生毛刺,如何消除毛刺?

通过一个负沿的锁存器将en信号进行整型,让其和时钟信号对齐,这样en和clk相与后的时钟就是比较规整的。

通常这个ICG在IC库里就是做好的单元,直接用即可

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?