10G Ethernet Subsystem 学习记录

说明:本文摘自 V3学院 尤老师的培训班笔记,仅用于个人学习,不用于任何商业用途。

满足个人在公交车上或者其他需要不得不等待的时间段内学习的需要。

-

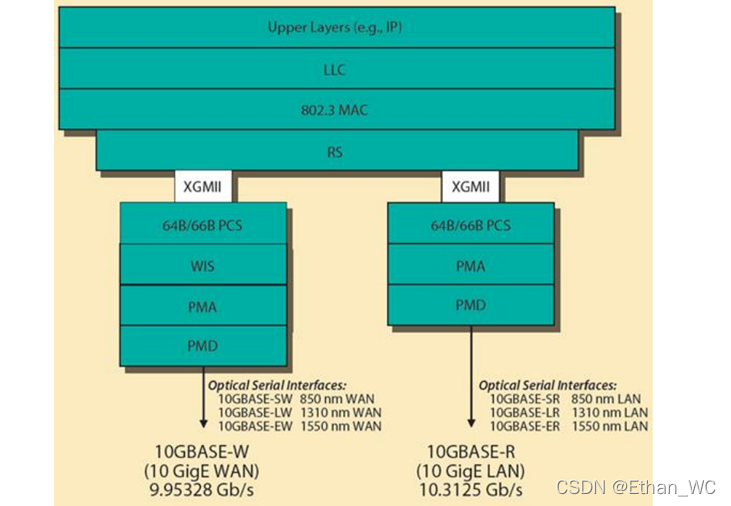

10GBASE-R 是一种使用 64B/66B 编码,数据流为 10.3125Gbit/s。一般情况下参考时钟为156.25M。为什么?

10312.5/156.25=66

每1bit的时钟为10.3125Gbit/s,那么如果是每66bit为一个数,那么其采样时钟就是10312.5/66=156.25M. (64b/66b)

============= -

10 GigeE WAN 广域网

10 GigeE Lan 局域网

可以通过电缆或者光纤来传输

============= -

千兆以太网接口:RGMII

万兆以太网接口:XGMII (X为希腊数字中的10,代表10G)

都是可以双沿传输的,但是10G subsystem 的 IP只支持XGMII 单沿。RS层把XGMII协议中的包头包尾都去掉,裸露出数据,传递给MAC层。MAC层转化为AXI-Stream的数据流传到LLC。LLC中需要我们自己写一些代码,把数据解出来或者反过来组帧一些数据发给MAC,MAC再—>RS-------……

-

发送数据是小头模式,先发低字节,再发高字节。

============= -

为什么要把XGMII接口单独拿出来做开发?

在一些特定的场景,希望万兆以太网取数据的过程是最快的,lantance是最小的。在这里做文章,可以使得取出的数据最快。

============= -

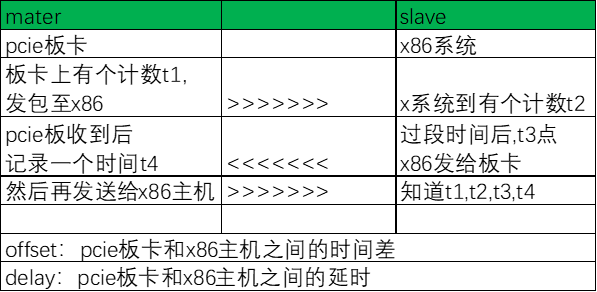

高频交易里边:万兆以太网接收到数据的包通过pcie传给x86系统,传给x86之间的延迟是不怎么方便去计算的。

他们希望从接受到这个包到传给pcie的这个时间要尽可能的短,那问题来了,我不知道这个中间的延迟大概有多少?因为pcie板卡和x86系统的时钟是不同步的。所以需要有一个基本测定延时的方法。

可以使用ieee1588的这个时钟校准的方法来移植到高频交易里边去测定延时。

也可以借助外部的GPS秒脉冲进行同步,更加精准,绝对同步。

在高频交易里谁的delay越小,谁就先能拿到最新的行情信息。

里边有个小技巧,就是我们在master(pcie板卡)中的计数器如何去转化成和x86系统同一概念的时间,这里尤老师没有去细说。自己想想。

============= -

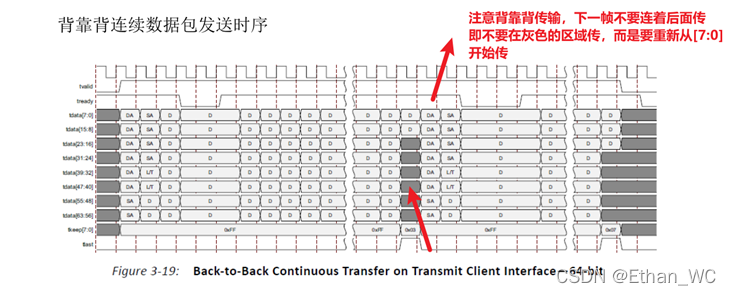

如果用背靠背的连续发包时序,会按照最小的帧间隔(12字节)去传输。如果帧间隔比较小,上位机可能会丢包,缓存不过来。

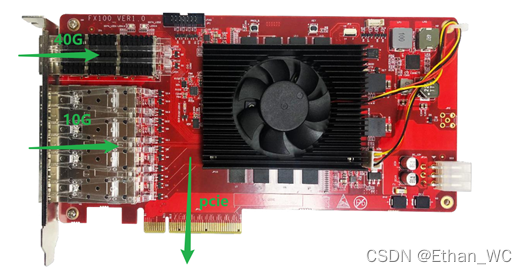

板载pcie的板卡接上万兆的接口,通过pcie的接口把数据load到x86这一端。这种情况可以使得以太网的包可以大量的传递。

即万兆进去,pcie出来给电脑主机

============= -

注意背靠背的传输下一帧需要重新从[7:0]开始传。

============= -

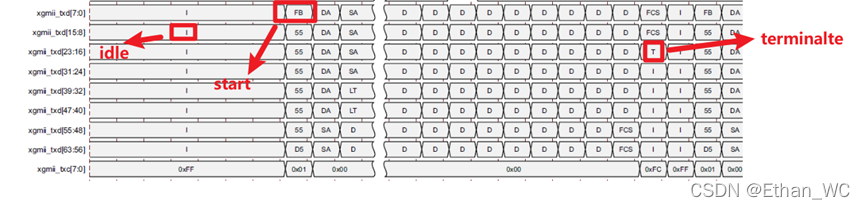

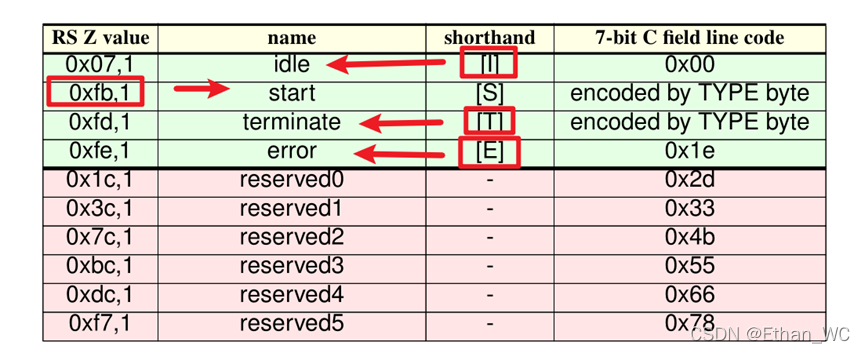

Fb –> start

I –> IDLE

T –> terminate

E –> error

============= -

K7的板子,Pciex8, 加8对高速接口,支持10G以太网。

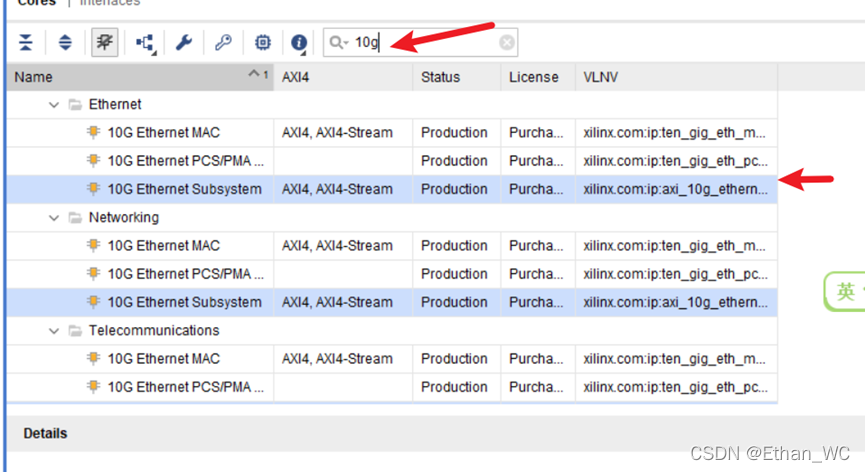

Enternet/ 10G Ethernet Subsystem: 把mac和pcs pma合成一个的ip.

============= -

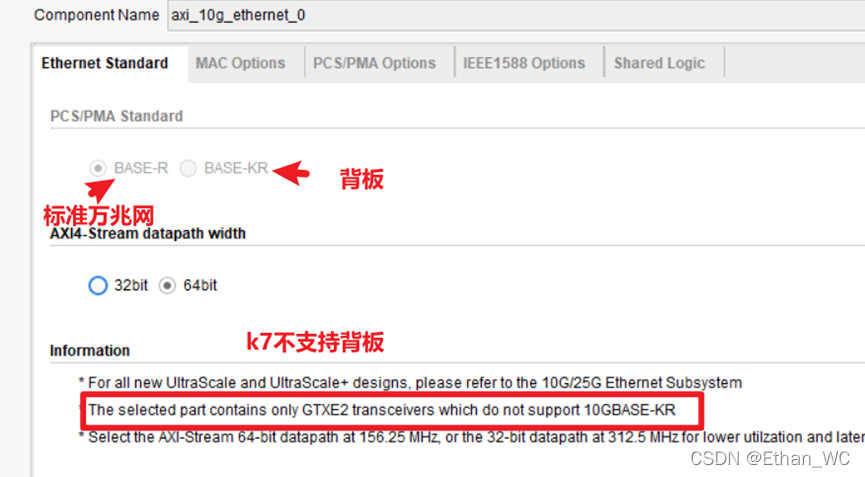

Base-R是标准的以太网,BASE-KR是用于背板的通信

============= -

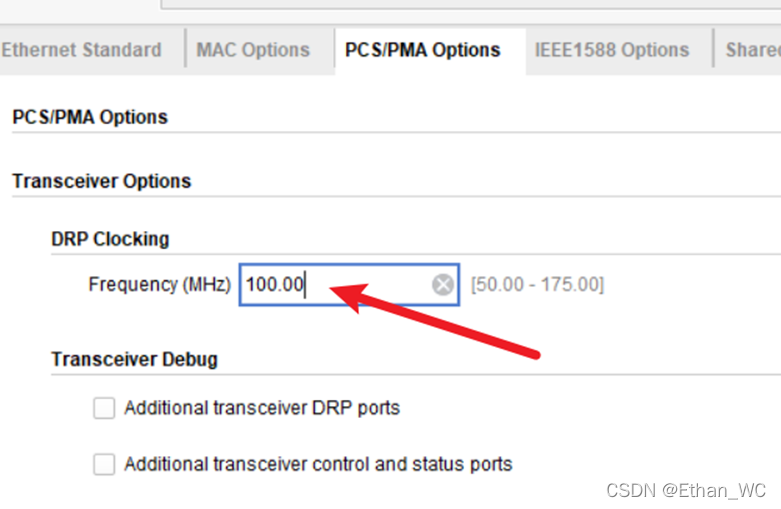

高速接口对复位比较敏感,必须在复位完成之后才能进行Link,或者说在某些情况下需要进行relink的时候,需要去复位,

这个DBR clocking还是挺重要的,是用来产生复位的信号的。

有的客户DRP CLKing设置的是100M,但最后给的是30M,导致高速接口有时能link上,有时候又link不上了。

改过来就好了,很大可能性是它初始化的时候它复位时间不够所导致的。

-

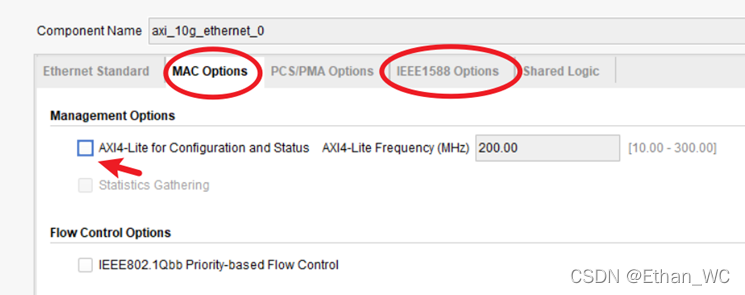

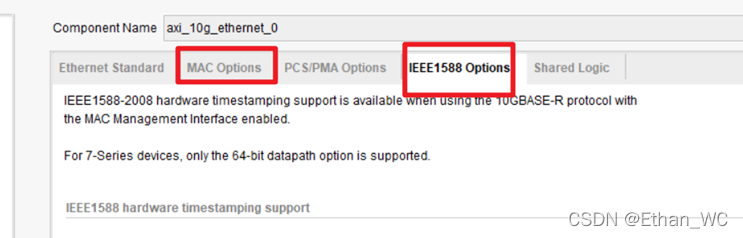

希望x86计算机计时和pcie板卡计时同步,可以在IEEE1588 Options配合MAC Options中打开AXI-Lite去配置MAC层的寄存器。我们这里没用,AXI-Lite没有打开。

============= -

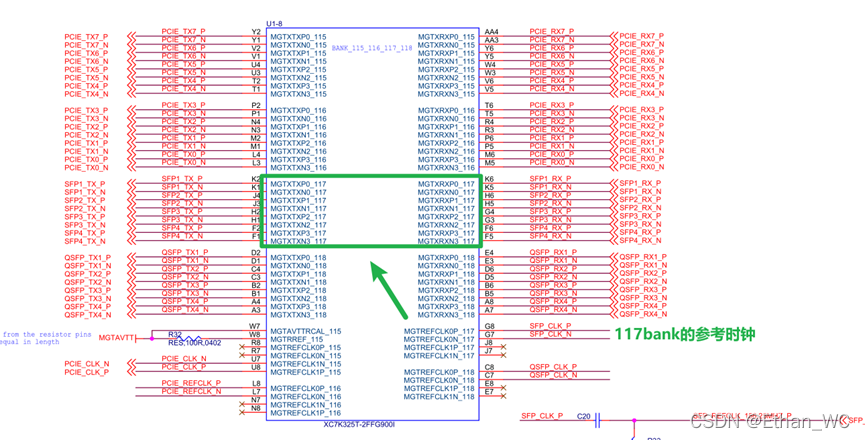

117bank的高速收发器都是用的参考时钟sfp_clk_p

拓展:你这个117bank的参考时钟能不能给其他bank做参考时钟呢?

可以,但是不能跨两个。比如117可以给116,115,118,119用。

这些115,116,117,118都是一个quad。

============= -

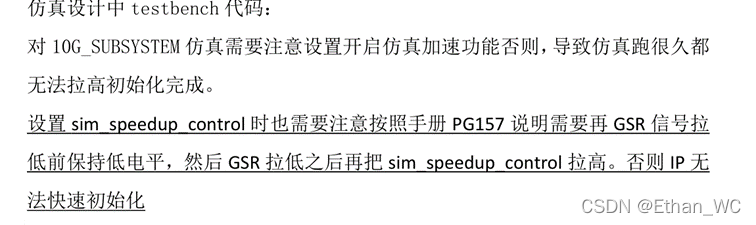

仿真注意事项

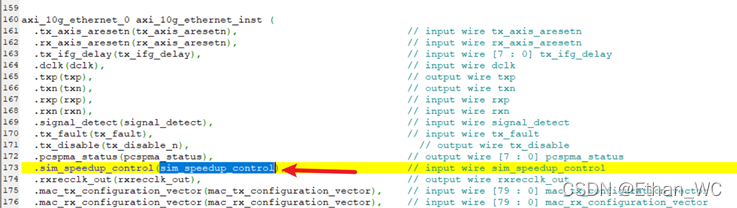

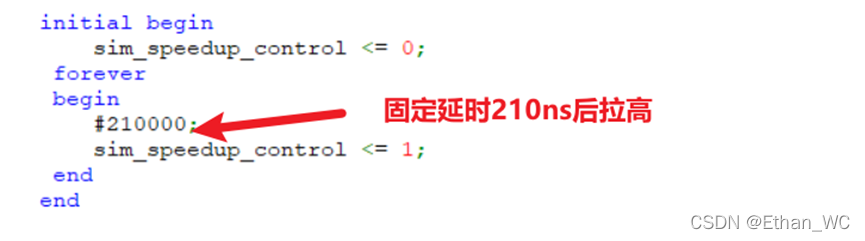

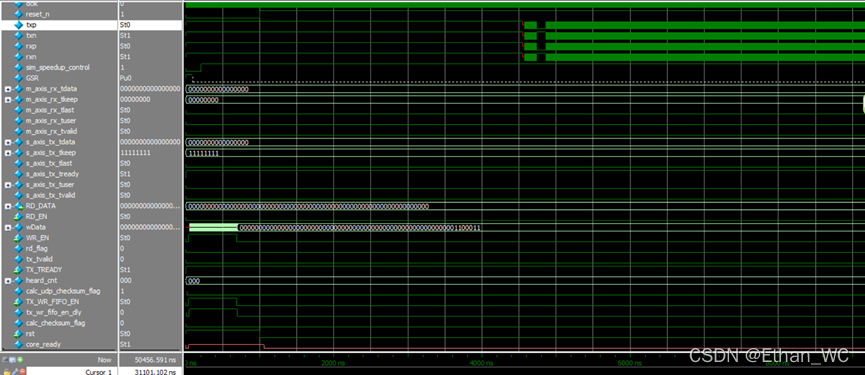

sim_speedup_control信号并不是直接拉高,而是有个拉低再拉高的过程。且必须要等到GSR拉低之后再把sim_speedup_control信号拉高。

GSR信号一般需要有几百个ns,我们直接固定延时200个ns就ok了。

============= -

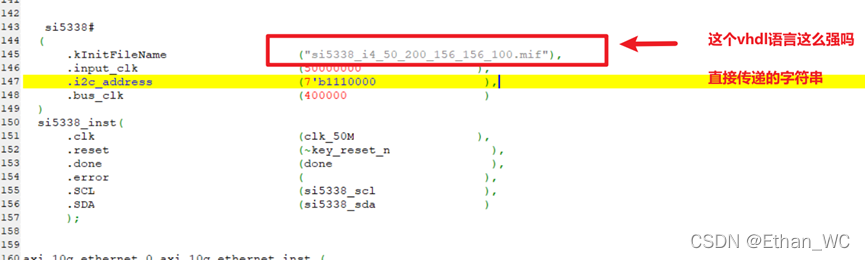

VHDL直接传递字符串!!!

============= -

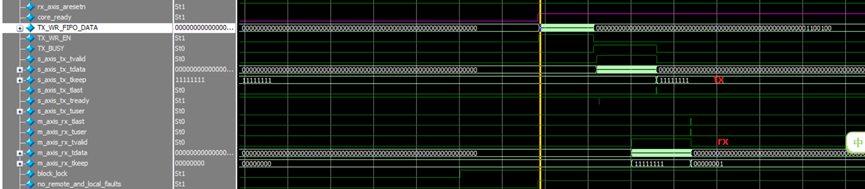

仿真记录

大约30us后core_ready才会拉高,要耐心等待。即使core_ready没有拉高,差分线上就已经有数据产生了,这时候axi-stream还没有给它发数据。网上查了说是一开始有IDLE的数据包,也会传过去。

============= -

说明

10G Ethernet Subsystem ipcore 使用起来很简单,只需要控制AXI-stream的接口即可。

8941

8941

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?