主要为PG195的翻译中关于应用部分。

IP应用

Clocking and Resets

时钟

axi_aclk 输出是用于所有 AXI 接口的时钟,应该驱动所有对应的 AXI Interconnect 的 aclk 信号。axi_aclk 不是一个自由运行的时钟。这是一个派生时钟,在 axi_aresetn 信号解除断言后才会变为有效。 注意:axi_aclk 输出不应该用作设计中的系统时钟。axi_aclk 不是一个自由运行的时钟输出。正如注意中所述,axi_aclk 可能并不始终存在。

复位

对于 PCIe 中的 AXI Bridge 模式下的 DMA/ Bridge 子系统,存在一个可选的 dma_bridge_resetn 输入引脚,允许您重置所有内部的 Bridge 引擎和寄存器,以及由 axi_aresetn 引脚驱动的所有 AXI 外设。当设置了以下参数时,在初始链接操作期间不需要断言 dma_bridge_resetn,因为 IP 会自动执行。在断言此引脚之前,必须终止所有事务。在断言之后,该引脚必须保持断言状态至少等于完成超时值的持续时间(通常为 50 毫秒),以清除可能当前在数据路径中排队的任何待处理传输。要设置此参数,请在 Tcl 命令行中键入以下命令:

set_property -dict [list CONFIG.soft_reset_en {true}] [get_ips <ip_name>]

!!!注:没有讲XDMA的复位要求,建议也以50ms为最小复位单位,且此复位解除之后,时钟才会出现,只可以作为异步复位。

Tandem Configuration

串列配置(Tandem)在Kintex-7互联TRD中的实现_xinxulsq的博客-CSDN博客

PCI Express®规范要求PCIe®链路在电源稳定后120毫秒内做好连接准备。由于可用编程比特流的大小和配置速率,对采用闪存存储器配置的大型FPGA而言要想满足这个要求的确是一个挑战。赛灵思的串列配置法(Tandem Configuration)是缩短FPGA配置时间以满足120毫秒PCIe链接时间要求的一种现实可行的方法。

当使用Tandem PROM时基本比特流大小以及初始配置时间可减少85%以上,而使用Tandem PCIe时可减少80%以上。

此处不做详述,一般在X86机箱上或一些特殊场景才会有此需求,在封闭的小系统,可以通过延迟PCIe扫描时间进行规避。

设计的流程

本节描述了如何定制和生成子系统,对子系统进行约束,并针对此IP子系统特定的仿真、综合和实现步骤进行说明。有关标准Vivado®设计流程和IP集成器的更详细信息,请参阅以下Vivado Design Suite用户指南:

- Vivado Design Suite用户指南:使用IP Integrator设计IP子系统 (UG994)

- Vivado Design Suite用户指南:IP设计 (UG896)

- Vivado Design Suite用户指南:入门指南 (UG910)

- Vivado Design Suite用户指南:逻辑仿真 (UG900)

IP生成

本节包含有关如何使用Xilinx®工具在Vivado® Design Suite中定制和生成子系统的信息。

如果在Vivado IP集成器中进行子系统的定制和生成,请查阅Vivado Design Suite用户指南:使用IP Integrator设计IP子系统 (UG994)以获取详细信息。IP集成器可能会在验证或生成设计时自动计算某些配置值。要检查这些值是否发生了更改,请参阅本章节中参数的描述。要查看参数值,请在Tcl控制台中运行validate_bd_design命令。

可以通过以下步骤为与IP子系统相关的各种参数指定值,从而定制IP以在设计中使用:

有关详细信息,参阅Vivado Design Suite用户指南:

IP设计 (UG896)和Vivado Design Suite用户指南:入门指南 (UG910)。

这一块为IP的例化,比较简单,暂时也不做描述。

约束

在Vivado® Design Suite中对子系统进行约束的内容。

所需的约束

用于PCI Express®的DMA/Bridge子系统需要在Xilinx Design Constraints(XDC)文件中指定定时和其他物理实现约束,以满足PCI Express的指定性能要求。生成的XDC中的引脚分配和层次结构名称与提供的示例设计相对应。

重要提示!如果未使用示例设计顶层文件,请将IBUFDS_GTE3(用于UltraScale+ IBUFDS_GTE4)实例用于参考时钟,IBUF实例用于sys_rst,并将与它们关联的位置和时序约束复制到您的本地设计顶层。

为了实现一致的实现结果,当通过Xilinx工具运行设计时,必须使用包含这些原始、未修改约束的XDC。有关XDC或特定约束的定义和使用的其他详细信息,请参阅Vivado Design Suite用户指南:使用约束(UG903)。

与IP解决方案一起提供的约束已在硬件中进行了测试,并提供了一致的结果。可以修改约束,但只有在充分理解每个约束的影响的情况下才能进行修改。另外,不为偏离提供的约束的设计提供支持。

设备、封装和速度等级选择 XDC的设备选择部分通知实现工具针对设计的哪个芯片、封装和速度等级进行目标设置。

重要提示!由于Gen2和Gen3用于PCIe核心是为特定的芯片和封装组合而设计的,因此不应修改此部分。

设备选择部分始终包含一个芯片选择行,但也可以包含特定于芯片或封装的选项。以下是一个示例的芯片选择行:

CONFIG PART = XCKU040-ffva1156-3-e-es1

重新定位IP核心

默认情况下,IP核级约束将块RAM、收发器和PCIe块锁定在建议的位置。要重新定位这些块,必须在XDC约束文件中覆盖这些块的约束。操作如下:

- 、从核级XDC约束文件中复制需要覆盖的块的约束。

- 、将约束放置在用户XDC约束文件中。

- 、使用新的位置更新约束。

用户XDC约束通常针对设计的顶层范围;因此,在复制和粘贴之后,确保约束引用的单元仍然有效。通常,您需要使用完整的层次结构名称更新模块路径。

注意:如果有需要交换的位置(即,新位置当前被另一个模块占用),有两种方法可以实现。

- 如果有临时位置可用,请首先将第一个模块移出新的临时位置。然后,将第二个模块移至第一个模块占用的位置。接下来,将第一个模块移至第二个模块的位置。这些步骤可以在XDC约束文件中完成。

- 如果没有其他可用作临时位置的位置,可以在将第二个模块重新定位到此位置之前,从Tcl命令窗口中使用reset_property命令对第一个模块进行复位。reset_property命令不能在XDC约束文件中执行,必须从Tcl命令文件中调用或直接键入到Tcl控制台中。

仿真

本部分包含有关在Vivado® Design Suite中进行IP仿真的信息。

有关Vivado®仿真组件的全面信息,以及使用支持的第三方工具的信息,请参阅Vivado Design Suite用户指南:逻辑仿真(UG900)。

Basic Simulation

可以生成和仿真AXI-MM和AXI-ST选项的仿真模型。这些是非常基本的仿真模型选项,您可以在其上开发复杂的设计。

AXI-MM模式

AXI4内存映射(AXI-MM)模式的示例设计在用户端具有4KB块RAM,因此可以将数据写入块RAM并从块RAM读取到主机。首先启动H2C传输,DMA从主机内存读取数据并写入块RAM。然后,启动C2H传输,DMA从块RAM读取数据并写入主机内存。原始数据与C2H写入数据进行比较。 H2C和C2H都使用一个描述符进行设置,总传输大小为64字节。

AXI-ST模式

AXI4-Stream(AXI_ST)模式的示例设计是一个回环设计。在用户端,H2C端口被回环到C2H端口。首先启动C2H传输,C2H DMA引擎在用户端等待数据。然后,启动H2C传输,DMA引擎从主机内存读取数据并写入用户端。由于这是一个回环设计,来自H2C的设计数据被导向C2H,并最终到达主机目标地址。 H2C和C2H都使用一个描述符进行设置,总传输大小为64字节。

Descriptor Bypass

仅针对通道0提供了描述符旁路模式的仿真模型。此设计可以扩展以支持其他通道。

PIPE Mode Simulation

DMA/Bridge子系统支持PIPE模式仿真,其中核心的PIPE接口与链路伙伴的PIPE接口相连接。这种模式可以增加仿真速度。

在定制IP对话框的基本页面上使用"启用PIPE模式仿真"选项,在当前Vivado® Design Suite解决方案示例设计中启用PIPE模式仿真,可以选择Endpoint模式或Root Port模式。外部PIPE接口信号在核心边界处生成,用于访问外部设备。启用此功能还提供了使用第三方PCI Express VIPs/BFMs的必要接口,以替代示例设计提供的Root Port模型。另请参阅"Gen3 x8和Gen2 x8配置中使用集成端点PCI Express块的PIPE模式仿真"应用笔记(XAPP1184)。

下面的表格描述了核心顶层的PIPE总线信号及其在EP核心(pcie_top)中的对应映射。

重要提示! xil_sig2pipe.v文件位于仿真目录中,并且该文件替换了phy_sig_gen.v。BFM/VIP应该与board.v中的xil_sig2pipe实例进行接口连接。

当VHDL是所选目标语言时,不支持该核心的PIPE模式仿真。

Table 131: Common In/Out Commands and Endpoint PIPE Signals Mappings

| In Commands | Endpoint PIPE | Out Commands | Signals Mapping Endpoint PIPE |

| common_commands_in[25:0] | not used | common_commands_out[0] | pipe_clk1 |

| common_commands_out[2:1] | pipe_tx_rate_gt2 | ||

| common_commands_out[3] | pipe_tx_rcvr_det_gt | ||

| common_commands_out[6:4] | pipe_tx_margin_gt | ||

| common_commands_out[7] | pipe_tx_swing_gt | ||

| common_commands_out[8] | pipe_tx_reset_gt | ||

| common_commands_out[9] | pipe_tx_deemph_gt | ||

| common_commands_out[16:10] | not used3 |

注:

- 、pipe_clk是基于核心配置的输出时钟。对于Gen1速率,pipe_clk为125 MHz。对于Gen2和Gen3,pipe_clk为250 MHz。

- 、pipe_tx_rate_gt指示PIPE速率(2’b00-Gen1,2’b01-Gen2和2’b10-Gen3)。

- 、该端口的功能已被弃用,可以不连接。

Table 132: Input/Output Bus with Endpoint PIPE Signals Mapping

| Input Bus | Endpoint PIPE | Output Bus | Endpoint PIPE |

| pipe_rx_0_sigs[31:0] | pipe_rx0_data_gt | pipe_tx_0_sigs[31: 0] | pipe_tx0_data_gt |

| pipe_rx_0_sigs[33:32] | pipe_rx0_char_is_k_gt | pipe_tx_0_sigs[33:32] | pipe_tx0_char_is_k_gt |

| pipe_rx_0_sigs[34] | pipe_rx0_elec_idle_gt | pipe_tx_0_sigs[34] | pipe_tx0_elec_idle_gt |

| pipe_rx_0_sigs[35] | pipe_rx0_data_valid_gt | pipe_tx_0_sigs[35] | pipe_tx0_data_valid_gt |

| pipe_rx_0_sigs[36] | pipe_rx0_start_block_gt | pipe_tx_0_sigs[36] | pipe_tx0_start_block_gt |

| pipe_rx_0_sigs[38:37] | pipe_rx0_syncheader_gt | pipe_tx_0_sigs[38:37] | pipe_tx0_syncheader_gt |

| pipe_rx_0_sigs[83:39] | not used | pipe_tx_0_sigs[39] | pipe_tx0_polarity_gt |

| pipe_tx_0_sigs[41:40] | pipe_tx0_powerdown_gt | ||

| pipe_tx_0_sigs[69:42] | not used1 |

注:

该端口的功能已被弃用,可以不连接。

Parameters for Custom PIPE Simulation

对于PIPE模拟,需要某些参数,并且可能需要手动设置。这些必需的参数在示例设计中提供。当您从Vivado IP目录生成示例设计时,所有必需的参数都会被设置,不需要额外的操作。然而,自定义设计将需要您将以下参数添加到设计测试台文件中。

defparam board.AXI_PCIE_EP.xdma_0_i.inst.pcie4_ip_i.inst.PL_SIM_FAST_LINK_TRAINING=2'h3;

localparam EXT_PIPE_SIM = "TRUE";

defparam board.AXI_PCIE_EP.xdma_0_i.inst.pcie4_ip_i.inst.EXT_PIPE_SIM = EXT_PIPE_SIM;

defparam board.RP.pcie_4_0_rport.pcie_4_0_int_inst.EXT_PIPE_SIM = "TRUE";

defparam board.RP.EXT_PIPE_SIM = "TRUE";

XDMA的仿真没有做过,后续做完XDMA的仿真,再补充数据,也许再开一篇讲XDMA的仿真比较合适。

这样对描述符的处理理解会更深刻!!!

综合和实现

example design

本章包含有关Vivado® Design Suite提供的示例设计的信息。

可用的示例设计如下:

- AXI4内存映射默认示例设计

- 带有PCIe到AXI4-Lite主控制器和PCIe到DMA旁路的AXI4内存映射示例设计

- 带有AXI4-Lite从接口的AXI4内存映射示例设计

- AXI4流式示例设计

- 带有描述符旁路的AXI4内存映射示例设计

- Vivado IP Integrator-Based示例设计

- 用户中断请求(IRQ)示例设计

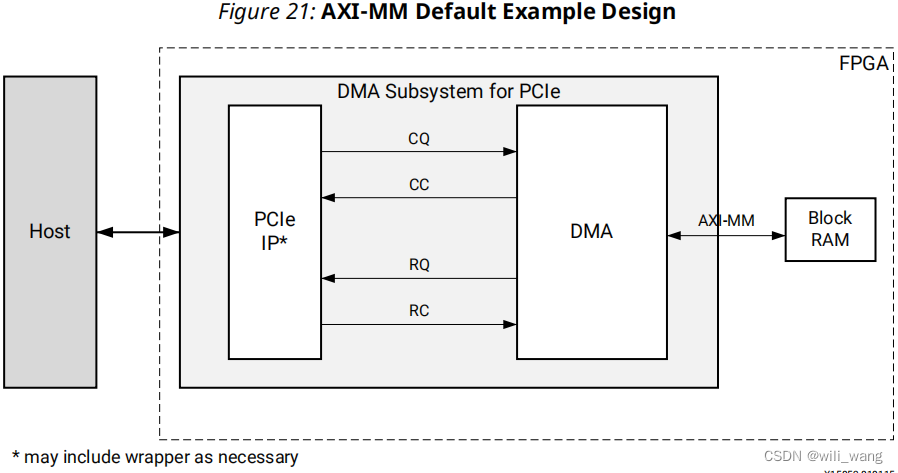

AXI4 Memory Mapped Default Example Design

下图显示了AXI4 Memory Mapped (AXI-MM) 接口作为默认设计。示例设计在用户设计中为AXI4 MM 接口提供了4KB的块RAM。对于H2C传输,DMA/Bridge子系统用于PCI Express®从主机读取数据并将其写入用户侧的块RAM中。对于C2H传输,DMA/Bridge子系统用于PCI Express®从块RAM中读取数据并写入主机内存。IP目录中的示例设计仅具有4 KB的块RAM;如果需要,可以重新生成更大块RAM大小的子系统。

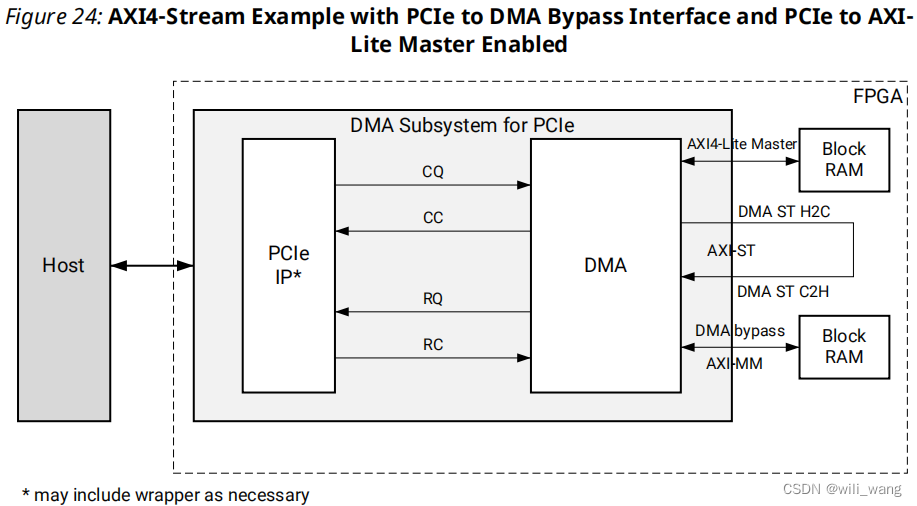

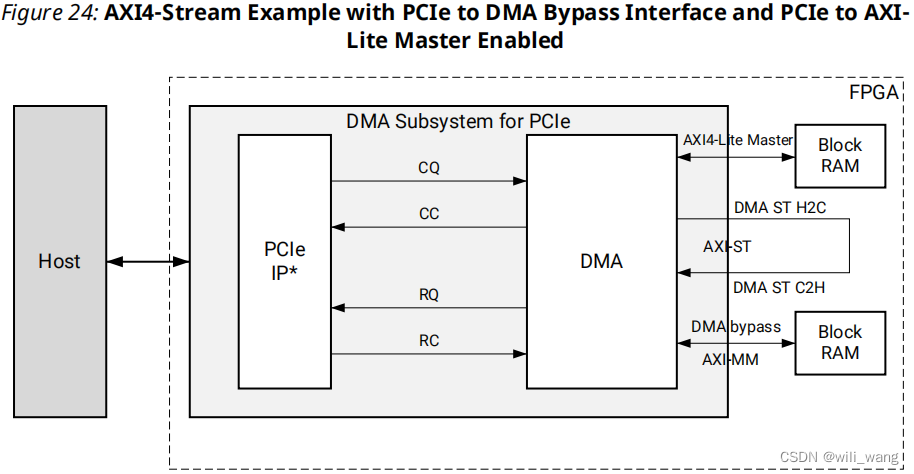

AXI4 Memory Mapped with PCIe to AXI4-Lite Master and PCIe to DMA Bypass Example Design

当启用AXI4-Stream接口时,每个H2C流通道都被回路连接到C2H通道。如下图所示,示例设计为AXI4流接口提供了一个环回设计。限制在于您需要选择相等数量的H2C和C2H通道以确保正常运行。此示例设计还展示了选择了PCIe到DMA bypass接口和PCIe到AXI-Lite Master接口。

DMA bypass接口和PCIe到AXI-Lite Master接口 这两个接口都是用于主机主动访问FPGA,不同点是AXI-Lite Master接口访问小的数据量;而DMA bypass接口可以访问大数据量。

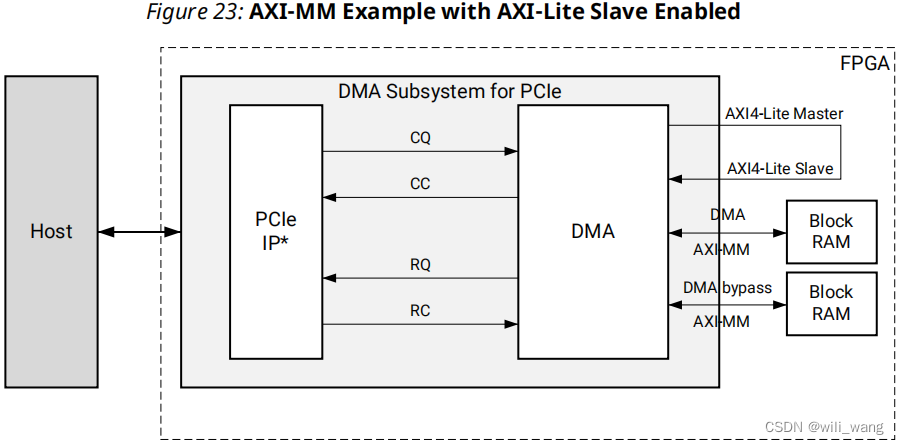

AXI4 Memory Mapped with AXI4-Lite Slave Interface Example Design

当启用PCIe®到AXI4-Lite主机和AXI4-Lite从机接口时,生成的示例设计(如下图所示)从AXI4-Lite主机到AXI4-Lite从机有一个环回。通常,用户逻辑可以使用AXI4-Lite从机接口读取/写入DMA/Bridge子系统的PCI Express®寄存器。通过这个示例设计,主机可以使用PCIe到AXI4-Lite主机(BAR0地址空间)读取/写入DMA/Bridge子系统的PCI Express®寄存器,这与使用PCIe到DMA(BAR1地址空间)相同。此示例设计还显示启用了PCIe到DMA旁路接口(BAR2)。

- AXI4-Lite Master去访问AXI4-Lite Slave(PCIe IP)接口设计比较巧妙;

- AXI-MM 可以直接访问Block ram,因为Block ram有地址;AXI-Steam只能自环;

- DMA Bypass访问大数据量

AXI4-Stream Example Design

当启用AXI4-Stream接口时,每个H2C流通道都被回环到C2H通道。如下图所示,示例设计为AXI4-Stream传输提供了一个回环设计。限制是需要选择相同数量的H2C和C2H通道以进行正确的操作。此示例设计还显示了启用了PCIe到DMA旁路接口和PCIe到AXI-Lite主机接口。

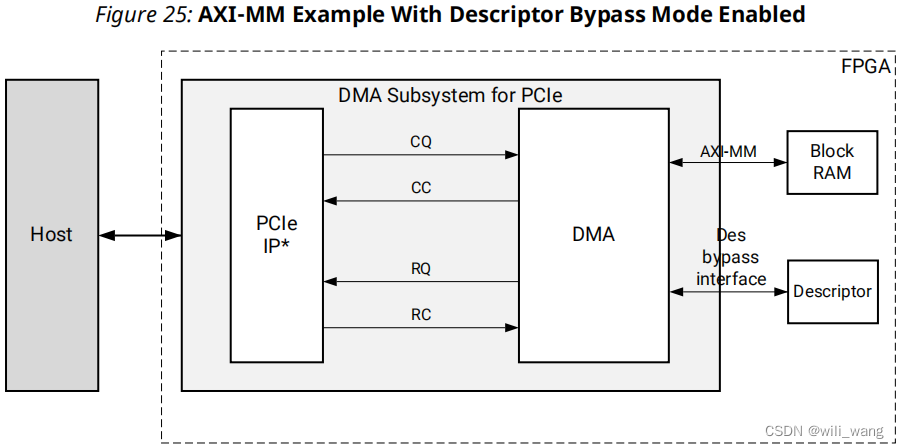

AXI4 Memory Mapped with Descriptor Bypass Example

当启用描述符旁路模式时,用户逻辑负责生成描述符并在描述符旁路接口中传输它们。如下图所示,AXI4内存映射设计启用了描述符旁路模式。您可以选择哪些通道将启用描述符旁路模式。当选择H2C的通道0和C2H的通道0用于描述符旁路模式时,生成的Vivado®示例设计将H2C0和C2H0的描述符旁路端口连接到仅生成一个64字节描述符的逻辑。用户负责为其他通道开发代码并扩展描述符本身。 下图显示了启用了描述符旁路模式的AXI-MM示例。

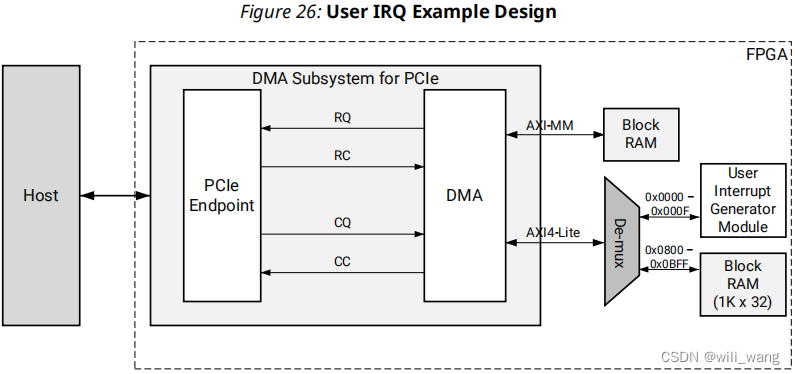

Vivado IP Integrator-Based Example Design User IRQ Example Design

用户IRQ示例设计使主机能够连接到AXI4-Lite主接口,同时还包括默认的DMA/Bridge子系统PCI Express®示例设计。在示例设计中,用户中断生成器模块和外部块RAM被集成在这个AXI4-Lite接口上。主机可以使用这个接口通过写入用户中断生成器模块的寄存器空间来生成用户IRQ,还可以读写外部1K块RAM。下图显示了示例设计。

可以使用以下Tcl命令生成示例设计。

set_property -dict [list CONFIG.usr_irq_exdes {true}] [get_ips <ip_name>]

寄存器描述在以下表格中找到。

Table 133: Example Design Registers

| Register | Register Name | Access Type | Description |

| 0x00 | Scratch Pad | RW | Scratch Pad |

| 0x04 | DMA BRAM Size | RO | User Memory Size connected to XDMA. |

| 0x08 | Interrupt Control Register | RW | Interrupt control register (write 1 to generate interrupt). |

| 0x0C | Interrupt Status Register | RO | Interrupt Status. |

注意:对于传统中断,应该在相应的中断位的中断控制寄存器(0x08)值在中断服务例程完成之后才能清除,因为主机可以使用这个值来确定中断来源。

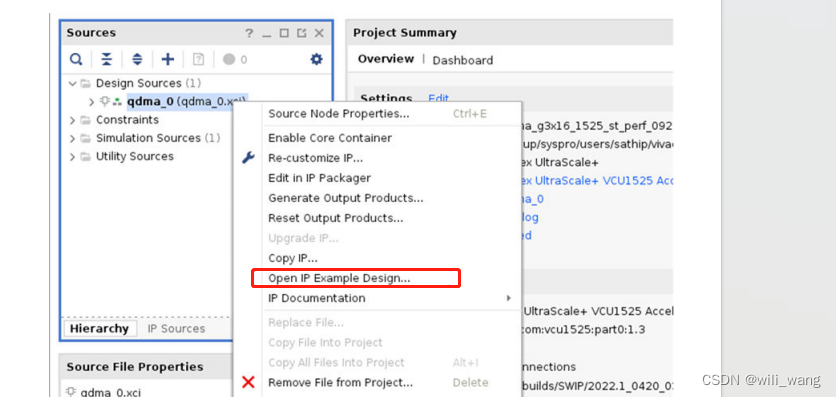

定制和生成示例设计

在“自定义 IP”对话框中,使用 IP 示例设计的默认参数值。在审查了 IP 参数后:

1、右键单击组件名称

2、Select Open IP Example Design.

This opens an example design in a separate Vivado Project.

后续仿真需要单独出一篇,好多事件可做,挖了一个又一个坑,无法填平了!!!

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?