学习在PS端配置以太网。本篇内容主要是vivado与SDK的使用步骤。

ZYNQ初体验千兆以太网的那些事儿(ps端)_zynq千兆网口实验-CSDN博客

vivado:

新建工程 --> 新建block design --> 选择zynq system,配置Ethernet、uart、SD卡。然后生成比特流

注意,这里不能只配置Ethernet,还要配置uart,不然在SDK新建模板的时候会报错。

生成HDL wrapper。然后export到SDK。

SDK:

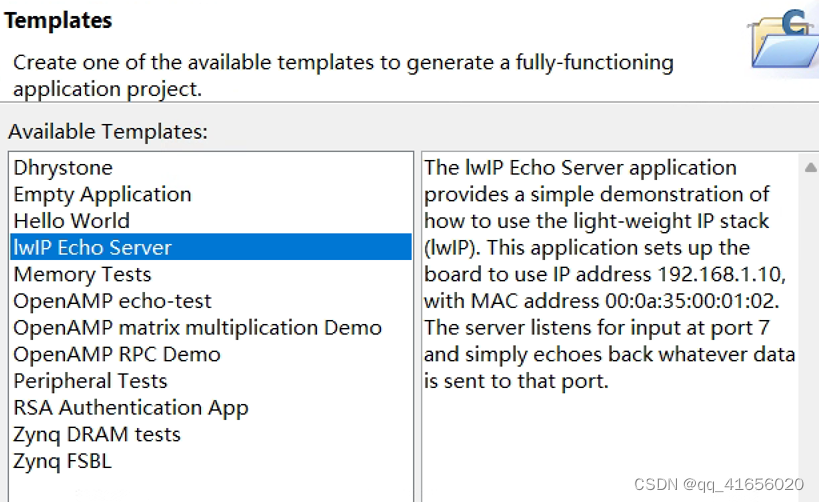

新建application,选择lwip模板。

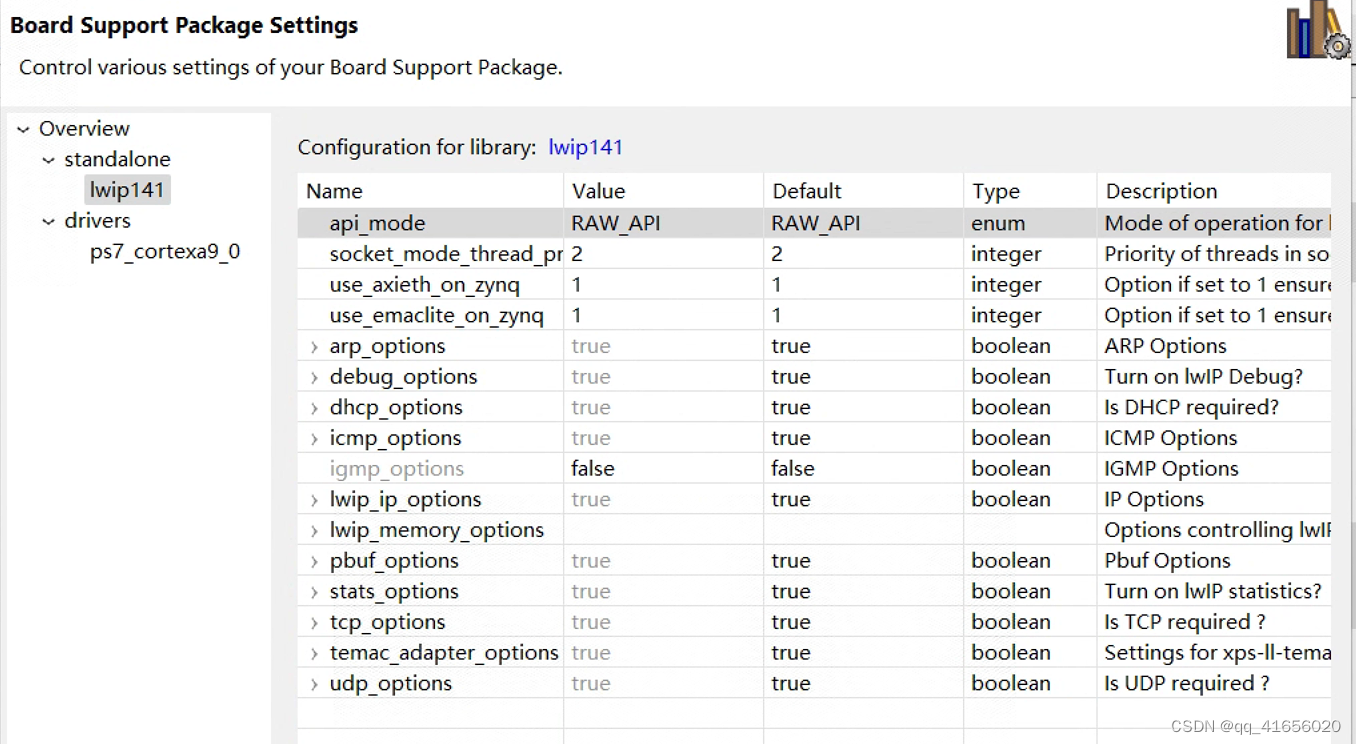

右键bsp配置以太网信息,这里没有修改任何信息。

然后main函数里就有了关于以太网配置的代码了。

那么现在来学习一下以太网相关的知识吧,不然代码看不懂。

fpga接口系列_基于zynq的以太网开发(pl到ps)_pl端采集的信息如何通过ps端以太网传输-CSDN博客

Zynq学习_____以太网三部曲(一)理论篇_zynq 以太网-CSDN博客

参考文档:zynq小系统板之嵌入式SDK开发指南

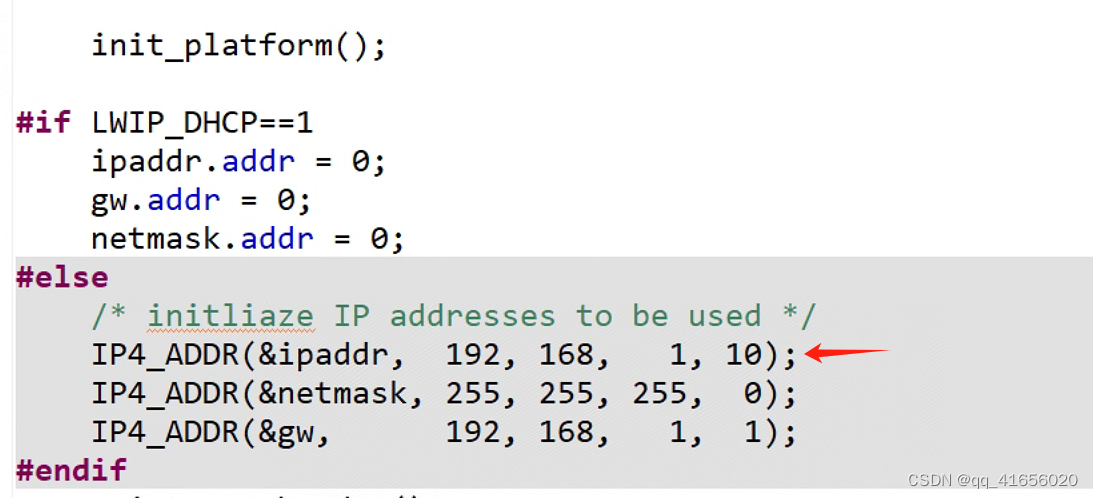

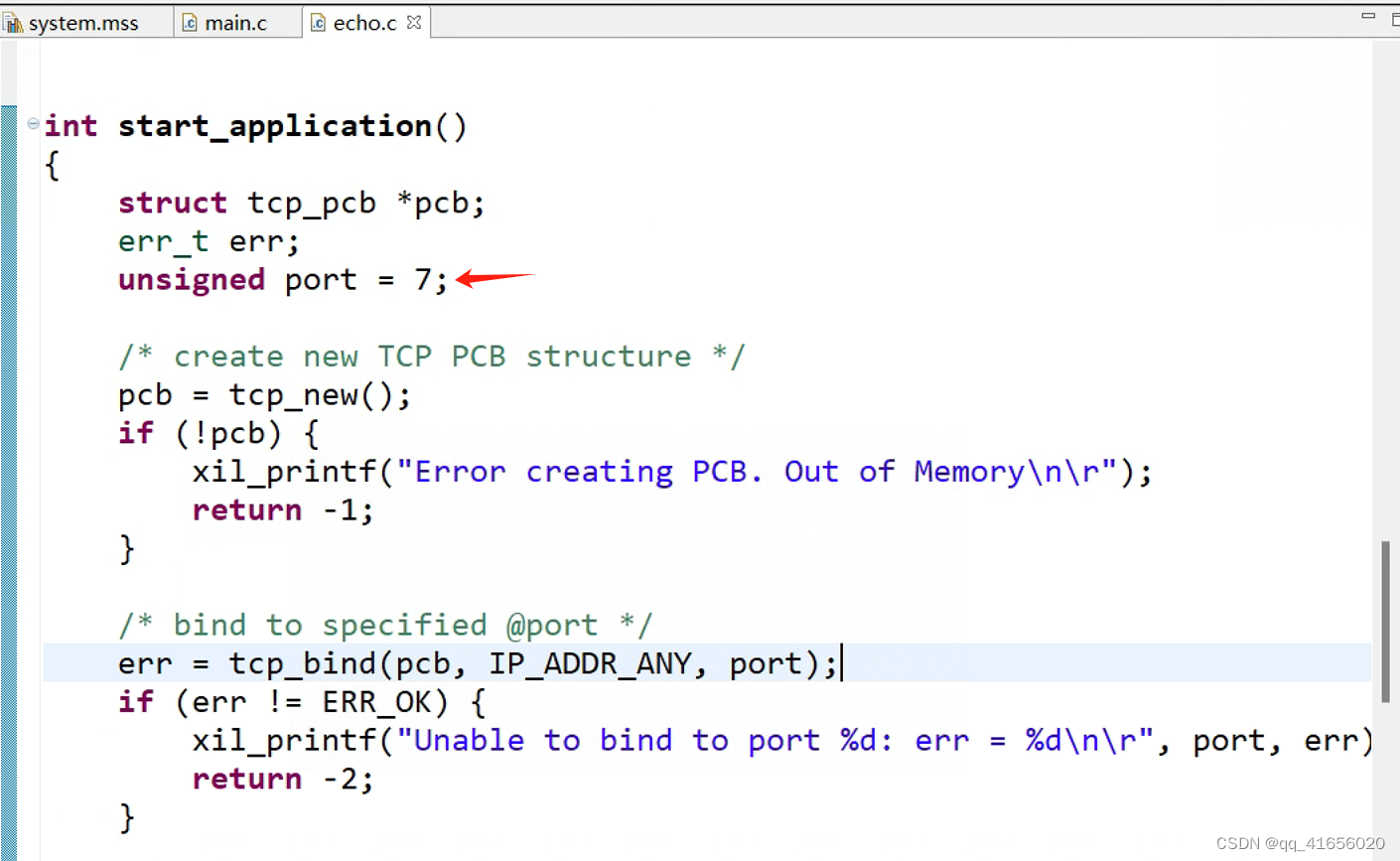

在创建工程选择模板时,右侧的界面已经说明MAC的地址为00:0a:35:00:01:02,静态IP地址为192.168.1.10,端口为port 7。在代码中的部分为:

echo.c代码:

#include <stdio.h>

#include <string.h>

#include "lwip/err.h"

#include "lwip/tcp.h"

#if defined (__arm__) || defined (__aarch64__)

#include "xil_printf.h"

#endif

int transfer_data() {

return 0;

}

void print_app_header()

{

xil_printf("\n\r\n\r-----lwIP TCP echo server ------\n\r");

xil_printf("TCP packets sent to port 6001 will be echoed back\n\r");

}

err_t recv_callback(void *arg, struct tcp_pcb *tpcb,

struct pbuf *p, err_t err)

{

/* do not read the packet if we are not in ESTABLISHED state */

if (!p) {

tcp_close(tpcb);

tcp_recv(tpcb, NULL);

return ERR_OK;

}

/* indicate that the packet has been received */

tcp_recved(tpcb, p->len);

/* echo back the payload */

/* in this case, we assume that the payload is < TCP_SND_BUF */

if (tcp_sndbuf(tpcb) > p->len) {

err = tcp_write(tpcb, p->payload, p->len, 1);

} else

xil_printf("no space in tcp_sndbuf\n\r");

/* free the received pbuf */

pbuf_free(p);

return ERR_OK;

}

err_t accept_callback(void *arg, struct tcp_pcb *newpcb, err_t err)

{

static int connection = 1;

/* set the receive callback for this connection */

tcp_recv(newpcb, recv_callback);

/* just use an integer number indicating the connection id as the

callback argument */

tcp_arg(newpcb, (void*)connection);

/* increment for subsequent accepted connections */

connection++;

return ERR_OK;

}

int start_application() //用户应用函数

{

struct tcp_pcb *pcb;

err_t err;

unsigned port = 7; // 端口设置为7

/* create new TCP PCB structure */

pcb = tcp_new();

if (!pcb) {

xil_printf("Error creating PCB. Out of Memory\n\r");

return -1;

}

/* bind to specified @port */

err = tcp_bind(pcb, IP_ADDR_ANY, port);

if (err != ERR_OK) {

xil_printf("Unable to bind to port %d: err = %d\n\r", port, err);

return -2;

}

/* we do not need any arguments to callback functions */

tcp_arg(pcb, NULL);

/* listen for connections */

pcb = tcp_listen(pcb);

if (!pcb) {

xil_printf("Out of memory while tcp_listen\n\r");

return -3;

}

/* specify callback to use for incoming connections */

tcp_accept(pcb, accept_callback);

xil_printf("TCP echo server started @ port %d\n\r", port);

return 0;

}

main.c代码:

#include <stdio.h>

#include "xparameters.h"

#include "netif/xadapter.h"

#include "platform.h"

#include "platform_config.h"

#if defined (__arm__) || defined(__aarch64__)

#include "xil_printf.h"

#endif

#include "lwip/tcp.h"

#include "xil_cache.h"

#if LWIP_DHCP==1

#include "lwip/dhcp.h"

#endif

/* defined by each RAW mode application */

void print_app_header();

int start_application();

int transfer_data();

void tcp_fasttmr(void);

void tcp_slowtmr(void);

/* missing declaration in lwIP */

void lwip_init();

#if LWIP_DHCP==1

extern volatile int dhcp_timoutcntr;

err_t dhcp_start(struct netif *netif);

#endif

extern volatile int TcpFastTmrFlag;

extern volatile int TcpSlowTmrFlag;

static struct netif server_netif;

struct netif *echo_netif;

void

print_ip(char *msg, struct ip_addr *ip)

{

print(msg);

xil_printf("%d.%d.%d.%d\n\r", ip4_addr1(ip), ip4_addr2(ip),

ip4_addr3(ip), ip4_addr4(ip));

}

void

print_ip_settings(struct ip_addr *ip, struct ip_addr *mask, struct ip_addr *gw)

{

print_ip("Board IP: ", ip);

print_ip("Netmask : ", mask);

print_ip("Gateway : ", gw);

}

#if defined (__arm__) || defined(__aarch64__)

#if XPAR_GIGE_PCS_PMA_SGMII_CORE_PRESENT == 1 || XPAR_GIGE_PCS_PMA_1000BASEX_CORE_PRESENT == 1

int ProgramSi5324(void);

int ProgramSfpPhy(void);

#endif

#endif

int main()

{

#if __aarch64__

Xil_DCacheDisable();

#endif

struct ip_addr ipaddr, netmask, gw;

/* the mac address of the board. this should be unique per board */

unsigned char mac_ethernet_address[] =

{ 0x00, 0x0a, 0x35, 0x00, 0x01, 0x02 };

echo_netif = &server_netif;

#if defined (__arm__) || defined(__aarch64__)

#if XPAR_GIGE_PCS_PMA_SGMII_CORE_PRESENT == 1 || XPAR_GIGE_PCS_PMA_1000BASEX_CORE_PRESENT == 1

ProgramSi5324();

ProgramSfpPhy();

#endif

#endif

init_platform();

#if LWIP_DHCP==1

ipaddr.addr = 0;

gw.addr = 0;

netmask.addr = 0;

#else

/* initliaze IP addresses to be used */

IP4_ADDR(&ipaddr, 192, 168, 1, 10);

IP4_ADDR(&netmask, 255, 255, 255, 0);

IP4_ADDR(&gw, 192, 168, 1, 1);

#endif

print_app_header();

lwip_init();

/* Add network interface to the netif_list, and set it as default */

if (!xemac_add(echo_netif, &ipaddr, &netmask,

&gw, mac_ethernet_address,

PLATFORM_EMAC_BASEADDR)) {

xil_printf("Error adding N/W interface\n\r");

return -1;

}

netif_set_default(echo_netif);

/* now enable interrupts */

platform_enable_interrupts();

/* specify that the network if is up */

netif_set_up(echo_netif);

#if (LWIP_DHCP==1)

/* Create a new DHCP client for this interface.

* Note: you must call dhcp_fine_tmr() and dhcp_coarse_tmr() at

* the predefined regular intervals after starting the client.

*/

dhcp_start(echo_netif);

dhcp_timoutcntr = 24;

while(((echo_netif->ip_addr.addr) == 0) && (dhcp_timoutcntr > 0))

xemacif_input(echo_netif);

if (dhcp_timoutcntr <= 0) {

if ((echo_netif->ip_addr.addr) == 0) {

xil_printf("DHCP Timeout\r\n");

xil_printf("Configuring default IP of 192.168.1.10\r\n");

IP4_ADDR(&(echo_netif->ip_addr), 192, 168, 1, 10);

IP4_ADDR(&(echo_netif->netmask), 255, 255, 255, 0);

IP4_ADDR(&(echo_netif->gw), 192, 168, 1, 1);

}

}

ipaddr.addr = echo_netif->ip_addr.addr;

gw.addr = echo_netif->gw.addr;

netmask.addr = echo_netif->netmask.addr;

#endif

print_ip_settings(&ipaddr, &netmask, &gw);

/* start the application (web server, rxtest, txtest, etc..) */

start_application();

/* receive and process packets */

while (1) {

if (TcpFastTmrFlag) {

tcp_fasttmr();

TcpFastTmrFlag = 0;

}

if (TcpSlowTmrFlag) {

tcp_slowtmr();

TcpSlowTmrFlag = 0;

}

xemacif_input(echo_netif);

transfer_data();

}

/* never reached */

cleanup_platform();

return 0;

}

本文介绍了如何在ZYNQ平台使用Vivado工具配置Ethernet接口,并结合SDK实现基于LWIP的TCP服务器,包括MAC地址、IP设置以及主函数和应用函数的详细代码示例。

本文介绍了如何在ZYNQ平台使用Vivado工具配置Ethernet接口,并结合SDK实现基于LWIP的TCP服务器,包括MAC地址、IP设置以及主函数和应用函数的详细代码示例。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?