一、Make的使用

- 选项

— -C dir 读入指定目录下的Makefile

— -f file 读入当前目录下的file文件作为Makefile

— -i 忽略所有的命令换行错误

— -I dir 指定被包含的Makefile所在目录

— -n 只打印要执行的命令,但不执行这些命令。

— -p 显示make变量数据库和隐含规则

— -s 在执行命令时不显示命令

— -w 如果make在执行过程中改变目录,打印当前目录名。

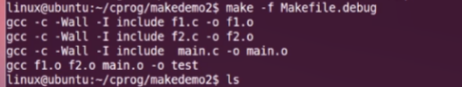

- 普通文件当Makefile文件按使用:make -f Makefile.debug -------- 把Makefile.debug当成Makefile文件使用

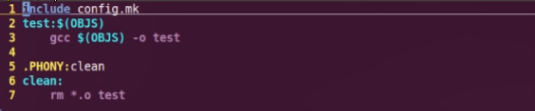

- 两个makefile文件一起编译的话,也就是说需要将一些其他的头文件以及配置文件一起编译到该工程中,需要在要编译的makefile文件中include(包含)该配置文件。 ------ 举例:在学习u-boot时很重要的文件 config.mk文件

二、Makefile的隐含规则

- 第一个隐含规则

编辑C程序的隐含规则

“<n>.o”的目标的依赖目标会自动推导出“<n>.c”,并且其生成命令是“$(CC) -c $(CPPFLAGS) $(CFLAGS)”

利用隐含规则简化:

- 第二个隐含规则:

链接Object文件的隐含规则

“<n>”目标依赖于“<n>.o”,通过运行C的编译器来运行链接程序生成(一般是“ld”),其生成命令是:“$(CC) $(LDFLAGS) <n>.o

" $(LOADLIBES) $(LDLIBS)"。这个规则对于只有一个源文件的源文件的工程有效,同时也对多个Object文件(由不同的源文件生成)的也有效。例如如下:

规则:

x:x.o y.o z.o

并且“x.c” 、“y.c”和“z.c”都存在时,隐含规则将执行如下命令。

cc -c x.c -o x.o

cc -c y.c -o y.o

cc -c z.c -o z.o

cc -c x.o y.o z.o -o x

如果没有一个源文件(如上例中的x.c)和你的目标名字(如上例中的x)相关联,那么,你最好写出来自己的生成规则,不然,隐含规则会报错的

- 充分使用Makefile后最终得到的Makefile:

四、VPATH 的用法

1、Makefile的VPATH

- VPATH :虚路径

— 在一些大的工程中,有大量的源文件,我们通常的做法时把这许多的源文件分类,并存放在不同的目录中。所有,当make需要区找寻文件的依赖关系时,你可以在文件前加上路径,但最好的方法是把一个路径告诉make,让make在自动去找。

— Makefile文件中的特殊变量“VPATH”就是完成这个功能的,如果没有指明这个变量,make只会在当前的目录中寻找依赖文件和目标文件。如果定义了这个变量,那么make就会在当前目录寻找不到的情况下,到所指定的目录中区找寻文件了。

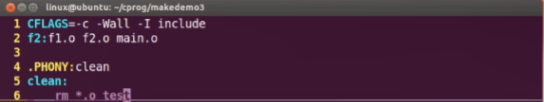

- 未简化的make:

- 简化后的make:

其中:rm test 修改为 rm f1 。

五、嵌套的Makefile

- 案例

— — 我们注意到有一句@echo $(SUBDIRS)

— — @(RM)并不是我们自己定义的变量,那它是从哪里来的呢?

— — make -C $@

— — export CC OBJS BIN OBJS_DIR BIN_DIRD

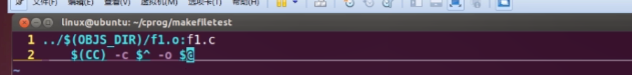

- 文件夹f1 中的Makefile 内容

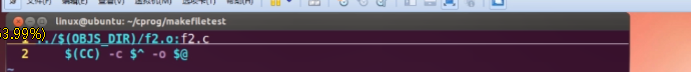

- 文件夹f2 中的Makefile 内容

- 当前目录中的Makefile嵌套运行其他子目录下的Makefile文件。

3224

3224

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?