PCB设计中的参考层是确保信号完整性和电磁兼容性的核心。它为高速信号提供低阻抗返回路径,减少环路电感和电磁辐射(EMI);通过电源-地平面耦合稳定电源阻抗,降低噪声;控制传输线特性阻抗(如50Ω/100Ω),避免信号反射。参考层还能屏蔽外部干扰,抑制串扰。若设计不当(如跨分割或参考层不完整),将导致阻抗突变、信号失真和EMC失效。合理选择地平面作为高速信号参考层,并优化叠层结构,是提升PCB性能的关键。

一、为什么需要选择参考层?

1. 参考层的物理作用

-

信号返回路径的载体:

高速信号的电流必须形成闭合回路,参考层为返回电流提供低阻抗路径。-

电流环路面积最小化:返回电流在参考层表面以镜像方式流动,减小环路电感(L∝环路面积),降低辐射和串扰。

-

-

控制传输线特性阻抗:

参考层与信号层的相对位置、间距和材料参数共同决定了传输线的特性阻抗(如50Ω或100Ω差分)。-

微带线(外层信号):信号层与单一参考层(GND或Power)构成传输线。

-

带状线(内层信号):信号层夹在两个参考层之间,阻抗更稳定,抗干扰能力更强。

-

2. 不选择参考层的后果

-

阻抗失配:返回路径不明确导致特性阻抗偏离设计值,引发信号反射(回波损耗)。

-

EMI恶化:电流环路面积增大,辐射强度随�2×面积f2×面积升高,可能超出FCC/CE标准。

-

电源噪声耦合:若参考层为噪声较大的电源平面,高频信号可能被调制,导致误码率上升。

二、参考层选择的核心原则

1. 优先级顺序

-

原则1:高速信号(>50MHz)必须参考完整的地平面(GND)。

-

原则2:低速信号可参考电源平面(Power),但需确保电源噪声足够低。

-

原则3:避免信号跨越参考层分割区,否则需通过电容或过孔桥接。

2. 四层板的典型叠层与参考层选择

四层板常见两种叠层结构,对应不同的参考层策略:

方案A:Top → GND → Power → Bottom

-

适用场景:高速数字电路(如CPU、DDR)、多电压系统。

-

参考层选择:

-

Top层信号:参考第2层(GND平面),阻抗由Top-GND间距、线宽、介质决定。

-

Bottom层信号:参考第3层(Power平面),需密集去耦电容稳定电源噪声。

-

-

优点:GND平面完整,适合高速信号;电源与地相邻,形成天然去耦电容。

-

缺点:电源平面可能因多电压需求被分割,需谨慎处理跨分割信号。

方案B:GND → Signal → Signal → Power

-

适用场景:高密度布线(如FPGA)、射频/高频电路。

-

参考层选择:

-

内层信号(第2、3层):上下分别参考GND和Power平面(带状线结构),阻抗由上下间距共同决定。

-

-

优点:双参考层抑制EMI;适合差分信号和敏感模拟电路。

-

缺点:叠层对称性要求高,加工成本略高;电源平面需严格去耦。

三、阻抗计算与参考层的参数关系

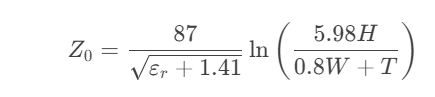

1. 微带线(外层信号)阻抗公式

-

关键参数:

-

H:信号层到参考层的介质厚度(如5mil)。

-

W:走线宽度(如6mil)。

-

T:铜厚(1oz=1.4mil)。

-

εr:介质材料介电常数(FR4约为4.3)。

-

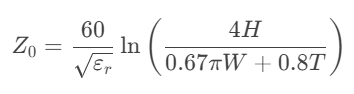

2. 带状线(内层信号)阻抗公式

-

关键参数:

-

H:上下参考层总间距(如GND到Power层20mil)。

-

3. 参考层对阻抗的影响

-

介质厚度(H):

H增加 → 阻抗升高(微带线更敏感)。-

示例:FR4材料,线宽6mil,H从5mil增至6mil,阻抗从53Ω升至58Ω。

-

-

参考层完整性:

若参考层被分割,实际介质厚度等效增大,导致阻抗跳变(需通过仿真验证)。

四、四层板参考层设计实践步骤

1. 叠层规划

-

目标:确保高速信号层紧邻地平面。

-

实例:

-

对于方案A(Top-GND-Power-Bottom),将时钟线、差分对布在Top层,参考GND。

-

对于方案B(GND-Signal-Signal-Power),将射频信号布在内层,双参考层抑制辐射。

-

2. 参考层完整性检查

-

禁止分割区域:高速信号正下方禁止参考层分割(如DDR数据线下方GND必须完整)。

-

跨分割修复:

-

添加缝合电容(0.1μF)连接分割区两侧的参考层。

-

使用接地过孔阵列“缝合”地平面,提供高频返回路径。

-

3. 阻抗计算与仿真

-

工具选择:

-

Polar SI9000、Altium阻抗计算器、ANSYS HFSS。

-

-

流程示例:

-

输入叠层参数(介质厚度、铜厚、介电常数)。

-

根据目标阻抗(如50Ω单端、100Ω差分)反推线宽/间距。

-

通过TDR仿真验证实际阻抗连续性(允许±10%误差)。

-

4. 去耦电容布局

-

电源平面参考的补偿:

-

在电源平面边缘和关键器件周围布置0.1μF+10μF电容组合。

-

示例:CPU四周每5mm放置一颗0.1μF电容,降低电源阻抗。

-

五、常见问题与解决方法

1. 问题:阻抗实测值偏离设计

-

原因:

-

参考层介质厚度加工误差(PCB厂公差±10%)。

-

参考层被意外分割或存在空洞。

-

-

解决:

-

与PCB厂确认叠层参数,预留阻抗测试条。

-

使用仿真工具反标实际参数,迭代设计。

-

2. 问题:高速信号EMI超标

-

原因:

-

信号参考层切换(如Top层信号下方GND不连续)。

-

电源平面噪声耦合到参考层。

-

-

解决:

-

优化叠层,确保高速信号参考完整地平面。

-

在电源平面添加高频去耦电容(如1nF 0402封装)。

-

3. 问题:多电源域导致参考层分割

-

原因:

-

需要3.3V、1.8V等多电压,电源平面被迫分割。

-

-

解决:

-

分割区边缘布置缝合电容(0.1μF),跨区信号线就近连接电容。

-

重新布线,避免高速信号跨越分割区。

-

六、总结

参考层选择的核心逻辑:

-

高速信号 → 紧邻完整地平面(最低阻抗路径)。

-

电源参考 → 仅限低频信号,且需去耦优化。

-

避免跨分割 → 通过电容或过孔强制修复路径。

四层板设计口诀:

“高速靠地,电源慎用;跨分割要电容,去耦密度是关键。”

886

886

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?